# MPC8240 Integrated Processor User's Manual

MPC8240UM/D Rev 1, 1/2001

#### How to Reach Us:

#### Home Page:

www.freescale.com

#### E-mail:

support@freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French)

#### Japan:

support@freescale.com

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd.

Technical Information Center

2 Dai King Street

Tai Po Industrial Estate

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or 303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or quarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

| Overview                                          | 1   |

|---------------------------------------------------|-----|

| Signal Descriptions and Clocking                  | 2   |

| Address Maps                                      | 3   |

| Configuration Registers                           | 4   |

| PowerPC Processor Core                            | 5   |

| MPC8240 Memory Interface                          | 6   |

| PCI Bus Interface                                 | 7   |

| DMA Controller                                    | 8   |

| Message Unit (I <sub>2</sub> O)                   | 9   |

| I <sup>2</sup> C Interface                        | 10  |

| Embedded Programmable Interrupt Controller (EPIC) | 11  |

| Central Control Unit                              | 12  |

| Error Handling                                    | 13  |

| Power Management                                  | 14  |

| Debug Features                                    | 15  |

| Programmable I/O and Watchpoint                   | 16  |

| Address Map A                                     | А   |

| Bit and Byte Ordering                             | В   |

| Initialization Example                            | С   |

| PowerPC Instruction Set                           | D   |

| Processor Core Register Summary                   | Е   |

| Glossary of Terms and Abbreviations               | GLO |

| Index                                             | IND |

|                            | Freescale Semiconductor, Inc. Overview            |

|----------------------------|---------------------------------------------------|

| 2                          | Signal Descriptions and Clocking                  |

| 3                          | Address Maps                                      |

| 4                          | Configuration Registers                           |

| 5                          | PowerPC Processor Core                            |

| 6                          | MPC8240 Memory Interface                          |

| 7                          | PCI Bus Interface                                 |

| 8                          | DMA Controller                                    |

| 9                          | Message Unit (I <sub>2</sub> O)                   |

| 10<br>11<br>12<br>13<br>14 | I <sup>2</sup> C Interface                        |

| 11                         | Embedded Programmable Interrupt Controller (EPIC) |

| 12                         | Central Control Unit                              |

| 13                         | Error Handling                                    |

| 14                         | Power Management                                  |

|                            | Debug Features                                    |

| 16                         | Programmable I/O and Watchpoint                   |

| 15<br>16<br>A              | Address Map A                                     |

| В                          | Bit and Byte Ordering                             |

| С                          | Initialization Example                            |

| D                          | PowerPC Instruction Set                           |

| Е                          | Processor Core Register Summary                   |

| GLO                        | Glossary of Terms and Abbreviations               |

| IND                        | Index                                             |

### **CONTENTS**

| Paragraph | Title | Page   |

|-----------|-------|--------|

| Number    | Title | Number |

#### **About This Book**

#### Chapter 1 Overview

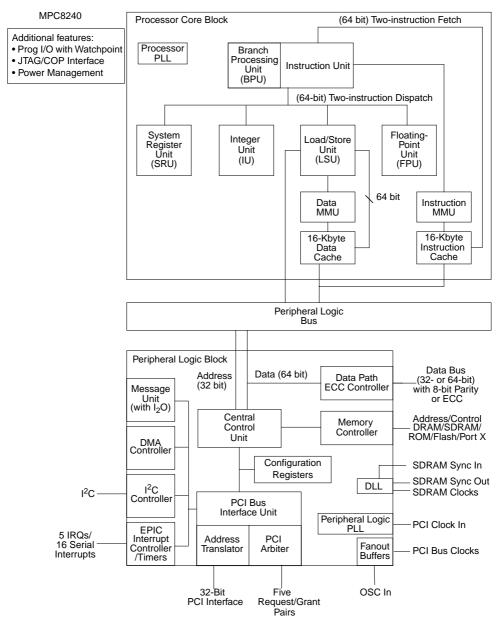

| 1.1     | MPC8240 Integrated Processor Overview 1-1                   |

|---------|-------------------------------------------------------------|

| 1.1.1   | MPC8240 Integrated Processor Features                       |

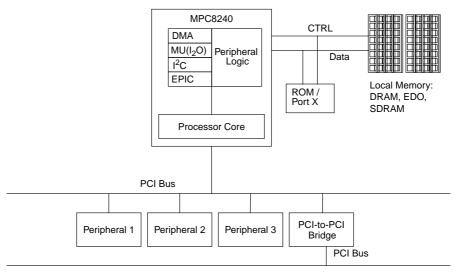

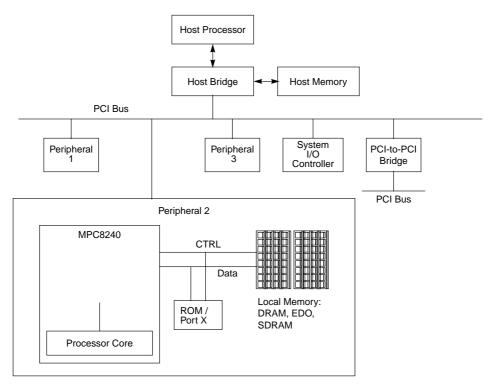

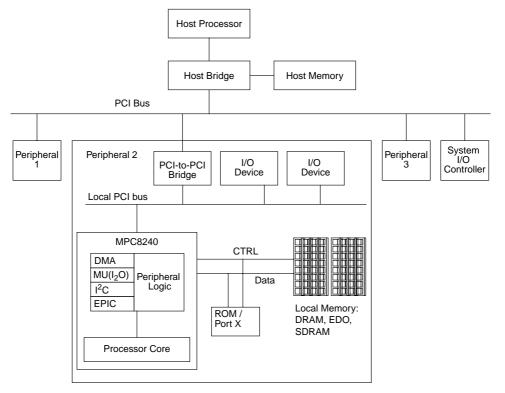

| 1.1.2   | MPC8240 Integrated Processor Applications                   |

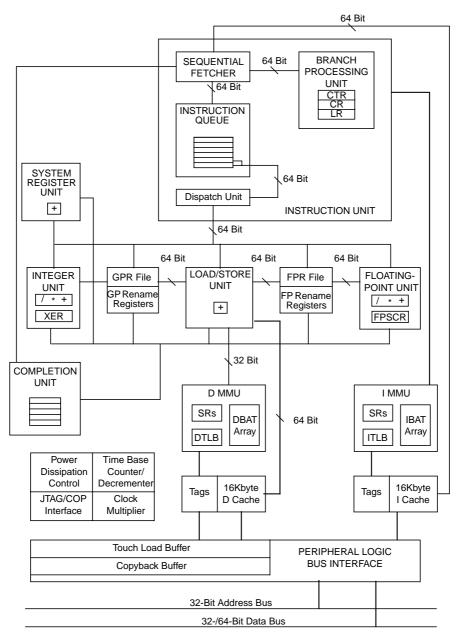

| 1.2     | Processor Core Overview                                     |

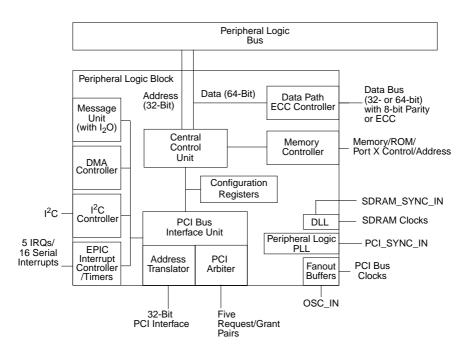

| 1.3     | Peripheral Logic Bus1-10                                    |

| 1.4     | Peripheral Logic Overview 1-11                              |

| 1.4.1   | Peripheral Logic Features 1-11                              |

| 1.4.2   | Peripheral Logic Functional Units                           |

| 1.4.3   | Memory System Interface                                     |

| 1.4.4   | Peripheral Component Interconnect (PCI) Interface 1-14      |

| 1.4.4.1 | PCI Bus Arbitration Unit 1-14                               |

| 1.4.4.2 | Address Maps and Translation 1-14                           |

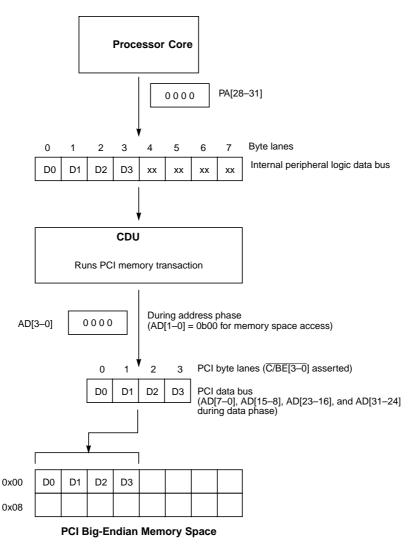

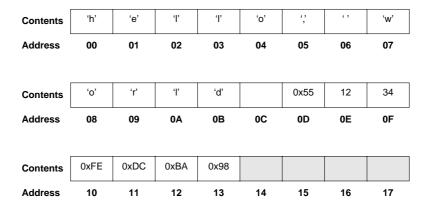

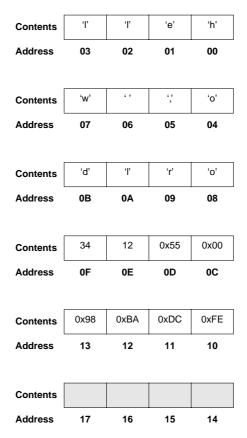

| 1.4.4.3 | Byte Ordering 1-15                                          |

| 1.4.4.4 | PCI Agent Capability1-15                                    |

| 1.4.5   | DMA Controller1-15                                          |

| 1.4.6   | Message Unit (MU) 1-15                                      |

| 1.4.6.1 | Doorbell Registers 1-15                                     |

| 1.4.6.2 | Inbound and Outbound Message Registers 1-16                 |

| 1.4.6.3 | Intelligent Input/Output Controller (I <sub>2</sub> O) 1-16 |

| 1.4.7   | Inter-Integrated Circuit (I <sup>2</sup> C) Controller      |

| 1.4.8   | Embedded Programmable Interrupt Controller (EPIC) 1-16      |

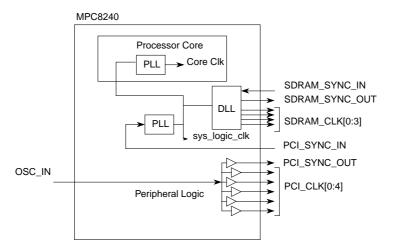

| 1.4.9   | Integrated PCI Bus and SDRAM Clock Generation 1-17          |

| 1.5     | Power Management                                            |

| 1.5.1   | Programmable Processor Power Management Modes 1-18          |

| 1.5.2   | Programmable Peripheral Logic Power Management Modes 1-18   |

| 1.6     | Programmable I/O Signals with Watchpoint 1-19               |

| 1.7     | Debug Features                                              |

| 1.7.1   | Memory Attribute and PCI Attribute Signals 1-20             |

| 1.7.2   | Memory Debug Address 1-20                                   |

| 1.7.3   | Memory Interface Valid (MIV)                                |

|         |                                                             |

| Paragraph<br>Number  | Title                                                                                                     | Page<br>Number |

|----------------------|-----------------------------------------------------------------------------------------------------------|----------------|

| 1.7.4                | Error Injection/Capture on Data Path                                                                      |                |

| 1.7.5                | IEEE 1149.1 (JTAG)/Test Interface                                                                         | 1-20           |

|                      | Chapter 2 Signal Descriptions and Clocking                                                                |                |

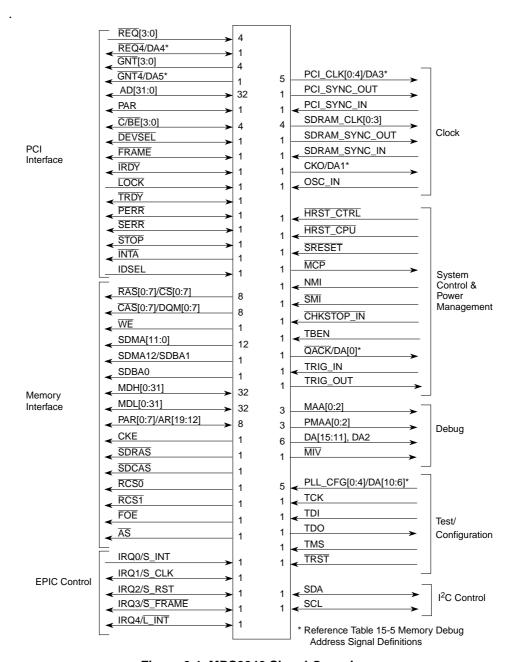

| 2.1                  | Signal Overview                                                                                           |                |

| 2.1.1                | Signal Cross Reference                                                                                    |                |

| 2.1.2                | Output Signal States during Reset                                                                         |                |

| 2.2                  | Detailed Signal Descriptions                                                                              |                |

| 2.2.1                | PCI Interface Signals                                                                                     |                |

| 2.2.1.1              | PCI Bus Request (REQ[4:0])—Input                                                                          |                |

| 2.2.1.1.1            | PCI Bus Request (REQ[4:0])—Internal Arbiter Enabled                                                       |                |

| 2.2.1.1.2            | PCI Bus Request (REQ[4:0])—Internal Arbiter Disabled                                                      |                |

| 2.2.1.2              | PCI Bus Grant (GNT[4:0])—Output                                                                           |                |

| 2.2.1.2.1            | PCI Bus Grant (GNT[4:0])—Internal Arbiter Enabled                                                         |                |

| 2.2.1.2.2            | PCI Bus Grant (GNT[4:0])—Internal Arbiter Disabled                                                        |                |

| 2.2.1.3              | PCI Address/Data Bus (AD[31:0])                                                                           |                |

| 2.2.1.3.1            | Address/Data (AD[31:0])—Output                                                                            |                |

| 2.2.1.3.2            | Address/Data (AD[31:0])—Input                                                                             |                |

| 2.2.1.4              | Parity (PAR)                                                                                              |                |

| 2.2.1.4.1            | Parity (PAR)—Output                                                                                       |                |

| 2.2.1.4.2            | Parity (PAR)—Input                                                                                        |                |

| 2.2.1.5              | Command/Byte Enable $(\overline{C/BE}[3:0])$                                                              |                |

| 2.2.1.5.1            | Command/Byte Enable $(\overline{C/BE}[3:0])$ —Output                                                      |                |

| 2.2.1.5.2<br>2.2.1.6 | Command/Byte Enable ( $\overline{\text{C/BE}}[3:0]$ )—Input  Device Select ( $\overline{\text{DEVSEL}}$ ) |                |

| 2.2.1.6              | Device Select (DEVSEL)—Output                                                                             |                |

| 2.2.1.6.1            | Device Select (DEVSEL)—Output  Device Select (DEVSEL)—Input                                               |                |

| 2.2.1.7              | Frame (FRAME)                                                                                             |                |

| 2.2.1.7              | Frame (FRAME)—Output                                                                                      |                |

| 2.2.1.7.1            | Frame (FRAME)—Input                                                                                       |                |

| 2.2.1.8              | Initiator Ready (IRDY)                                                                                    |                |

| 2.2.1.8.1            | Initiator Ready (IRDY)—Output                                                                             |                |

| 2.2.1.8.2            | Initiator Ready (IRDY)—Input                                                                              | 2-13           |

| 2.2.1.9              | Lock ( <del>LOCK</del> )—Input                                                                            |                |

| 2.2.1.10             | Target Ready (TRDY)                                                                                       |                |

| 2.2.1.10.1           | Target Ready (TRDY)—Output                                                                                | 2-13           |

| 2.2.1.10.2           | Target Ready (TRDY)—Input                                                                                 | 2-14           |

| 2.2.1.11             | Parity Error (PERR)                                                                                       |                |

| 2.2.1.11.1           | Parity Error (PERR)—Output                                                                                |                |

| 2.2.1.11.2           | Parity Error (PERR)—Input                                                                                 |                |

| Paragraph<br>Number | Title                                                | Page<br>umber |

|---------------------|------------------------------------------------------|---------------|

| 2.2.1.12            | System Error (SERR)                                  |               |

| 2.2.1.12.1          | System Error (SERR)—Output                           | 2-15          |

| 2.2.1.12.2          | System Error (SERR)—Input                            | 2-15          |

| 2.2.1.13            | Stop ( <del>STOP</del> )                             | 2-15          |

| 2.2.1.13.1          | Stop (STOP)—Output                                   |               |

| 2.2.1.13.2          | Stop (STOP)—Input                                    | 2-15          |

| 2.2.1.14            | Interrupt Request (INTA)—Output                      | 2-15          |

| 2.2.1.15            | ID Select (IDSEL)—Input                              | 2-16          |

| 2.2.2               | Memory Interface Signals                             | 2-16          |

| 2.2.2.1             | Row Address Strobe (RAS[0:7])—Output                 | 2-16          |

| 2.2.2.2             | Column Address Strobe (\overline{CAS[0:7]})—Output   | 2-17          |

| 2.2.2.3             | SDRAM Command Select (CS[0:7])—Output                | 2-17          |

| 2.2.2.4             | SDRAM Data Input/Output Mask (DQM[0:7])—Output       | 2-17          |

| 2.2.2.5             | Write Enable (WE)—Output                             | 2-18          |

| 2.2.2.6             | SDRAM Address (SDMA[11:0])—Output                    |               |

| 2.2.2.7             | SDRAM Address 12 (SDMA12)—Output                     | 2-18          |

| 2.2.2.8             | SDRAM Internal Bank Select 0–1 (SDBA0, SDBA1)—Output | 2-18          |

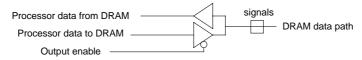

| 2.2.2.9             | Memory Data Bus (MDH[0:31], MDL[0:31])               | 2-19          |

| 2.2.2.9.1           | Memory Data Bus (MDH[0:31], MDL[0:31])—Output        | 2-20          |

| 2.2.2.9.2           | Memory Data Bus (MDH[0:31], MDL[0:31])—Input         | 2-20          |

| 2.2.2.10            | Data Parity/ECC (PAR[0:7])                           |               |

| 2.2.2.10.1          | Data Parity (PAR[0:7])—Output                        | 2-20          |

| 2.2.2.10.2          | Data Parity (PAR[0:7])—Input                         | 2-21          |

| 2.2.2.11            | ROM Address 19:12 (AR[19:12])—Output                 | 2-21          |

| 2.2.2.12            | SDRAM Clock Enable (CKE)—Output                      | 2-21          |

| 2.2.2.13            | SDRAM Row Address Strobe (SDRAS)—Output              | 2-21          |

| 2.2.2.14            | SDRAM Column Address Strobe (SDCAS)—Output           | 2-22          |

| 2.2.2.15            | ROM Bank 0 Select (RCS0)—Output                      | 2-22          |

| 2.2.2.16            | ROM Bank 1 Select (RCS1)—Output                      | 2-22          |

| 2.2.2.17            | Flash Output Enable (FOE)—Output                     | 2-23          |

| 2.2.2.18            | Address Strobe (AS)—Output                           |               |

| 2.2.3               | EPIC Control Signals                                 |               |

| 2.2.3.1             | Discrete Interrupt 0:4 (IRQ[0:4])—Input              | 2-23          |

| 2.2.3.2             | Serial Interrupt Mode Signals                        |               |

| 2.2.3.2.1           | Serial Interrupt Stream (S_INT)—Input                |               |

| 2.2.3.2.2           | Serial Interrupt Clock (S_CLK)—Output                |               |

| 2.2.3.2.3           | Serial Interrupt Reset (S_RST)—Output                | 2-24          |

| 2.2.3.2.4           | Serial Interrupt Frame (S_FRAME)—Output              | 2-24          |

| 2.2.3.3             | Local Interrupt (LINT)—Output                        | 2-24          |

| 2.2.4               | I <sup>2</sup> C Interface Control Signals           |               |

| 2.2.4.1             | Serial Data (SDA)                                    |               |

| 2.2.4.1.1           | Serial Data (SDA)—Output                             | 2-25          |

| 2.2.4.1.2           | Serial Data (SDA)—Input                              | 2-25          |

| Paragraph<br>Number |                                                     | Page<br>mber |

|---------------------|-----------------------------------------------------|--------------|

| 2.2.4.2             | Serial Clock (SCL)                                  | 2-25         |

| 2.2.4.2.1           | Serial Clock (SCL)—Output                           | 2-25         |

| 2.2.4.2.2           | Serial Clock (SCL)—Input                            | 2-25         |

| 2.2.5               | System Control and Power Management Signals         |              |

| 2.2.5.1             | Hard Reset                                          |              |

| 2.2.5.1.1           | Hard Reset (Processor) (HRST_CPU)—Input             | 2-26         |

| 2.2.5.1.2           | Hard Reset (Peripheral Logic) (HRST_CTRL)—Input     | 2-26         |

| 2.2.5.2             | Soft Reset (SRESET)—Input                           |              |

| 2.2.5.3             | Machine Check (MCP)—Output                          |              |

| 2.2.5.4             | Nonmaskable Interrupt (NMI)—Input                   | 2-27         |

| 2.2.5.5             | System Management Interrupt (SMI)—Input             | 2-28         |

| 2.2.5.6             | Checkstop In (CHKSTOP_IN)—Input                     | 2-28         |

| 2.2.5.7             | Time Base Enable (TBEN)—Input                       | 2-28         |

| 2.2.5.8             | Quiesce Acknowledge (QACK)—Output                   | 2-28         |

| 2.2.5.9             | Watchpoint Trigger Signals                          |              |

| 2.2.5.9.1           | Watchpoint Trigger In (TRIG_IN)—Input               | 2-29         |

| 2.2.5.9.2           | Watchpoint Trigger Out (TRIG_OUT)—Output            | 2-29         |

| 2.2.5.10            | Debug Signals                                       | 2-29         |

| 2.2.5.10.1          | Memory Address Attributes (MAA[0:2])—Output         | 2-30         |

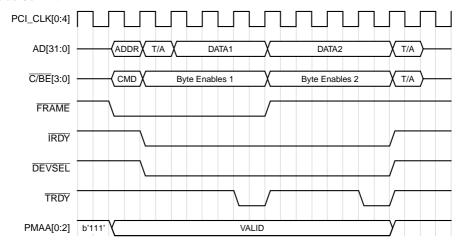

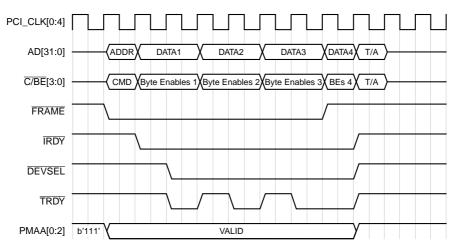

| 2.2.5.10.2          | PCI Address Attributes (PMAA[0:2])—Output           | 2-30         |

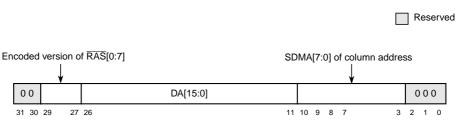

| 2.2.5.10.3          | Debug Address (DA[0:15])—Output                     | 2-30         |

| 2.2.5.10.4          | Memory Interface Valid (MIV)—Output                 | 2-31         |

| 2.2.6               | Test and Configuration Signals                      | 2-31         |

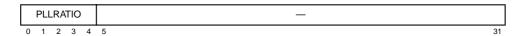

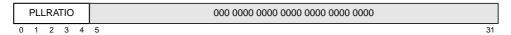

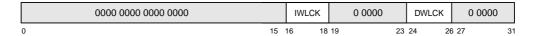

| 2.2.6.1             | PLL Configuration (PLL_CFG[0:4])—Input              | 2-31         |

| 2.2.6.2             | JTAG Test Clock (TCK)—Input                         |              |

| 2.2.6.3             | JTAG Test Data Input (TDI)—Input                    |              |

| 2.2.6.4             | JTAG Test Data Output (TDO)—Output                  |              |

| 2.2.6.5             | JTAG Test Mode Select (TMS)—Input                   |              |

| 2.2.6.6             | JTAG Test Reset (TRST)—Input                        | 2-32         |

| 2.2.7               | Clock Signals                                       |              |

| 2.2.7.1             | System Clock Input (OSC_IN)—Input                   |              |

| 2.2.7.2             | PCI Clock (PCI_CLK[0:4])—Output                     |              |

| 2.2.7.3             | PCI Clock Synchronize Out (PCI_SYNC_OUT)—Output     |              |

| 2.2.7.4             | PCI Feedback Clock (PCI_SYNC_IN)—Input              |              |

| 2.2.7.5             | SDRAM Clock Outputs (SDRAM_CLK[0:3])—Output         |              |

| 2.2.7.6             | SDRAM Clock Synchronize Out (SDRAM_SYNC_OUT)—Output |              |

| 2.2.7.7             | SDRAM Feedback Clock (SDRAM_SYNC_IN)—Input          |              |

| 2.2.7.8             | Debug Clock (CKO)—Output                            |              |

| 2.3                 | Clocking                                            |              |

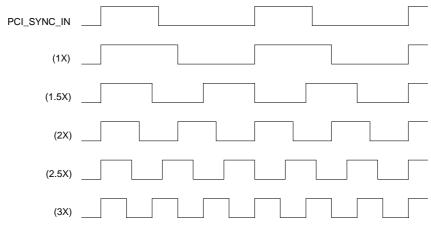

| 2.3.1               | Clocking Method                                     |              |

| 2.3.2               | DLL Operation and Locking                           |              |

| 2.3.3               | Clock Synchronization                               |              |

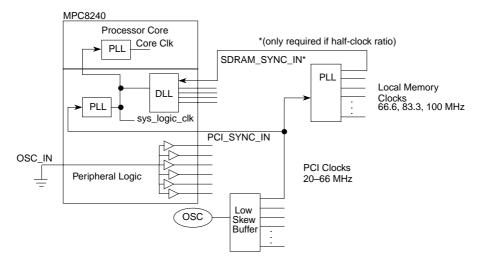

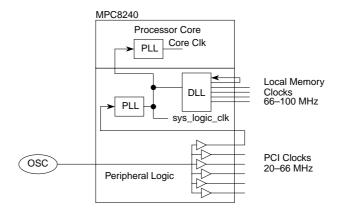

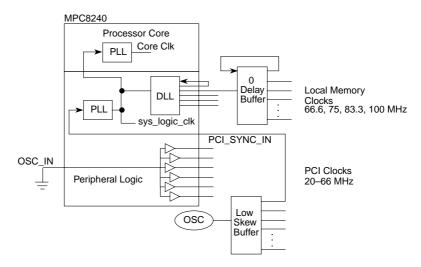

| 2.3.4               | Clocking System Solution Examples                   |              |

| 2.4                 | Configuration Signals Sampled at Reset              | 2-38         |

| Paragraph<br>Number                                                                                                                                                          | Title Nu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Page<br>umber                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|                                                                                                                                                                              | Chapter 3<br>Address Maps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                           |

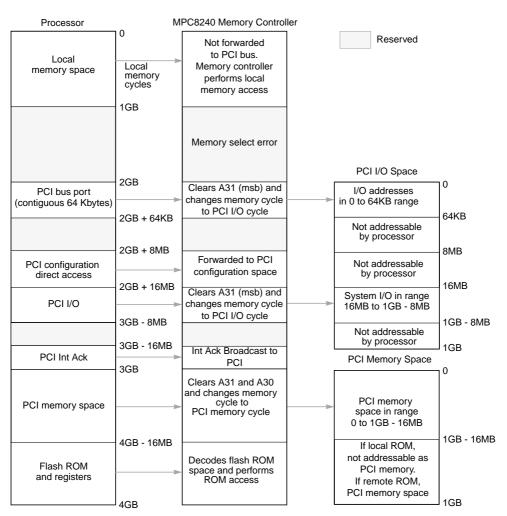

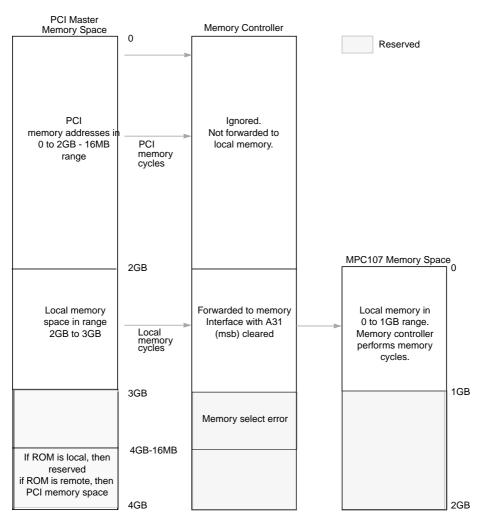

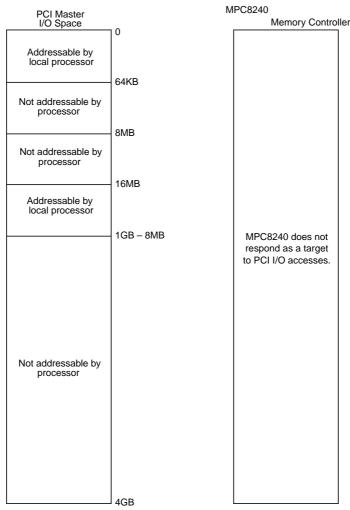

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.3.1<br>3.3.3.2<br>3.3.3.3<br>3.3.3.4<br>3.4                                                            | Address Map B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-7<br>3-7<br>3-9<br>3-11<br>3-13<br>3-14<br>3-15<br>3-15<br>3-16<br>3-17 |

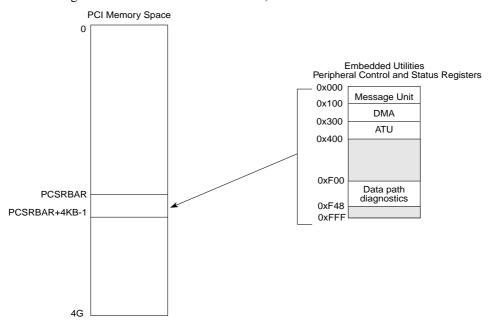

| 3.4.2                                                                                                                                                                        | Peripheral Control and Status Registers  Chapter 4  Configuration Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-19                                                                      |

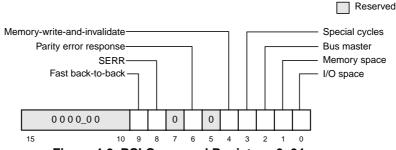

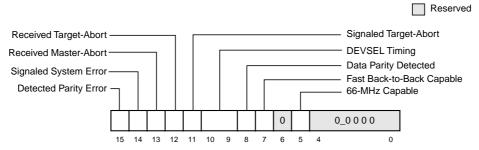

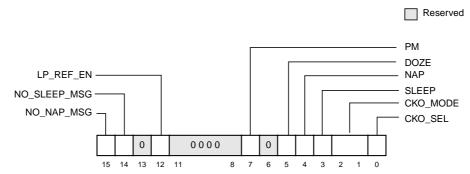

| 4.1<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.3.1<br>4.1.3.2<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>4.2.7<br>4.2.8<br>4.2.9<br>4.3<br>4.3.1<br>4.3.2<br>4.4 | Configuration Register Access in Little-Endian Mode  Configuration Register Access in Big-Endian Mode  Configuration Register Summary  Processor-Accessible Configuration Registers  PCI-Accessible Configuration Registers  PCI Interface Configuration Registers  PCI Command Register—Offset 0x04  PCI Status Register—Offset 0x06  Programming Interface—Offset 0x09  PCI Base Class Code—Offset 0x0B  PCI Cache Line Size—Offset 0x0C  Latency Timer—Offset 0x0D  PCI Base Address Registers—LMBAR and PCSRBAR  PCI Interrupt Line—Offset 0x3C  PCI Arbiter Control Register (PACR)—Offset 0x46  Peripheral Logic Power Management Configuration Registers (PMCRs)  Power Management Configuration Register 1 (PMCR1)—Offset 0x70  Power Management Configuration Register 2 (PMCR2)—Offset 0x72  Output/Clock Driver and Miscellaneous I/O Control Registers | 4-2 4-3 4-5 4-5 4-10 4-11 4-12 4-14 4-14 4-14 4-15 4-16 4-17 4-18         |

| Paragraph<br>Number    | Title                                                                                   | Page<br>Number |

|------------------------|-----------------------------------------------------------------------------------------|----------------|

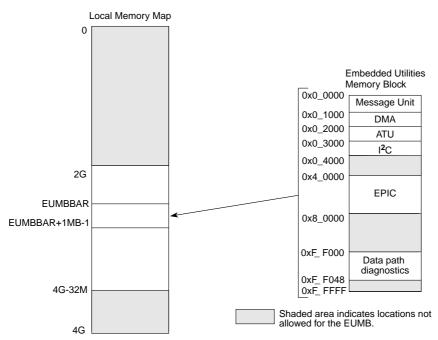

| 4.5                    | Embedded Utilities Memory Block Base Address Register—0x78                              | 4-22           |

| 4.6                    | Memory Interface Configuration Registers                                                | 4-23           |

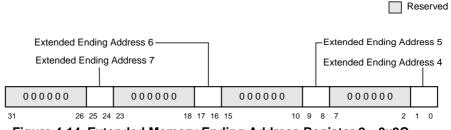

| 4.6.1                  | Memory Boundary Registers                                                               |                |

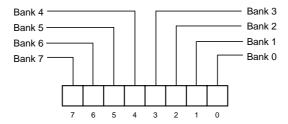

| 4.6.2                  | Memory Bank Enable Register—0xA0                                                        | 4-27           |

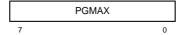

| 4.6.3                  | Memory Page Mode Register—0xA3                                                          | 4-28           |

| 4.7                    | Processor Interface Configuration Registers                                             |                |

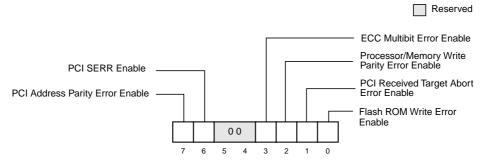

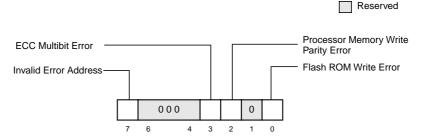

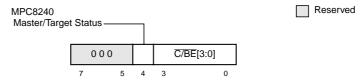

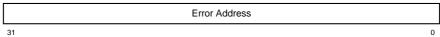

| 4.8                    | Error Handling Registers                                                                |                |

| 4.8.1                  | ECC Single-Bit Error Registers                                                          |                |

| 4.8.2                  | Error Enabling and Detection Registers                                                  |                |

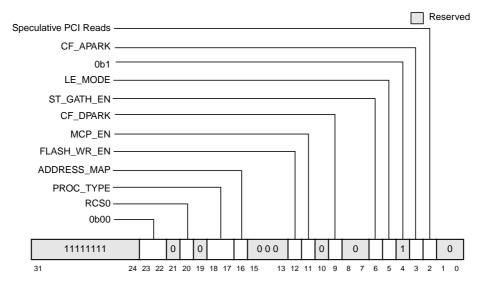

| 4.9                    | Address Map B Options Register—0xE0                                                     |                |

| 4.10                   | Memory Control Configuration Registers                                                  | 4-42           |

|                        | Chapter 5 PowerPC Processor Core                                                        |                |

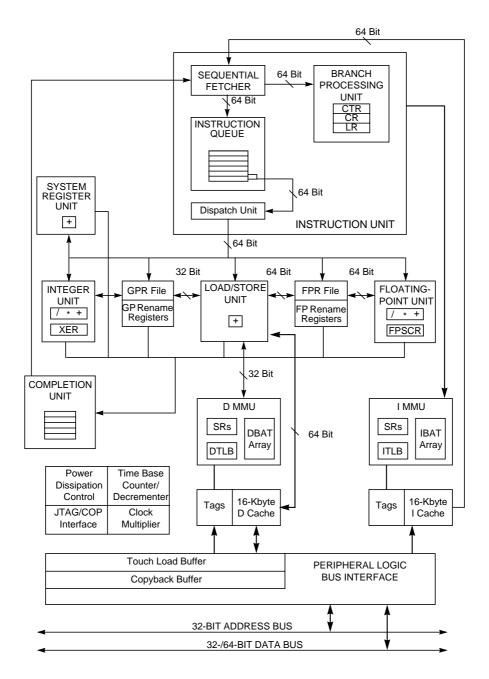

| 5.1                    | Overview                                                                                | 5-1            |

| 5.2                    | PowerPC Processor Core Features                                                         |                |

| 5.2.1                  | Instruction Unit                                                                        | 5-5            |

| 5.2.2                  | Instruction Queue and Dispatch Unit                                                     | 5-6            |

| 5.2.3                  | Branch Processing Unit (BPU)                                                            | 5-6            |

| 5.2.4                  | Independent Execution Units                                                             |                |

| 5.2.4.1                | Integer Unit (IU)                                                                       | 5-7            |

| 5.2.4.2                | Floating-Point Unit (FPU)                                                               |                |

| 5.2.4.3                | Load/Store Unit (LSU)                                                                   |                |

| 5.2.4.4                | System Register Unit (SRU)                                                              |                |

| 5.2.5                  | Completion Unit                                                                         |                |

| 5.2.6                  | Memory Subsystem Support                                                                |                |

| 5.2.6.1                | Memory Management Units (MMUs)                                                          |                |

| 5.2.6.2                | Cache Units                                                                             |                |

| 5.2.6.3                | Peripheral Logic Bus Interface                                                          |                |

| 5.2.6.3.1              | Peripheral Logic Bus Protocol                                                           |                |

| 5.2.6.3.2              | Peripheral Logic Bus Data Transfers                                                     |                |

| 5.2.6.3.3              | Peripheral Logic Bus Frequency                                                          |                |

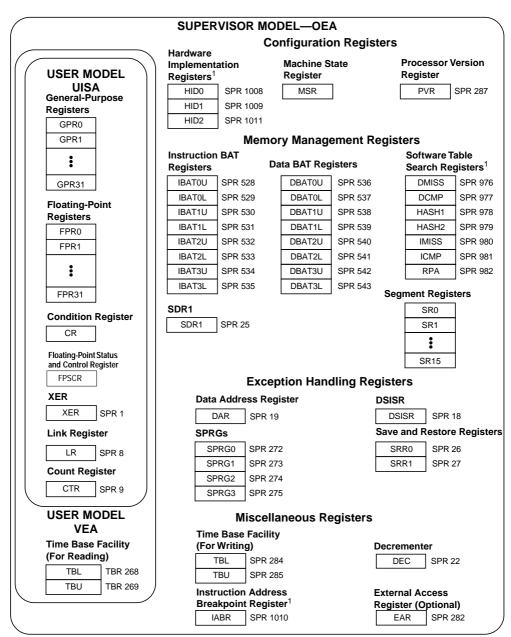

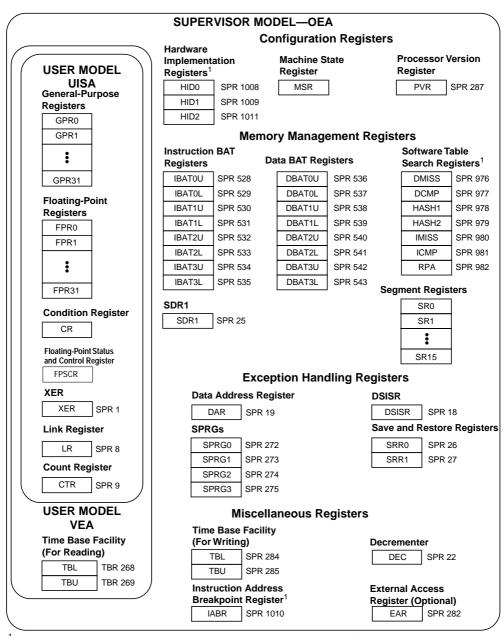

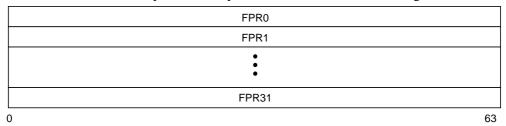

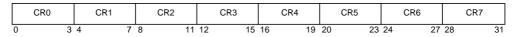

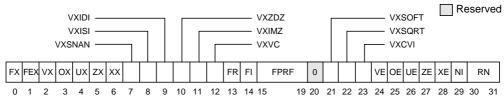

| 5.3                    | Programming Model                                                                       |                |

| 5.3.1                  | Register Set                                                                            |                |

| 5.3.1.1                | PowerPC Register Set                                                                    |                |

| 5.3.1.2                | MPC8240-Specific Registers                                                              |                |

| 5.3.1.2.1              | Hardware Implementation-Dependent Register 0 (HID0)                                     |                |

| 5.3.1.2.2              | Hardware Implementation-Dependent Register 1 (HID1)                                     |                |

| 5.3.1.2.3<br>5.3.1.2.4 | Hardware Implementation-Dependent Register 2 (HID2)<br>Processor Version Register (PVR) |                |

| 5.3.1.2.4              | PowerPC Instruction Set and Addressing Modes                                            |                |

|                        |                                                                                         |                |

| Paragraph<br>Number | Title                                                | Page<br>Number |

|---------------------|------------------------------------------------------|----------------|

| 5.3.2.1             | Calculating Effective Addresses                      | 5-18           |

| 5.3.2.2             | PowerPC Instruction Set                              |                |

| 5.3.2.3             | MPC8240 Implementation-Specific Instruction Set      |                |

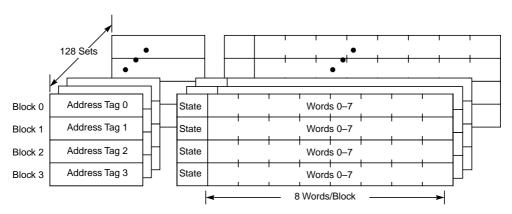

| 5.4                 | Cache Implementation                                 | 5-20           |

| 5.4.1               | PowerPC Cache Model                                  | 5-20           |

| 5.4.2               | MPC8240 Implementation-Specific Cache Implementation | 5-21           |

| 5.4.2.1             | Data Cache                                           | 5-21           |

| 5.4.2.2             | Instruction Cache                                    | 5-23           |

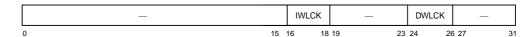

| 5.4.2.3             | Cache Locking                                        |                |

| 5.4.2.3.1           | Entire Cache Locking                                 | 5-23           |

| 5.4.2.3.2           | Way Locking                                          |                |

| 5.4.3               | Cache Coherency                                      |                |

| 5.4.3.1             | CCU Responses to Processor Transactions              |                |

| 5.4.3.2             | Processor Responses to PCI-to-Memory Transactions    | 5-25           |

| 5.5                 | Exception Model                                      | 5-26           |

| 5.5.1               | PowerPC Exception Model                              |                |

| 5.5.2               | MPC8240 Implementation-Specific Exception Model      | 5-27           |

| 5.5.3               | Exception Priorities                                 |                |

| 5.6                 | Memory Management                                    | 5-30           |

| 5.6.1               | PowerPC MMU Model                                    |                |

| 5.6.2               | MPC8240 Implementation-Specific MMU Features         | 5-31           |

| 5.7                 | Instruction Timing                                   | 5-32           |

| 5.8                 | Differences between the MPC8240 Core                 |                |

|                     | and the PowerPC 603e Microprocessor                  | 5-34           |

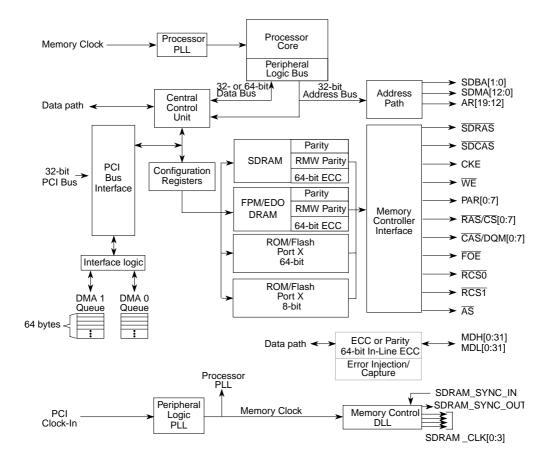

|                     | Chapter 6                                            |                |

|                     | MPC8240 Memory Interface                             |                |

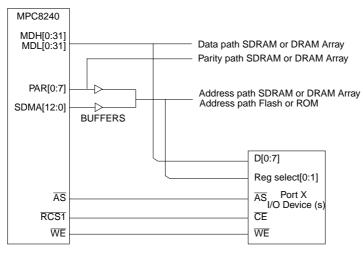

| 6.1                 | Memory Interface Signal Summary                      |                |

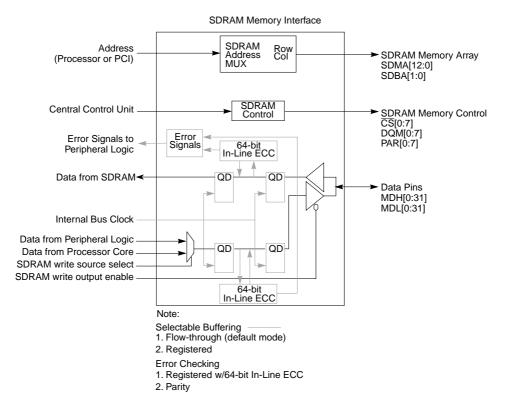

| 6.2                 | SDRAM Interface Operation                            | 6-6            |

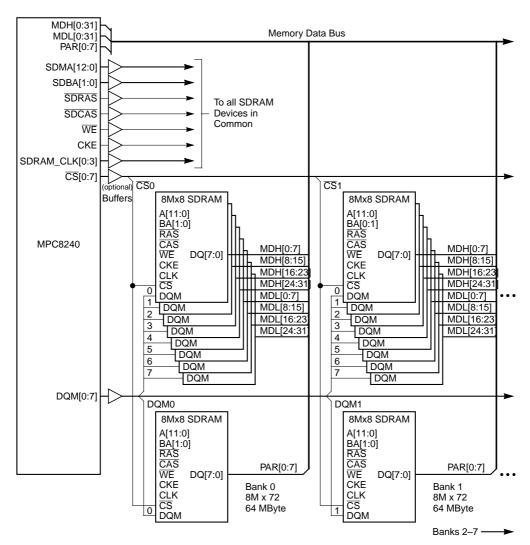

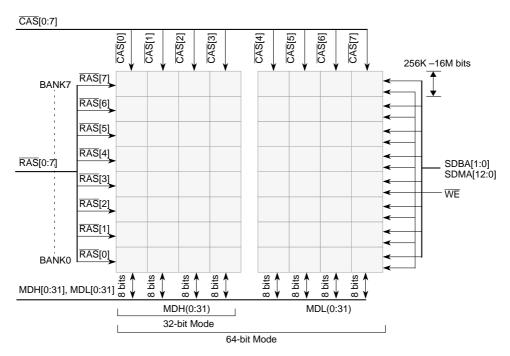

| 6.2.1               | Supported SDRAM Organizations                        | 6-9            |

| 6.2.2               | SDRAM Address Multiplexing                           | 6-10           |

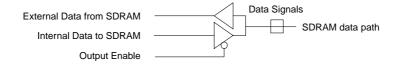

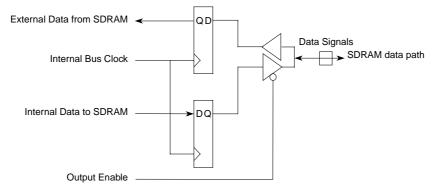

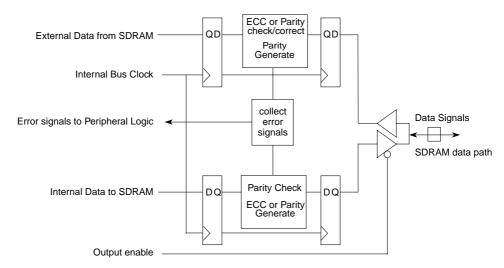

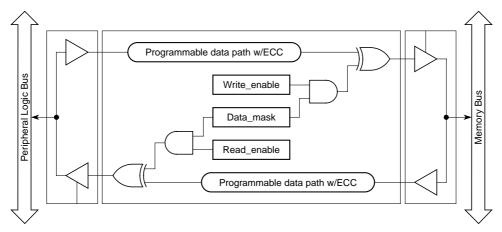

| 6.2.3               | SDRAM Memory Data Interface                          | 6-13           |

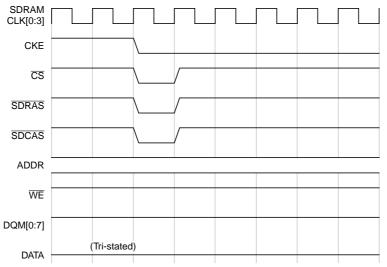

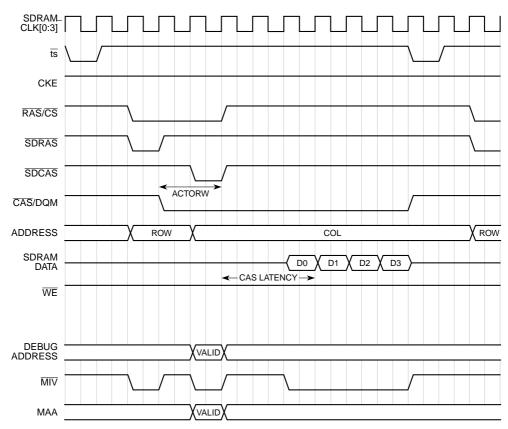

| 6.2.4               | SDRAM Power-On Initialization                        |                |

| 6.2.5               | MPC8240 Interface Functionality for JEDEC SDRAMs     |                |

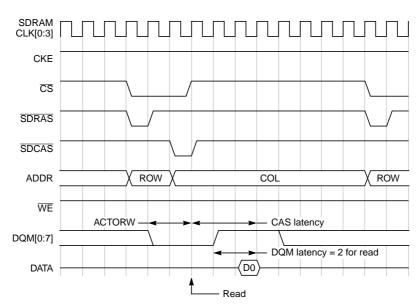

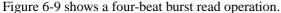

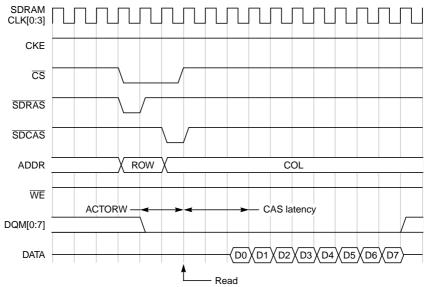

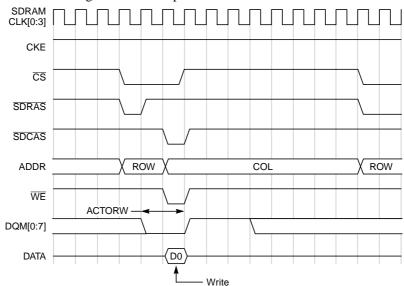

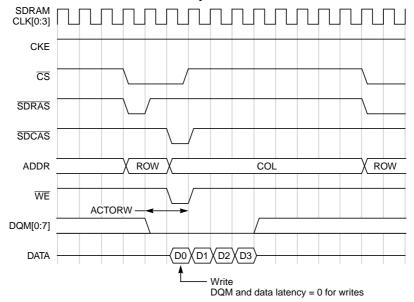

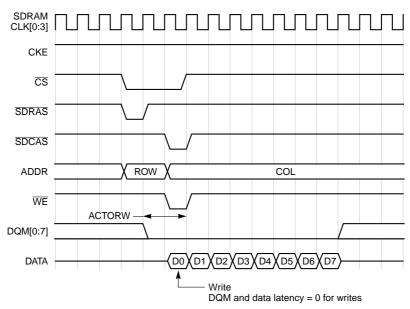

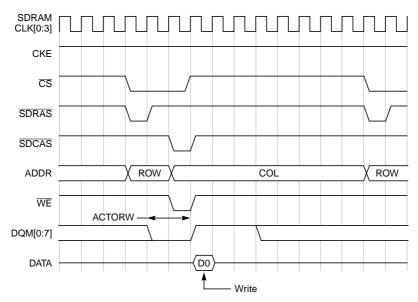

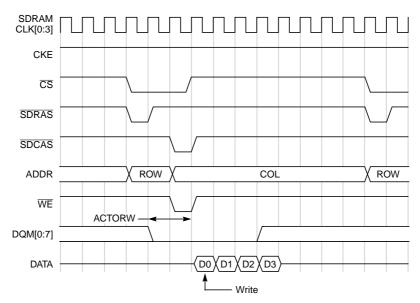

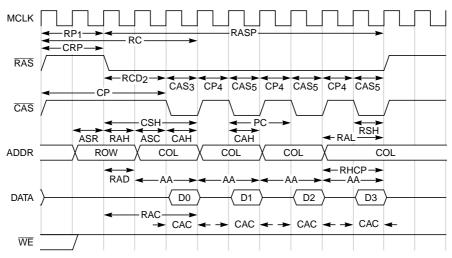

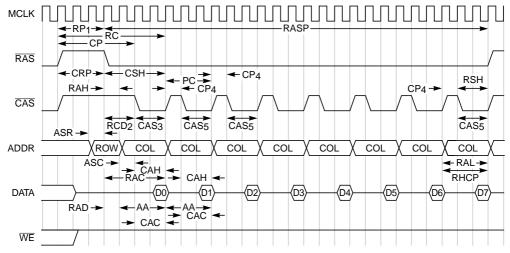

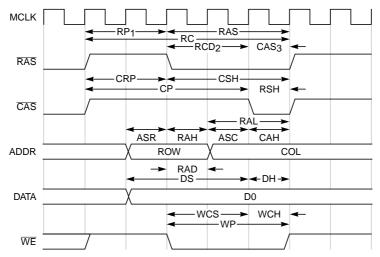

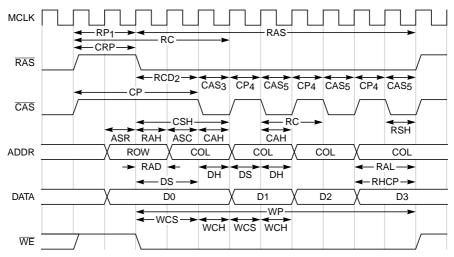

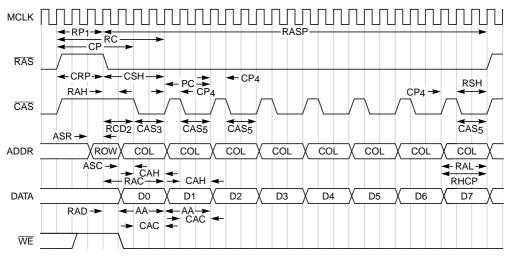

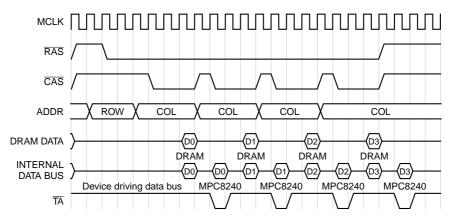

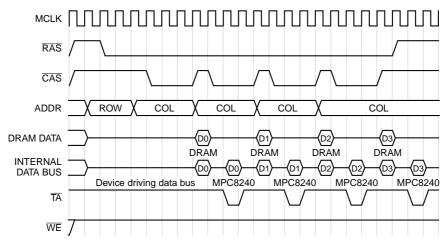

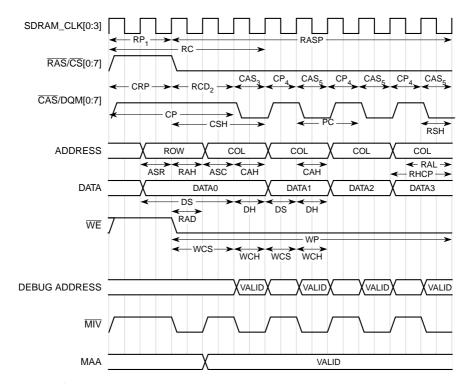

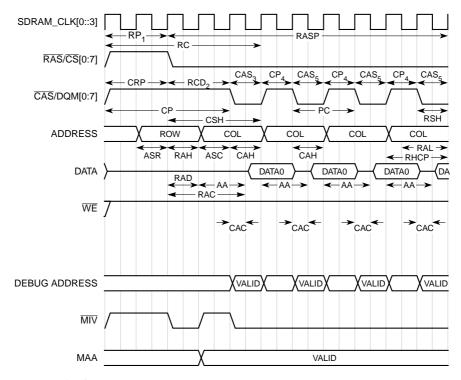

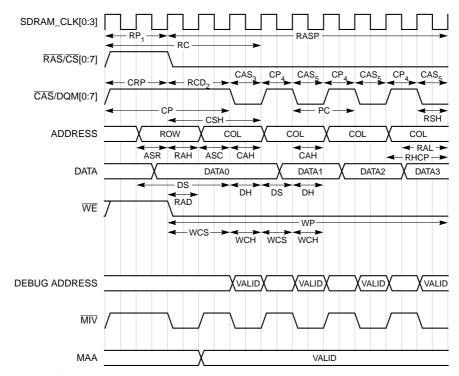

| 6.2.6               | SDRAM Burst and Single-Beat Transactions             |                |

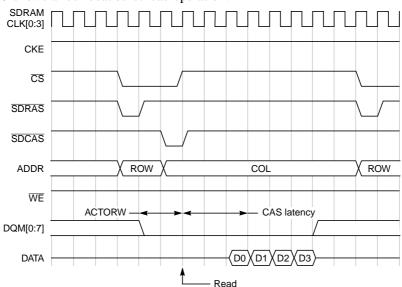

| 6.2.7               | SDRAM Page Mode                                      | 6-19           |

| 6.2.7.1             | SDRAM Paging in Sleep Mode                           |                |

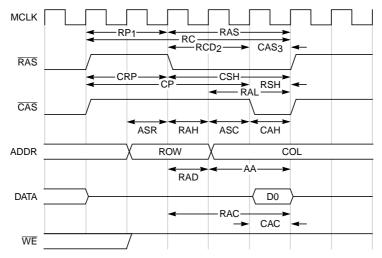

| 6.2.8               | SDRAM Interface Timing                               |                |

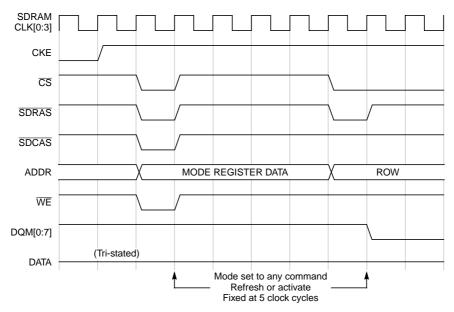

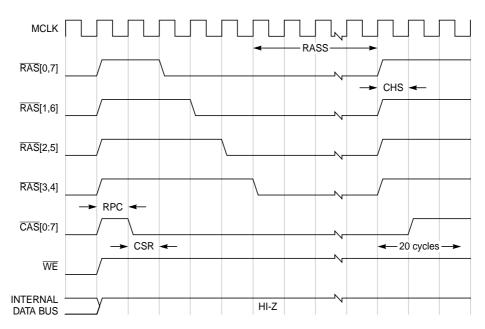

| 6.2.8.1             | SDRAM Mode-Set Command Timing                        |                |

| 6.2.9               | SDRAM Parity and RMW Parity                          |                |

| 6.2.9.1             | RMW Parity Latency Considerations                    | 6-27           |

| Paragraph<br>Number         | Title                                                 | Page<br>Number |

|-----------------------------|-------------------------------------------------------|----------------|

| 6.2.10                      | SDRAM In-Line ECC                                     | 6-27           |

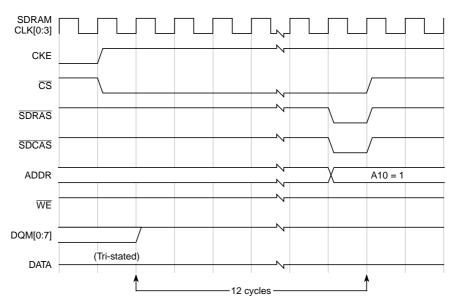

| 6.2.11                      | SDRAM Registered DIMM Mode                            | 6-29           |

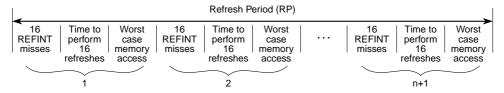

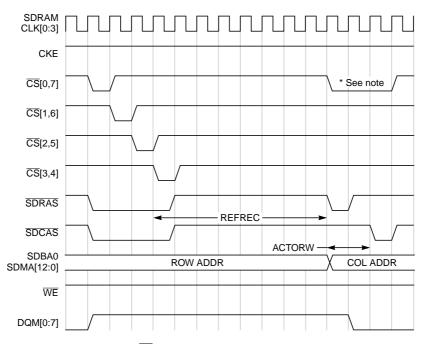

| 6.2.12                      | SDRAM Refresh                                         | 6-31           |

| 6.2.12.1                    | SDRAM Refresh Timing                                  | 6-33           |

| 6.2.12.2                    | SDRAM Refresh and Power Saving Modes                  |                |

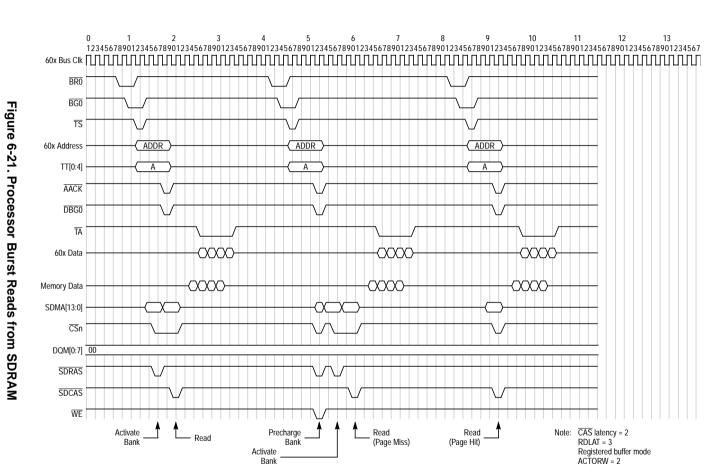

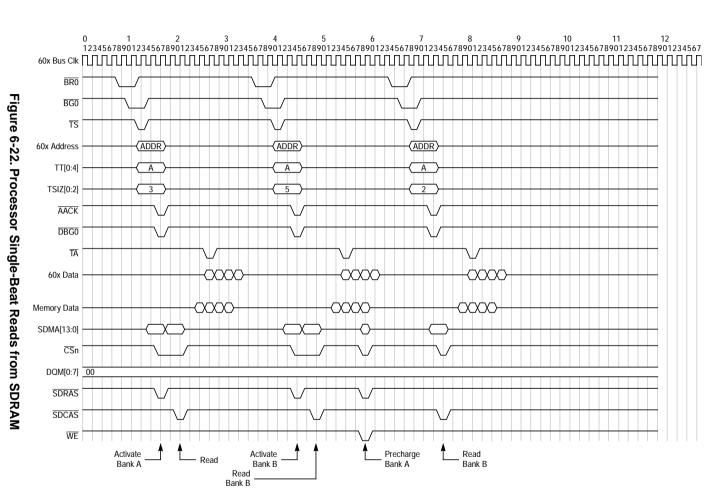

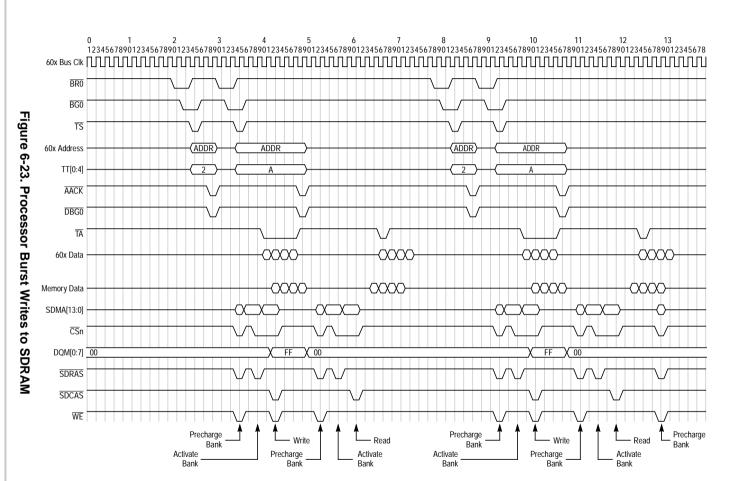

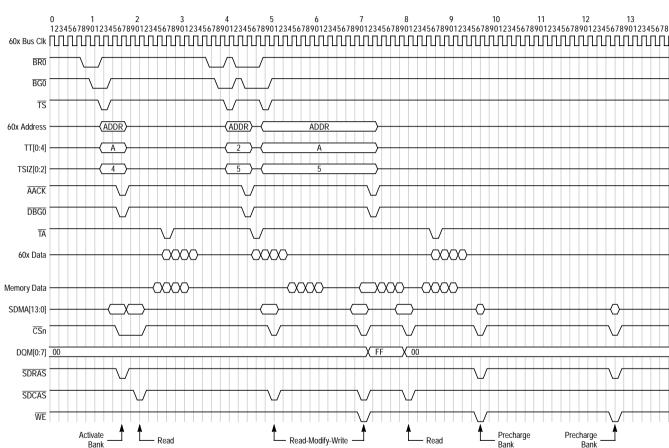

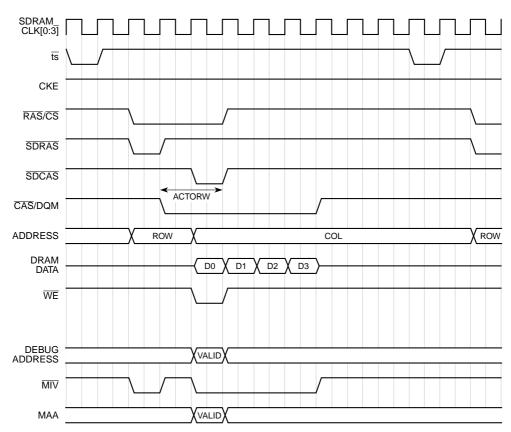

| 6.2.13                      | Processor-to-SDRAM Transaction Examples               | 6-36           |

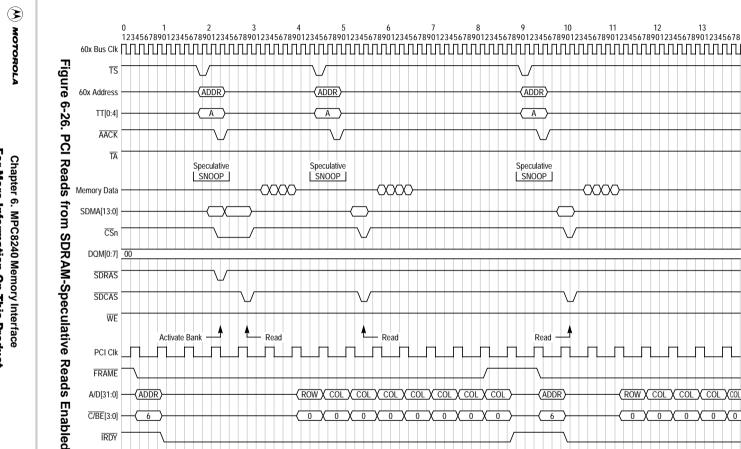

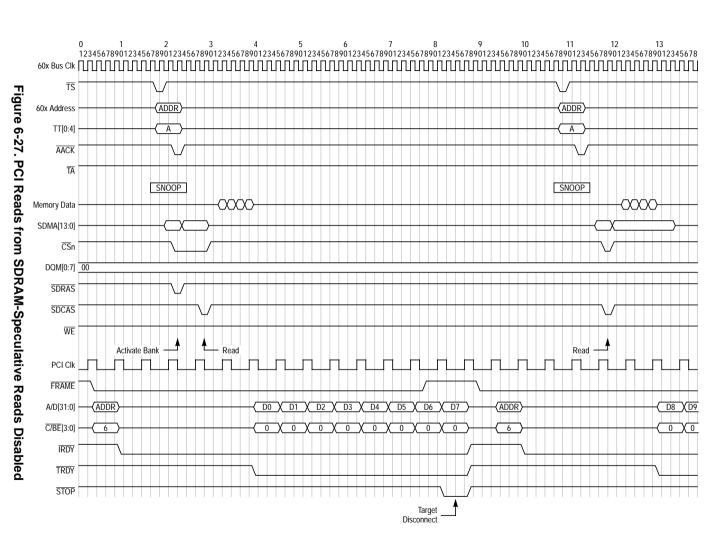

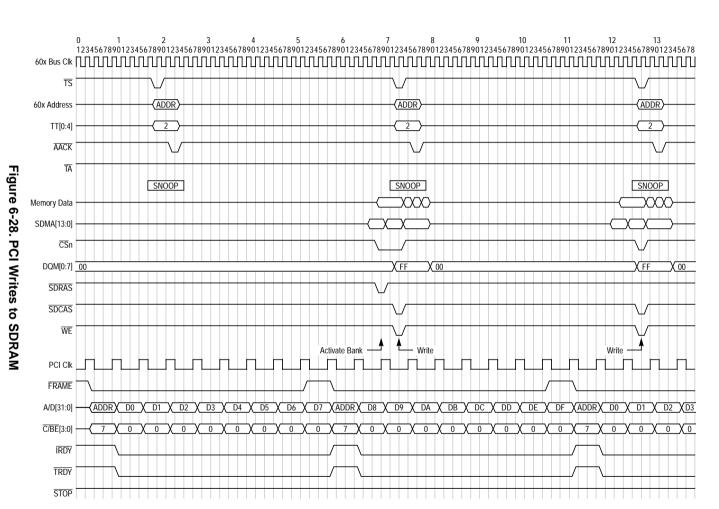

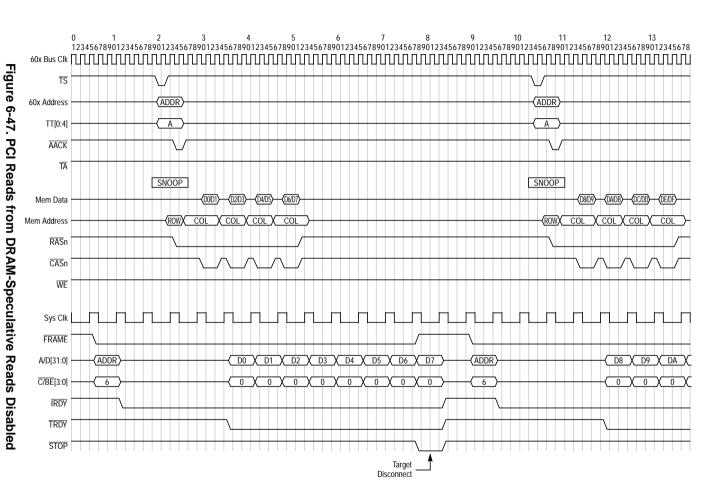

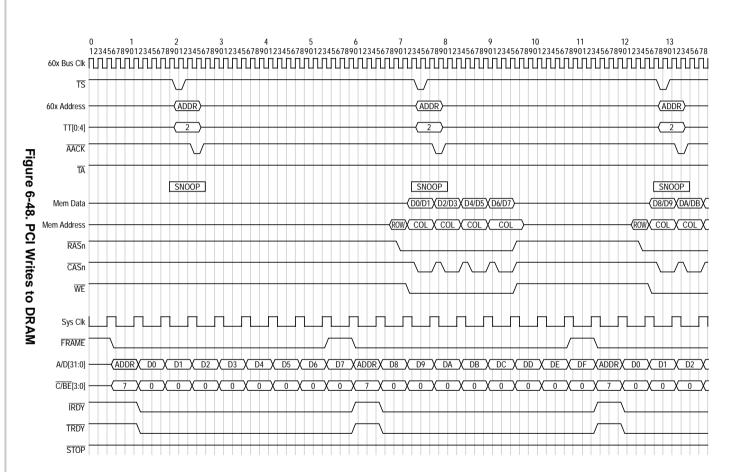

| 6.2.14                      | PCI-to-SDRAM Transaction Examples                     | 6-42           |

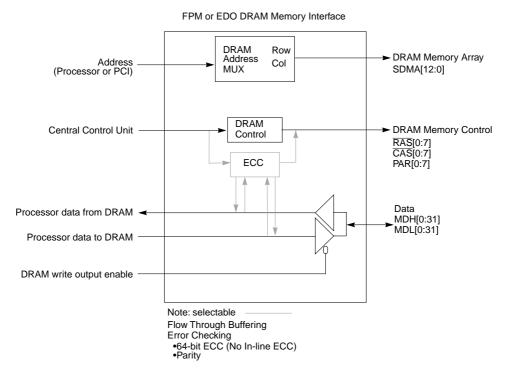

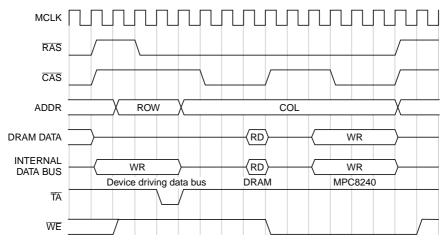

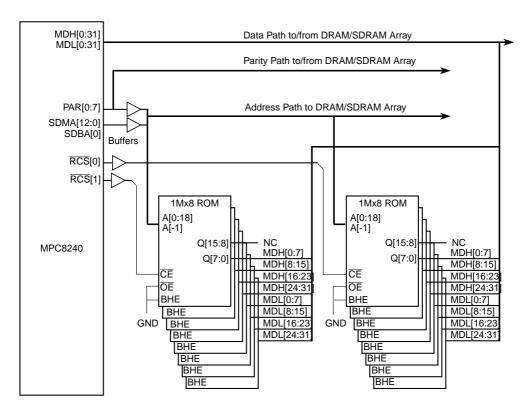

| 6.3                         | FPM or EDO DRAM Interface Operation                   |                |

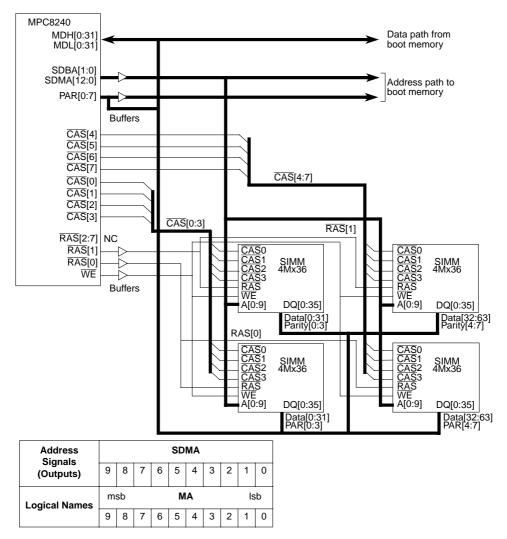

| 6.3.1                       | Supported FPM or EDO DRAM Organizations               | 6-48           |

| 6.3.2                       | FPM or EDO DRAM Address Multiplexing                  | 6-50           |

| 6.3.2.1                     | Row Bit Multiplexing During The Row Phase (RAS)       | 6-50           |

| 6.3.2.2                     | Column Bit Multiplexing During the Column Phase (CAS) | 6-51           |

| 6.3.2.3                     | Graphical View of the Row and Column Bit Multiplexing | 6-51           |

| 6.3.3                       | FPM or EDO Memory Data Interface                      | 6-54           |

| 6.3.4                       | FPM or EDO DRAM Initialization                        | 6-55           |

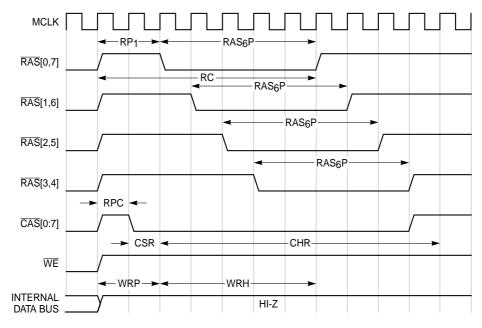

| 6.3.5                       | FPM or EDO DRAM Interface Timing                      | 6-56           |

| 6.3.6                       | DMA Burst Wrap                                        | 6-61           |

| 6.3.7                       | FPM or EDO DRAM Page Mode Retention                   |                |

| 6.3.8                       | FPM or EDO DRAM Parity and RMW Parity                 | 6-61           |

| 6.3.8.1                     | RMW Parity Latency Considerations                     | 6-62           |

| 6.3.9                       | FPM or EDO ECC                                        | 6-62           |

| 6.3.9.1                     | FPM or EDO DRAM Interface Timing with ECC             | 6-64           |

| 6.3.10                      | FPM or EDO DRAM Refresh                               | 6-66           |

| 6.3.10.1                    | FPM or EDO Refresh Timing                             | 6-66           |

| 6.3.11                      | FPM or EDO DRAM Power Saving Modes                    | 6-67           |

| 6.3.11.1                    | Configuration Parameters for DRAM Power Saving Modes  | 6-67           |

| 6.3.11.2                    | DRAM Self-Refresh in Sleep Mode                       | 6-68           |

| 6.3.12                      | PCI-to-DRAM Transaction Examples                      | 6-69           |

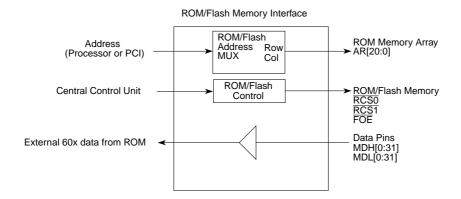

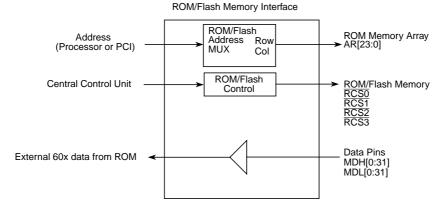

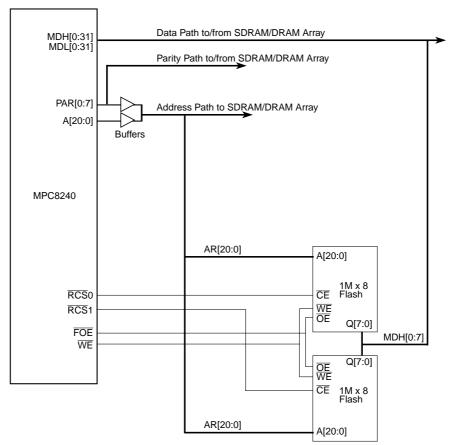

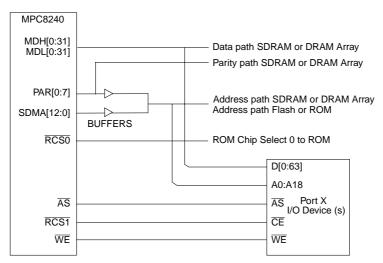

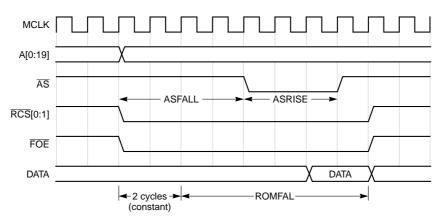

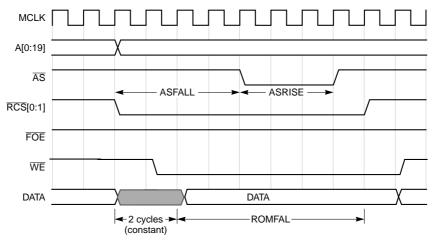

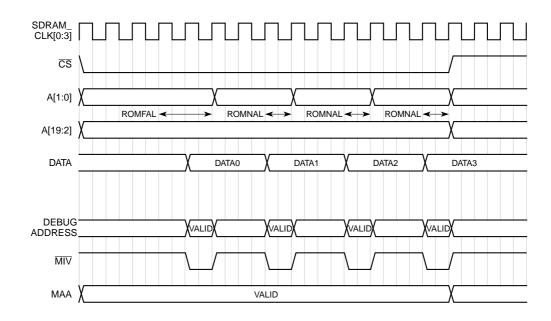

| 6.4                         | ROM/Flash Interface Operation                         | 6-73           |

| 6.4.1                       | ROM/Flash Address Multiplexing                        | 6-77           |

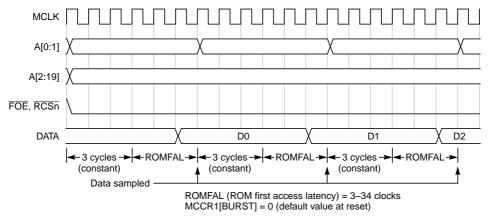

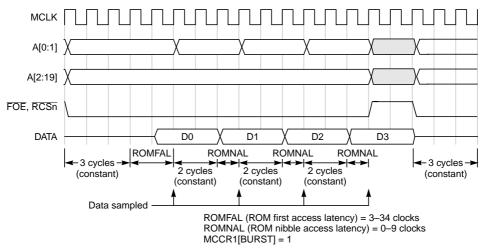

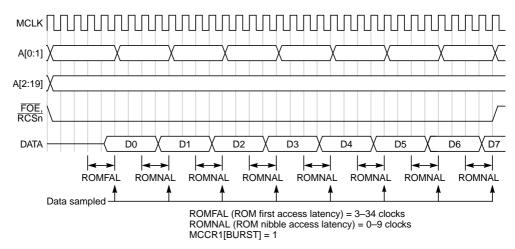

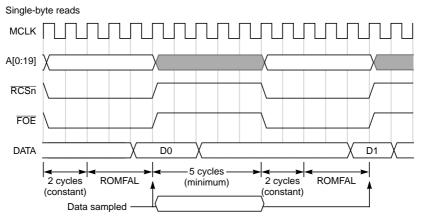

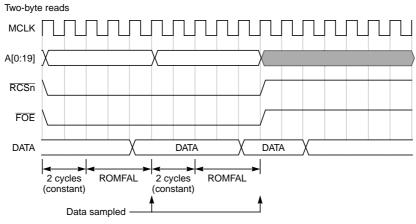

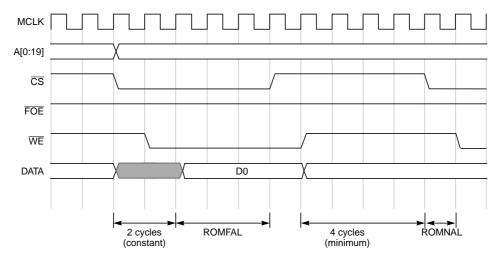

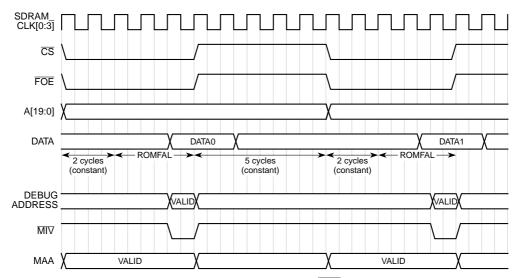

| 6.4.2                       | 64 or 32-Bit ROM/Flash Interface Timing               | 6-78           |

| 6.4.3                       | 8-Bit ROM/Flash Interface Timing                      | 6-81           |

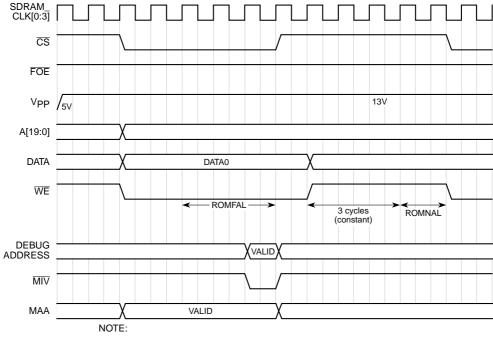

| 6.4.4                       | ROM/Flash Interface Write Operations                  |                |

| 6.4.5                       | ROM/Flash Interface Write Timing                      | 6-84           |

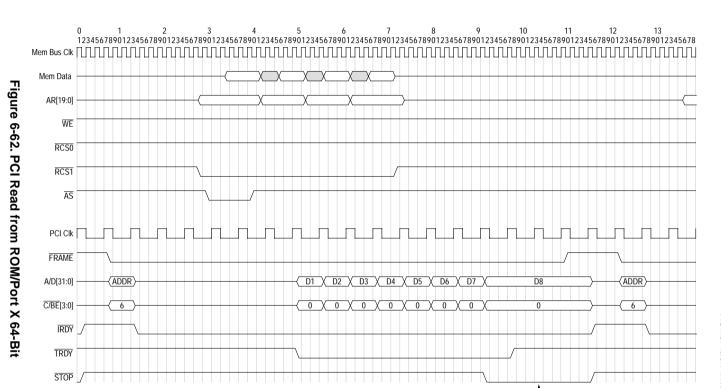

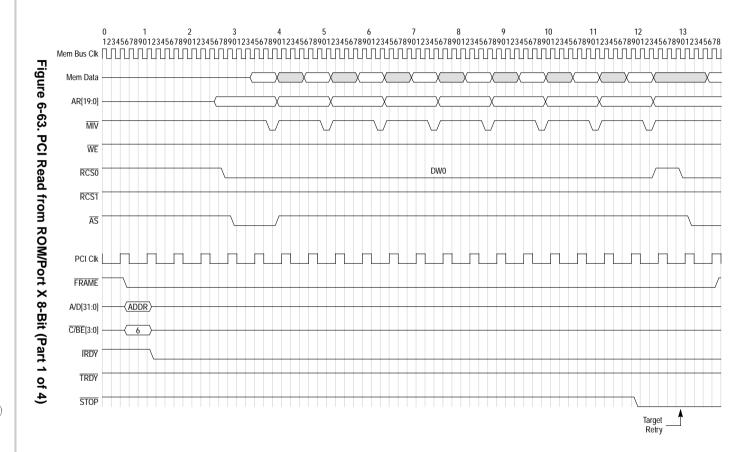

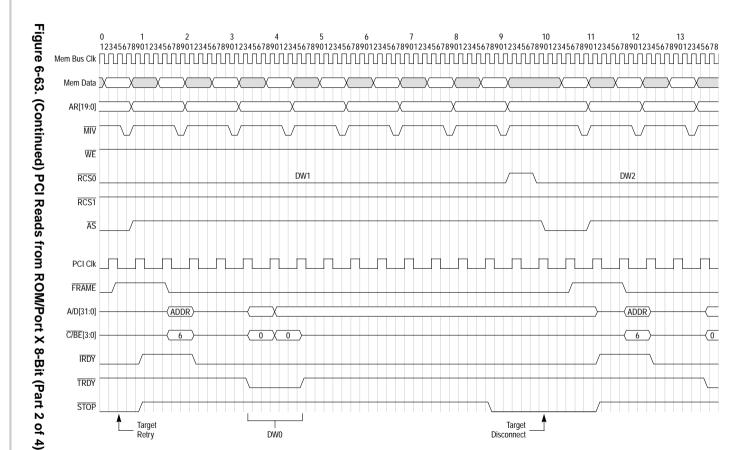

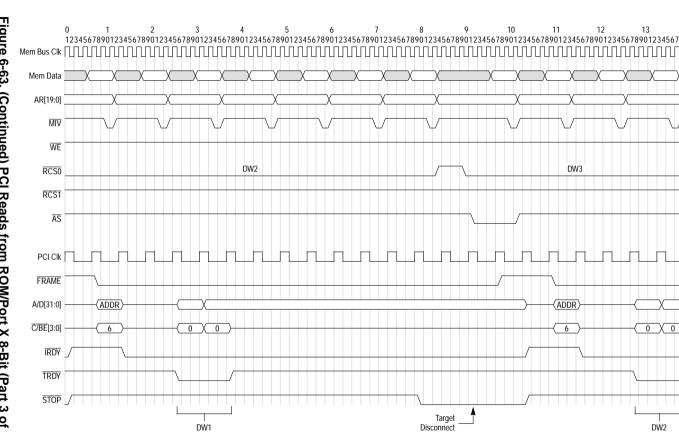

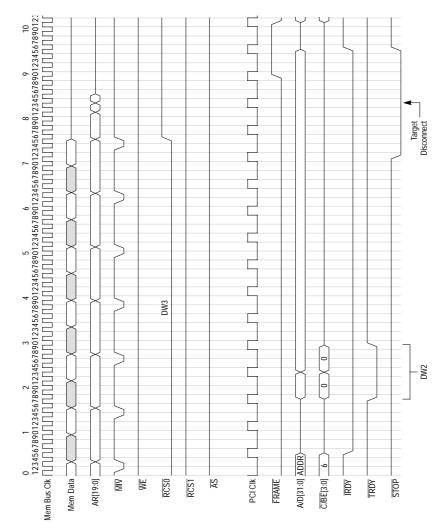

| 6.4.6                       | PCI-to-ROM/Port X Transaction Example                 | 6-84           |

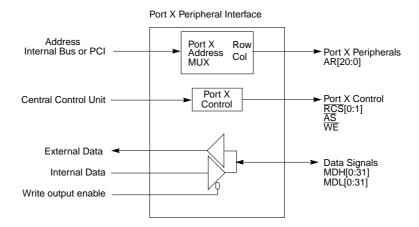

| 6.4.7                       | Port X Interface                                      | 6-89           |

| Chapter 7 PCI Bus Interface |                                                       |                |

| 7.1<br>7.1.1                | PCI Interface Overview The MPC8240 as a PCI Initiator |                |

| ,                           | 110 111 002 10 us u 1 01 Intuator                     |                |

| Paragraph<br>Number | Title                                       | Page<br>Number |

|---------------------|---------------------------------------------|----------------|

| 7.1.2               | The MPC8240 as a PCI Target                 | 7-3            |

| 7.1.3               | PCI Signal Output Hold Timing               | 7-3            |

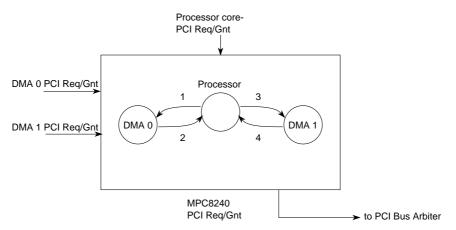

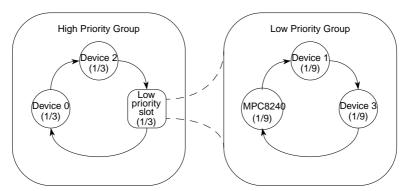

| 7.2                 | PCI Bus Arbitration                         | 7-4            |

| 7.2.1               | Internal Arbitration for PCI Bus Access     |                |

| 7.2.1.1             | Processor-Initiated Transactions to PCI Bus |                |

| 7.2.1.2             | DMA-Initiated Transactions to the PCI Bus   | 7-5            |

| 7.2.2               | PCI Bus Arbiter Operation                   | 7-6            |

| 7.2.3               | PCI Bus Parking                             |                |

| 7.2.4               | Power-Saving Modes and the PCI Arbiter      |                |

| 7.2.5               | Broken Master Lock-Out                      |                |

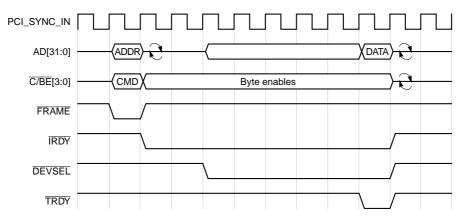

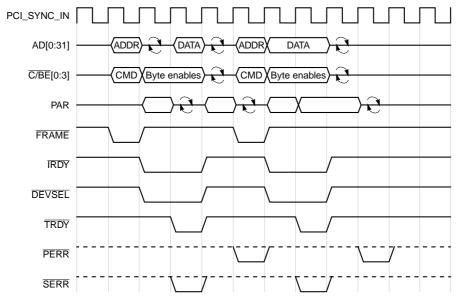

| 7.3                 | PCI Bus Protocol                            | 7-8            |

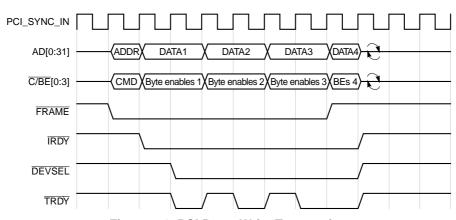

| 7.3.1               | Basic Transfer Control                      | 7-9            |

| 7.3.2               | PCI Bus Commands                            | 7-9            |

| 7.3.3               | Addressing                                  | 7-11           |

| 7.3.3.1             | Memory Space Addressing                     | 7-12           |

| 7.3.3.2             | I/O Space Addressing                        |                |

| 7.3.3.3             | Configuration Space Addressing              |                |

| 7.3.4               | Device Selection                            |                |

| 7.3.5               | Byte Alignment                              |                |

| 7.3.6               | Bus Driving and Turnaround                  |                |

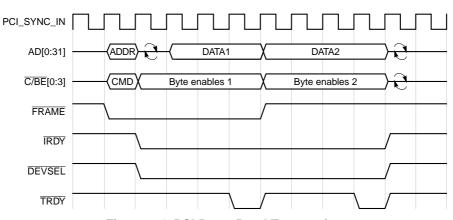

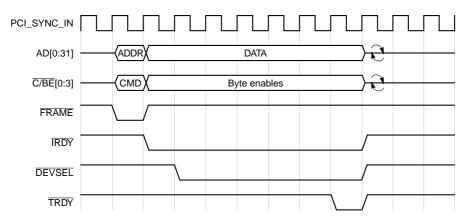

| 7.4                 | PCI Bus Transactions                        |                |

| 7.4.1               | PCI Read Transactions                       | 7-14           |

| 7.4.2               | PCI Write Transactions                      | 7-16           |

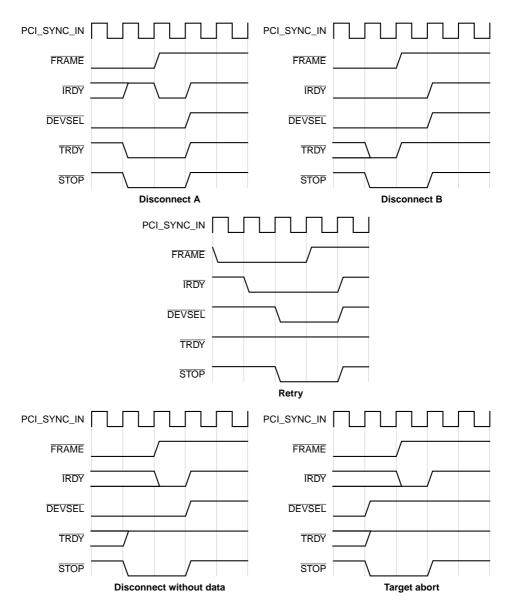

| 7.4.3               | Transaction Termination                     | 7-17           |

| 7.4.3.1             | Master-Initiated Termination                |                |

| 7.4.3.2             | Target-Initiated Termination                | 7-18           |

| 7.4.4               | Fast Back-to-Back Transactions              |                |

| 7.4.5               | Configuration Cycles                        | 7-21           |

| 7.4.5.1             | The PCI Configuration Space Header          |                |

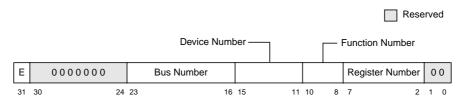

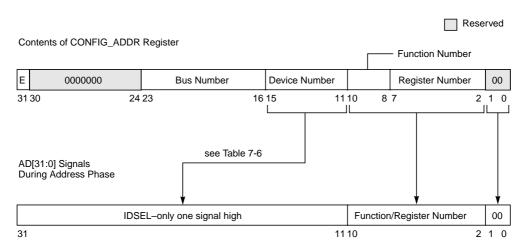

| 7.4.5.2             | Accessing the PCI Configuration Space       | 7-23           |

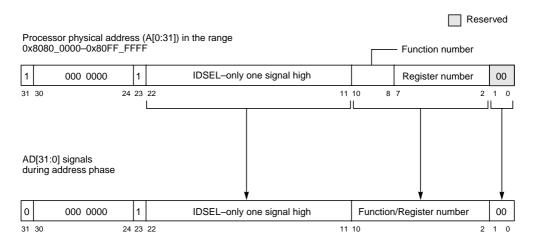

| 7.4.5.2.1           | Type 0 Configuration Translation            | 7-25           |

| 7.4.5.2.2           | Type 1 Configuration Translation            |                |

| 7.4.6               | Other Bus Transactions                      | 7-27           |

| 7.4.6.1             | Interrupt-Acknowledge Transactions          | 7-27           |

| 7.4.6.2             | Special-Cycle Transactions                  | 7-28           |

| 7.5                 | Exclusive Access                            | 7-29           |

| 7.5.1               | Starting an Exclusive Access                | 7-29           |

| 7.5.2               | Continuing an Exclusive Access              | 7-29           |

| 7.5.3               | Completing an Exclusive Access              | 7-30           |

| 7.5.4               | Attempting to Access a Locked Target        | 7-30           |

| 7.5.5               | Exclusive Access and the MPC8240            |                |

| 7.6                 | PCI Error Functions                         | 7-30           |

| 7.6.1               | PCI Parity                                  | 7-31           |

| Paragraph<br>Number | Title                                                       | Page<br>Number |

|---------------------|-------------------------------------------------------------|----------------|

| 7.6.2               | Error Reporting                                             | 7-32           |

| 7.7                 | PCI Host and Agent Modes                                    | 7-32           |

| 7.7.1               | PCI Initialization Options                                  | 7-32           |

| 7.7.2               | Accessing the MPC8240 Configuration Space                   | 7-33           |

| 7.7.3               | PCI Configuration Cycle Retry Capability in Agent Mode      | 7-34           |

| 7.7.4               | PCI Address Translation Support                             | 7-34           |

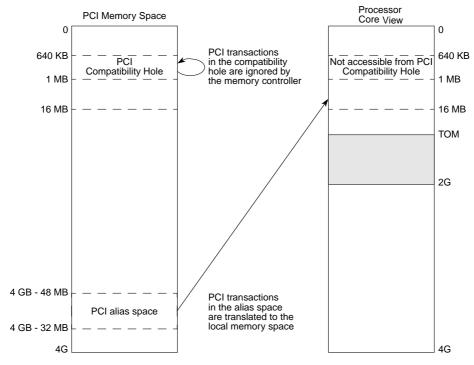

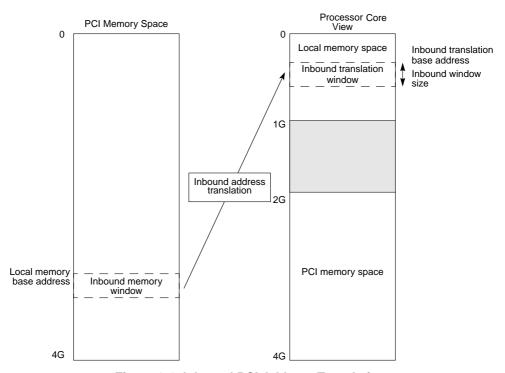

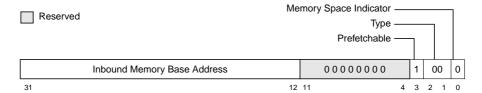

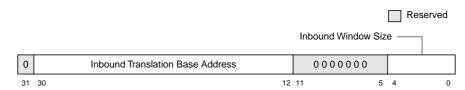

| 7.7.4.1             | Inbound PCI Address Translation                             | 7-34           |

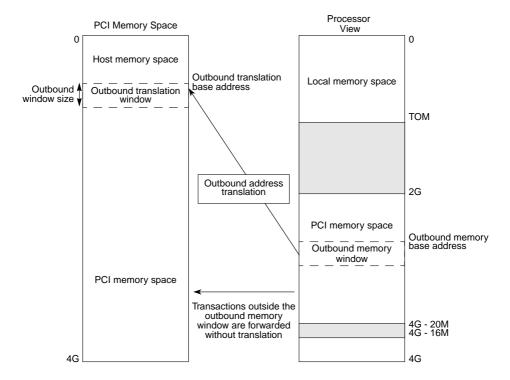

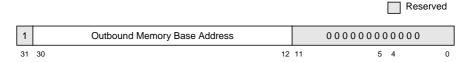

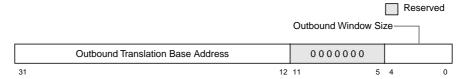

| 7.7.4.2             | Outbound PCI Address Translation                            | 7-34           |

| 7.7.4.3             | Initialization Code Translation in Agent Mode               | 7-35           |

|                     | Chapter 8 DMA Controller                                    |                |

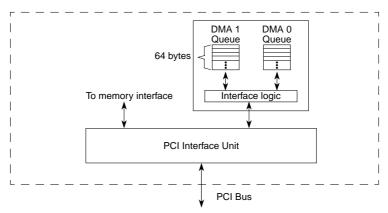

| 8.1                 | DMA Overview                                                | 8-1            |

| 8.2                 | DMA Register Summary                                        | 8-2            |

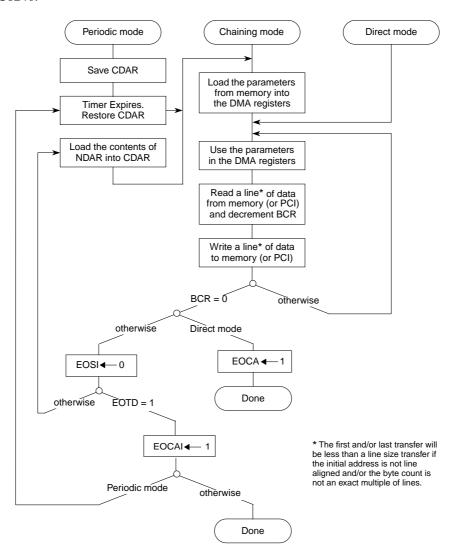

| 8.3                 | DMA Operation                                               |                |

| 8.3.1               | DMA Direct Mode                                             | 8-4            |

| 8.3.2               | DMA Chaining Mode                                           | 8-5            |

| 8.3.2.1             | Basic Chaining Mode Initialization                          | 8-5            |

| 8.3.2.2             | Periodic DMA Feature                                        | 8-6            |

| 8.3.3               | DMA Operation Flow                                          |                |

| 8.3.4               | DMA Coherency                                               | 8-8            |

| 8.3.5               | DMA Performance                                             | 8-8            |

| 8.4                 | DMA Transfer Types                                          | 8-9            |

| 8.4.1               | PCI to PCI                                                  | 8-9            |

| 8.4.2               | PCI to Local Memory                                         | 8-9            |

| 8.4.3               | Local Memory to PCI                                         | 8-9            |

| 8.4.4               | Local Memory to Local Memory                                | 8-9            |

| 8.5                 | Address Map Interactions                                    | 8-10           |

| 8.5.1               | Attempted Writes to Local ROM/Port X Space                  | 8-10           |

| 8.5.2               | Host Mode Interactions                                      | 8-10           |

| 8.5.2.1             | PCI Master Abort when PCI Bus Specified for Lower 2-Gbyte S | pace 8-10      |

| 8.5.2.2             | Address Alias to Lower 2-Gbyte Space                        | 8-10           |

| 8.5.2.3             | Attempted Reads from ROM on the PCI Bus—Host Mode           | 8-11           |

| 8.5.2.4             | Attempted Reads from ROM on the Memory Bus                  | 8-11           |

| 8.5.3               | Agent Mode Interactions                                     | 8-11           |

| 8.5.3.1             | Agent Mode DMA Transfers for PCI                            | 8-11           |

| 8.5.3.2             | Accesses to Outbound Memory Window                          |                |

|                     | that Overlaps 0xFE00_00 - 0xFEEF_FFFF                       | 8-11           |

| 8.5.3.3             | Attempted Accesses to Local ROM when ROM is on PCI          |                |

| 8.5.3.4             | Attempted Access to ROM on the PCI Bus—Agent Mode           | 8-12           |

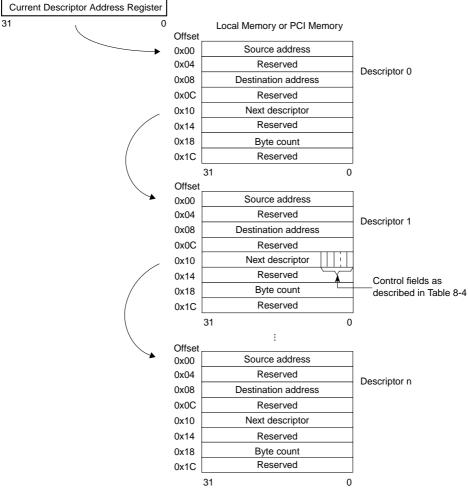

| 8.6                 | DMA Descriptors for Chaining Mode                           |                |

| Paragraph<br>Number | Title                                              | Page<br>Number |

|---------------------|----------------------------------------------------|----------------|

| 8.6.1               | Descriptors in Big-Endian Mode                     | 8-14           |

| 8.6.2               | Descriptors in Little-Endian Mode                  | 8-14           |

| 8.7                 | DMA Register Descriptions                          | 8-15           |

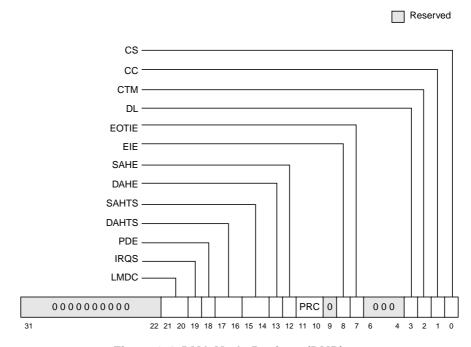

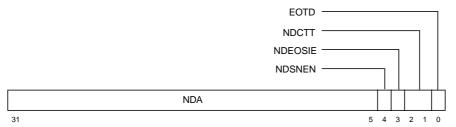

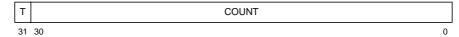

| 8.7.1               | DMA Mode Registers (DMRs)                          | 8-15           |

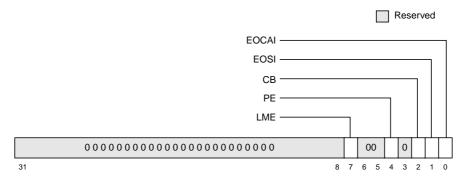

| 8.7.2               | DMA Status Registers (DSRs)                        | 8-18           |

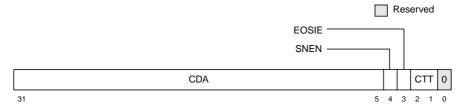

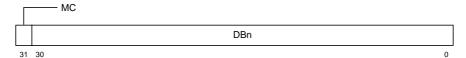

| 8.7.3               | Current Descriptor Address Registers (CDARs)       | 8-19           |

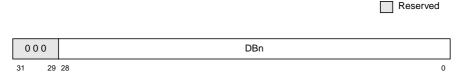

| 8.7.4               | Source Address Registers (SARs)                    |                |

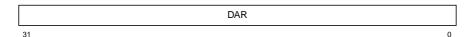

| 8.7.5               | Destination Address Registers (DARs)               |                |

| 8.7.6               | Byte Count Registers (BCRs)                        |                |

| 8.7.7               | DAR and BCR Values—Double PCI Write                | 8-22           |

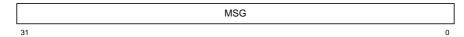

| 8.7.8               | Next Descriptor Address Registers (NDARs)          | 8-23           |

|                     | Chapter 9<br>Message Unit (with I <sub>2</sub> O)  |                |

| 9.1                 | Message Unit (MU) Overview                         | 9-1            |

| 9.2                 | Message and Doorbell Register Programming Model    |                |

| 9.2.1               | Message and Doorbell Register Summary              |                |

| 9.2.2               | Message Register Descriptions                      |                |

| 9.2.3               | Doorbell Register Descriptions                     | 9-3            |

| 9.3                 | I <sub>2</sub> O Interface                         |                |

| 9.3.1               | PCI Configuration Identification                   | 9-5            |

| 9.3.2               | I <sub>2</sub> O Register Summary                  | 9-5            |

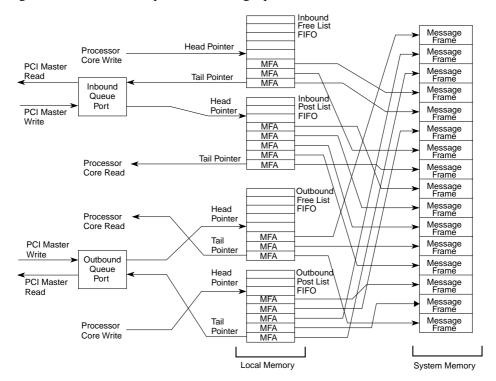

| 9.3.3               | FIFO Descriptions                                  | 9-6            |

| 9.3.3.1             | Inbound FIFOs                                      | 9-7            |

| 9.3.3.1.1           | Inbound Free_List FIFO                             | 9-8            |

| 9.3.3.1.2           | Inbound Post_List FIFO                             | 9-8            |

| 9.3.3.2             | Outbound FIFOs                                     | 9-8            |

| 9.3.3.2.1           | Outbound Free_List FIFO                            | 9-8            |

| 9.3.3.2.2           | Outbound Post_List FIFO                            |                |

| 9.3.4               | I <sub>2</sub> O Register Descriptions             |                |

| 9.3.4.1             | PCI-Accessible I <sub>2</sub> O Registers          |                |

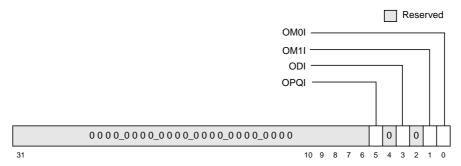

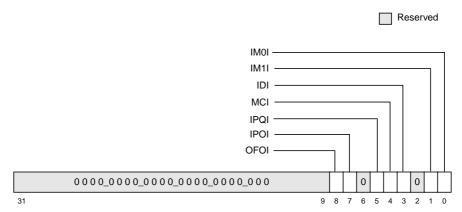

| 9.3.4.1.1           | Outbound Message Interrupt Status Register (OMISR) |                |

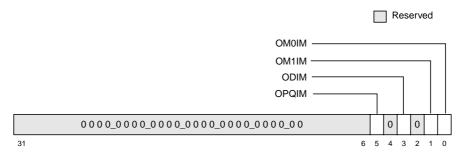

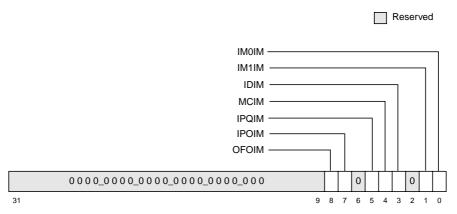

| 9.3.4.1.2           | Outbound Message Interrupt Mask Register (OMIMR)   |                |

| 9.3.4.1.3           | Inbound FIFO Queue Port Register (IFQPR)           |                |

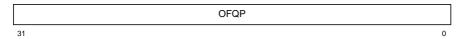

| 9.3.4.1.4           | Outbound FIFO Queue Port Register (OFQPR)          |                |

| 9.3.4.2             | Processor-Accessible I <sub>2</sub> O Registers    |                |

| 9.3.4.2.1           | Inbound Message Interrupt Status Register (IMISR)  |                |

| 9.3.4.2.2           | Inbound Message Interrupt Mask Register (IMIMR)    |                |

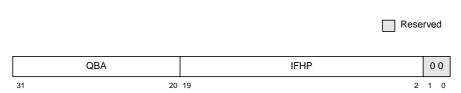

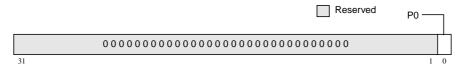

| 9.3.4.2.3           | Inbound Free_FIFO Head Pointer Register (IFHPR)    |                |

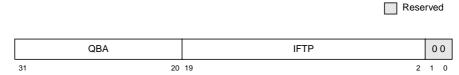

| 9.3.4.2.4           | Inbound Free_FIFO Tail Pointer Register (IFTPR)    |                |

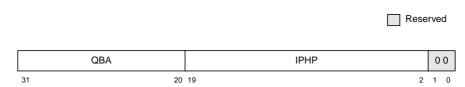

| 9.3.4.2.5           | Inbound Post_FIFO Head Pointer Register (IPHPR)    | 9-16           |

| Paragraph<br>Number | Title                                                | Page<br>Number |

|---------------------|------------------------------------------------------|----------------|

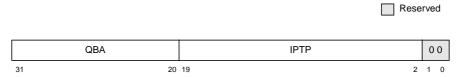

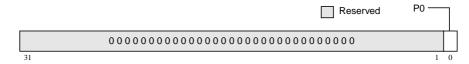

| 9.3.4.2.6           | Inbound Post_FIFO Tail Pointer Register (IPTPR)      | 9-17           |

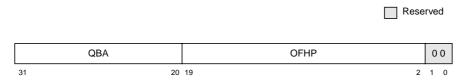

| 9.3.4.2.7           | Outbound Free_FIFO Head Pointer Register (OFHPR)     |                |

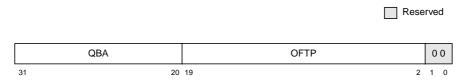

| 9.3.4.2.8           | Outbound Free_FIFO Tail Pointer Register (OFTPR)     |                |

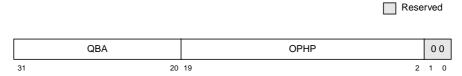

| 9.3.4.2.9           | Outbound Post_FIFO Head Pointer Register (OPHPR)     |                |

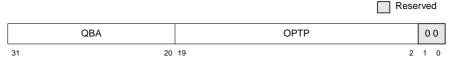

| 9.3.4.2.10          | Outbound Post_FIFO Tail Pointer Register (OPTPR)     |                |

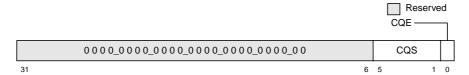

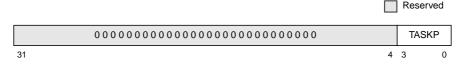

| 9.3.4.2.11          | Messaging Unit Control Register (MUCR)               |                |

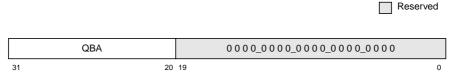

| 9.3.4.2.12          | Queue Base Address Register (QBAR)                   |                |

|                     | Chapter 10<br>I <sup>2</sup> C Interface             |                |

| 10.1                | I <sup>2</sup> C Interface Overview                  | 10-1           |

| 10.1.1              | I <sup>2</sup> C Unit Features                       | 10-1           |

| 10.1.2              | I <sup>2</sup> C Interface Signal Summary            | 10-2           |

| 10.1.3              | I <sup>2</sup> C Register Summary                    |                |

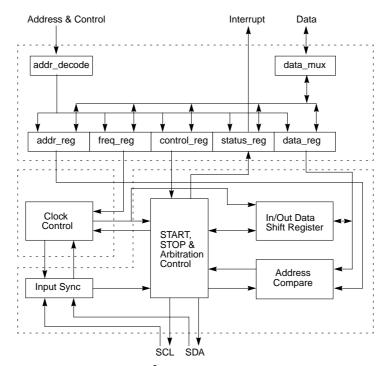

| 10.1.4              | I <sup>2</sup> C Block Diagram                       |                |

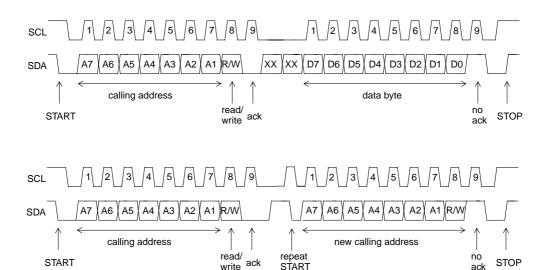

| 10.2                | I <sup>2</sup> C Protocol                            | 10-3           |

| 10.2.1              | START Condition                                      | 10-4           |

| 10.2.2              | Slave Address Transmission                           | 10-4           |

| 10.2.3              | Data Transfer                                        |                |

| 10.2.4              | Repeated START Condition                             | 10-5           |

| 10.2.5              | STOP Condition                                       |                |

| 10.2.6              | Arbitration Procedure                                |                |

| 10.2.7              | Clock Synchronization                                |                |

| 10.2.8              | Handshaking                                          |                |

| 10.2.9              | Clock Stretching                                     |                |

| 10.3                | I <sup>2</sup> C Register Descriptions               | 10-7           |

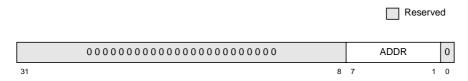

| 10.3.1              | I <sup>2</sup> C Address Register (I2CADR)           |                |

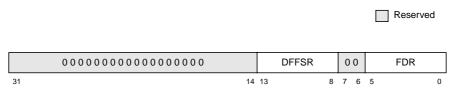

| 10.3.2              | I <sup>2</sup> C Frequency Divider Register (I2CFDR) | 10-8           |

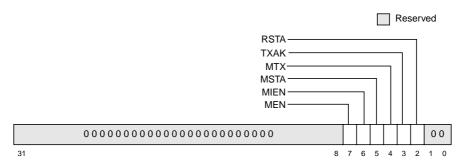

| 10.3.3              | I <sup>2</sup> C Control Register (I2CCR)            | 10-10          |

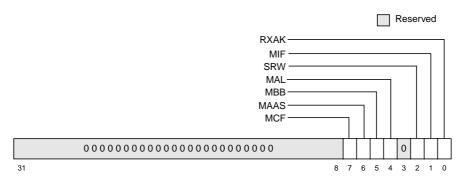

| 10.3.4              | I <sup>2</sup> C Status Register (I2CSR)             | 10-11          |

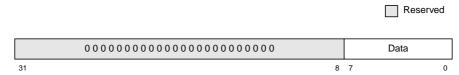

| 10.3.5              | I <sup>2</sup> C Data Register (I2CDR)               | 10-13          |

| 10.4                | Programming Guidelines                               |                |

| 10.4.1              | Initialization Sequence                              |                |

| 10.4.2              | Generation of START                                  |                |

| 10.4.3              | Post-Transfer Software Response                      |                |

| 10.4.4              | Generation of STOP                                   |                |

| 10.4.5              | Generation of Repeated START                         |                |

| 10.4.6              | Generation of SCK when SDA Low                       |                |

| 10.4.7              | Slave Mode Interrupt Service Routine                 |                |

| 10.4.7.1            | Slave Transmitter and Received Acknowledge           |                |

| 10.4.7.2            | Loss of Arbitration and Forcing of Slave Mode        |                |

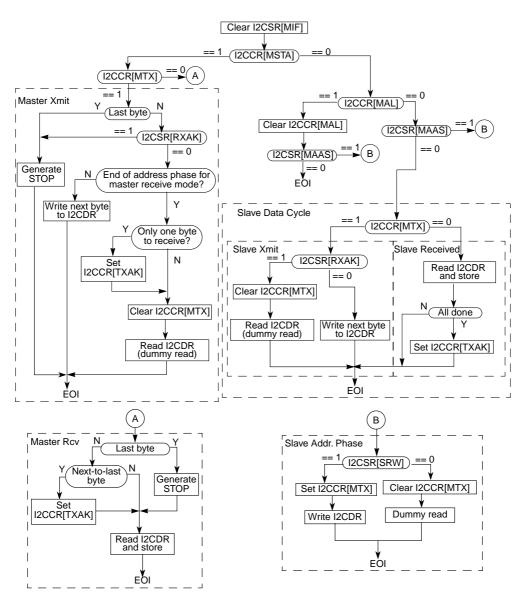

| 10.4.8              | Interrupt Service Routine Flowchart                  | 10-16          |

#### **CONTENTS**

| Paragraph | Title | Page   |

|-----------|-------|--------|

| Number    | Title | Number |

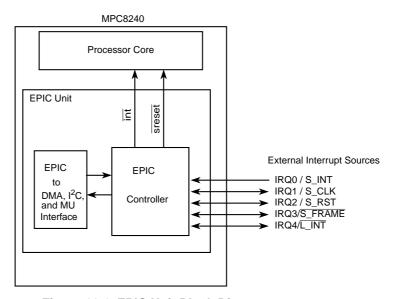

# Chapter 11 Embedded Programmable Interrupt Controller (EPIC) Unit

| 11.1     | EPIC Unit Overview                                                       |

|----------|--------------------------------------------------------------------------|

| 11.1.1   | EPIC Features Summary                                                    |

| 11.1.2   | EPIC Interface Signal Description                                        |

| 11.1.3   | EPIC Block Diagram                                                       |

| 11.2     | EPIC Register Summary                                                    |

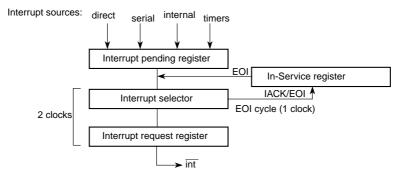

| 11.3     | EPIC Unit Interrupt Protocol                                             |

| 11.3.1   | Interrupt Source Priority                                                |

| 11.3.2   | Processor Current Task Priority                                          |

| 11.3.3   | Interrupt Acknowledge 11-8                                               |

| 11.3.4   | Nesting of Interrupts                                                    |

| 11.3.5   | Spurious Vector Generation                                               |

| 11.3.6   | Internal Block Diagram Description                                       |

| 11.3.6.1 | Interrupt Pending Register (IPR)—Non-programmable 11-9                   |

| 11.3.6.2 | Interrupt Selector (IS)                                                  |

| 11.3.6.3 | Interrupt Request Register (IRR)                                         |

| 11.3.6.4 | In-Service Register (ISR)                                                |

| 11.4     | EPIC Pass-Through Mode                                                   |

| 11.5     | EPIC Direct Interrupt Mode                                               |

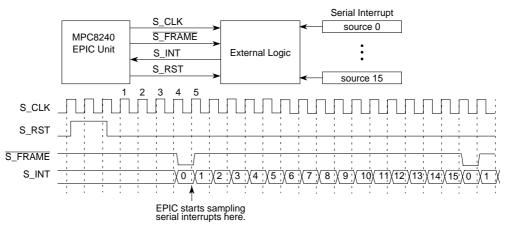

| 11.6     | EPIC Serial Interrupt Interface                                          |

| 11.6.1   | Sampling of Serial Interrupts                                            |

| 11.6.2   | Serial Interrupt Timing Protocol                                         |

| 11.6.3   | Edge/Level Sensitivity of Serial Interrupts                              |

| 11.7     | EPIC Timers                                                              |

| 11.8     | Programming Guidelines                                                   |

| 11.9     | Register Definitions                                                     |

| 11.9.1   | Feature Reporting Register (FRR)                                         |

| 11.9.2   | Global Configuration Register (GCR)                                      |

| 11.9.3   | EPIC Interrupt Configuration Register (EICR)                             |

| 11.9.4   | EPIC Vendor Identification Register (EVI)                                |

| 11.9.5   | Processor Initialization Register (PI)                                   |

| 11.9.6   | Spurious Vector Register (SVR)                                           |

| 11.9.7   | Global Timer Registers                                                   |

| 11.9.7.1 | Timer Frequency Reporting Register (TFRR)                                |

| 11.9.7.2 | Global Timer Current Count Registers (GTCCRs)                            |

| 11.9.7.3 | Global Timer Base Count Registers (GTBCRs)                               |

| 11.9.7.4 | Global Timer Vector/Priority Registers (GTVPRs)                          |

| 11.9.7.5 | Global Timer Destination Registers (GTDRs)                               |

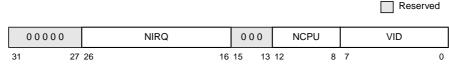

| 11.9.8   | External (Direct and Serial), and Internal Interrupt Registers 11-24     |

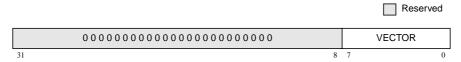

| 11.9.8.1 | Direct & Serial Interrupt Vector/Priority Registers (IVPRs, SVPRs) 11-24 |

| 11.9.8.2 | Direct & Serial Interrupt Destination Registers (IDRs, SDRs)             |

|          |                                                                          |

| Paragraph<br>Number                                                                                                                                                                        | Title Page Number                                                                                                                                                                                        |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

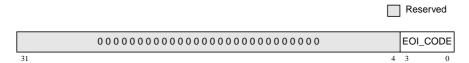

| 11.9.8.3<br>11.9.8.4<br>11.9.9<br>11.9.9.1<br>11.9.9.2<br>11.9.10                                                                                                                          | Internal (I <sup>2</sup> C, DMA, MU) Interrupt Vector/Priority Registers (IIVPRs) 11-26 Internal (I <sup>2</sup> C, DMA or MU) Interrupt Destination Registers (IIDRs) 11-26 Processor-Related Registers |  |

|                                                                                                                                                                                            | Chapter 12<br>Central Control Unit                                                                                                                                                                       |  |

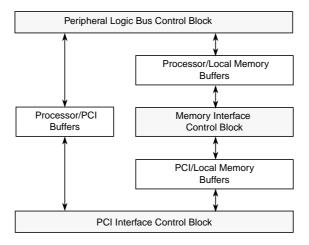

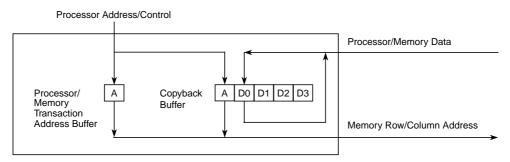

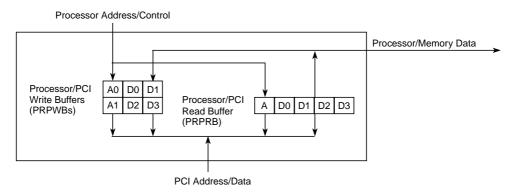

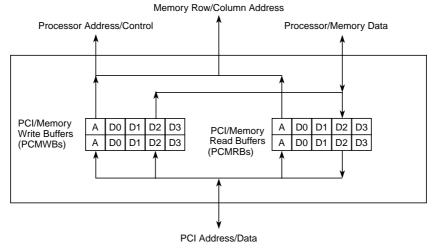

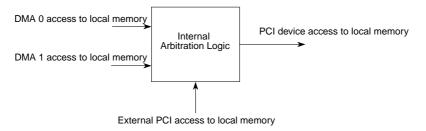

| 12.1<br>12.1.1<br>12.1.2<br>12.1.2.1<br>12.1.2.2<br>12.1.3<br>12.1.3.1<br>12.1.3.1.2<br>12.1.3.2<br>12.1.3.2<br>12.2.1<br>12.2.1.1<br>12.2.1.2<br>12.2.1.3<br>12.2.1.4<br>12.2.2<br>12.2.3 | Internal Buffers                                                                                                                                                                                         |  |

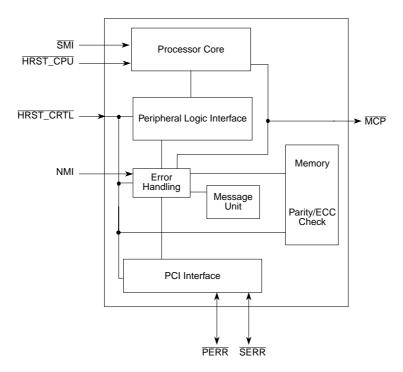

| Chapter 13<br>Error Handling                                                                                                                                                               |                                                                                                                                                                                                          |  |

| 13.1<br>13.1.1<br>13.1.2<br>13.2<br>13.2.1<br>13.2.2<br>13.2.3<br>13.2.3.1<br>13.2.3.2<br>13.2.3.3                                                                                         | Overview                                                                                                                                                                                                 |  |

| Paragraph<br>Number | Title                                      | Page<br>Number |

|---------------------|--------------------------------------------|----------------|

| 13.3                | Error Reporting                            | 13-5           |

| 13.3.1              | Processor Interface Errors                 | 13-6           |

| 13.3.1.1            | Processor Transaction Error                | 13-6           |

| 13.3.1.2            | Flash Write Error                          | 13-7           |

| 13.3.1.3            | Processor Write Parity Error               | 13-7           |

| 13.3.2              | Memory Interface Errors                    | 13-7           |

| 13.3.2.1            | Memory Read Data Parity Error              | 13-8           |

| 13.3.2.2            | Memory ECC Error                           | 13-8           |

| 13.3.2.3            | Memory Select Error                        |                |

| 13.3.2.4            | Memory Refresh Overflow Error              | 13-9           |

| 13.3.3              | PCI Interface Errors                       | 13-9           |

| 13.3.3.1            | PCI Address Parity Error                   | 13-9           |

| 13.3.3.2            | PCI Data Parity Error                      | 13-10          |

| 13.3.3.3            | PCI Master-Abort Transaction Termination   | 13-10          |

| 13.3.3.4            | Received PCI Target-Abort Error            | 13-10          |

| 13.3.3.5            | NMI (Nonmaskable Interrupt)                |                |

| 13.3.4              | Message Unit Error Events                  |                |

| 13.4                | Exception Latencies                        | 13-11          |

|                     | Chapter 14 Power Management                |                |

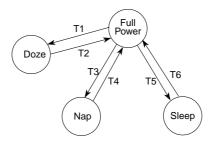

| 14.1                | Overview                                   |                |

| 14.2                | Processor Core Power Management            |                |

| 14.2.1              | Dynamic Power Management                   |                |

| 14.2.2              | Programmable Power Modes on Processor Core |                |

| 14.2.3              | Processor Power Management Modes—Details   |                |

| 14.2.3.1            | Full-Power Mode with DPM Disabled          |                |

| 14.2.3.2            | Full-Power Mode with DPM Enabled           |                |

| 14.2.3.3            | Processor Doze Mode                        |                |

| 14.2.3.4            | Processor Nap Mode                         |                |

| 14.2.3.5            | Processor Sleep Mode                       |                |

| 14.2.4              | Power Management Software Considerations   |                |

| 14.3                | Peripheral Logic Power Management          |                |

| 14.3.1              | MPC8240 Peripheral Power Mode Transitions  |                |

| 14.3.2              | Peripheral Power Management Modes          |                |

| 14.3.2.1            | Peripheral Logic Full Power Mode           |                |

| 14.3.2.2            | Peripheral Logic Doze Mode                 |                |

| 14.3.2.3            | Peripheral Logic Nap Mode                  |                |

| 14.3.2.3.1          | PCI Transactions During Nap Mode           |                |

| 14.3.2.3.2          | PLL Operation During Nap Mode              |                |

| 14.3.2.4            | Peripheral Logic Sleep Mode                | 14-10          |

| Paragraph<br>Number | Title                                            | Page<br>Number |

|---------------------|--------------------------------------------------|----------------|

| 14.3.2.4.1          | System Memory Refresh during Sleep Mode          | 14-11          |

| 14.3.2.4.2          | Disabling the PLL during Sleep Mode              |                |

| 14.3.2.4.3          | SDRAM Paging during Sleep Mode                   | 14-11          |

| 14.4                | Example Code Sequence for Entering Processor     |                |

|                     | and Peripheral Logic Sleep Modes                 | 14-11          |

|                     | Chapter 15                                       |                |

|                     | Debug Features                                   |                |

| 15.1                | Debug Register Summary                           |                |

| 15.2                | Address Attribute Signals                        |                |

| 15.2.1              | Memory Address Attribute Signals (MAA[0:2])      |                |

| 15.2.2              | Memory Address Attribute Signal Timing           |                |

| 15.2.3              | PCI Address Attribute Signals                    |                |

| 15.2.4              | PCI Address Attribute Signal Timing              |                |

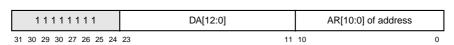

| 15.3                | Memory Debug Address                             |                |

| 15.3.1              | Enabling Debug Address                           |                |

| 15.3.2              | Debug Address Signal Definitions                 |                |

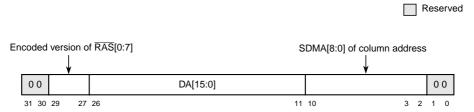

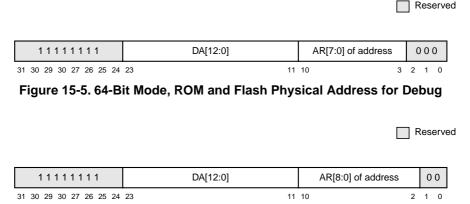

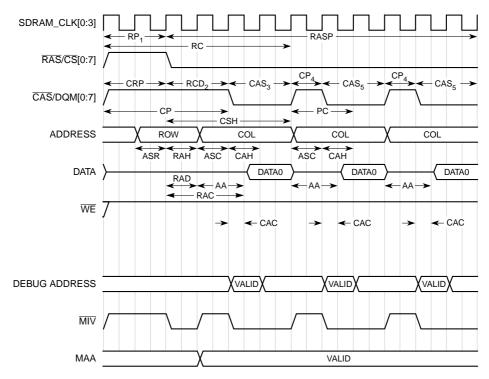

| 15.3.3              | Physical Address Mappings                        | 15-6           |

| 15.3.4              | RAS Encoding                                     |                |

| 15.3.5              | Debug Address Timing                             |                |

| 15.4                | Memory Interface Valid (MIV)                     |                |

| 15.4.1              | MIV Signal Timing                                |                |

| 15.5                | Memory Data Path Error Injection/Capture         |                |

| 15.5.1              | Memory Data Path Error Injection Mask Registers  |                |

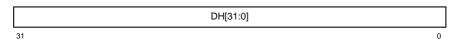

| 15.5.1.1            | DH Error Injection Mask Register                 |                |

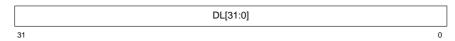

| 15.5.1.2            | DL Error Injection Mask Register                 |                |

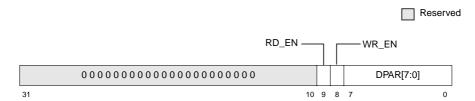

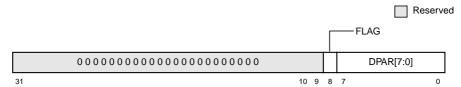

| 15.5.1.3            | Parity Error Injection Mask Register             |                |

| 15.5.2              | Memory Data Path Error Capture Monitor Registers |                |

| 15.5.2.1            | DH Error Capture Monitor Register                |                |

| 15.5.2.2            | DL Error Capture Monitor Register                |                |

| 15.5.2.3            | Parity Error Capture Monitor Register            |                |

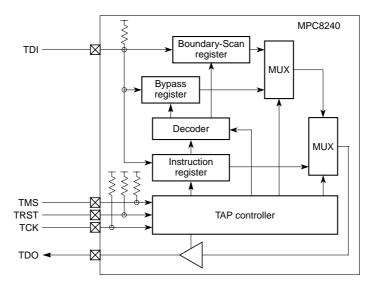

| 15.6                | JTAG/Testing Support                             |                |

| 15.6.1              | JTAG Signals                                     |                |

| 15.6.2              | JTAG Registers and Scan Chains                   | 15-22          |

| 15.6.2.1            | Bypass Register                                  |                |

| 15.6.2.2            | Boundary-Scan Registers                          |                |

| 15.6.2.3            | Instruction Register                             | 15-22          |

| 15.6.2.4            | TAP Controller                                   | 15-22          |

| Paragraph<br>Number                                                  | Title                                                                                                                                                                                                                                                        | Page<br>Number   |  |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|

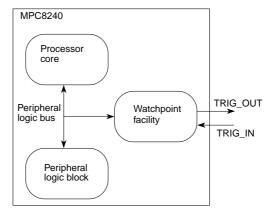

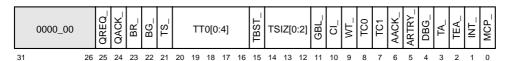

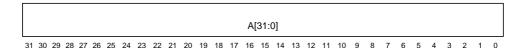

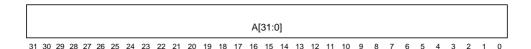

| Chapter 16 Programmable I/O and Watchpoint                           |                                                                                                                                                                                                                                                              |                  |  |

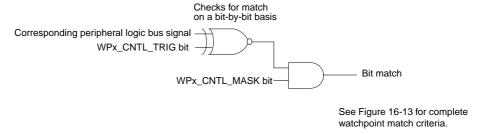

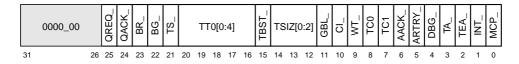

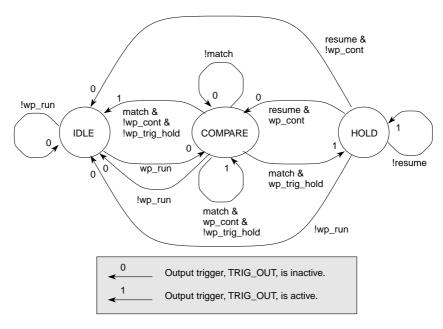

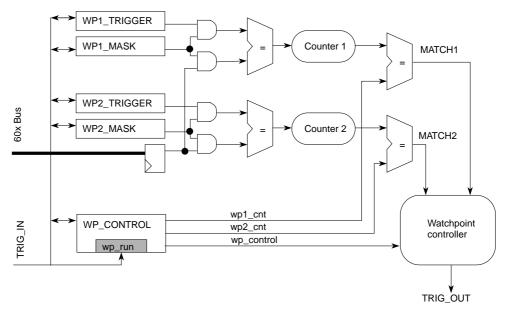

| 16.1<br>16.2<br>16.2.1<br>16.2.2<br>16.2.3<br>16.2.4<br>16.3<br>16.4 | Watchpoint Interface Signal Description  Watchpoint Registers  Watchpoint Register Address Map  Watchpoint Trigger Registers  Watchpoint Mask Registers  Watchpoint Control Register (WP_CONTROL)  State and Block Diagrams  Watchpoint Trigger Applications |                  |  |

| Appendix A<br>Address Map A                                          |                                                                                                                                                                                                                                                              |                  |  |