M68331BCC/D

October 1993

# M68331BCC BUSINESS CARD COMPUTER USER'S MANUAL

© MOTOROLA, INC., 1993; All Rights Reserved

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

CPU32Bug is a trademark of Motorola Inc.

White Knight is a trademark of FreeSoft Company.

MacTerminal, Apple, and Macintosh are trademarks of Apple Computer, Inc.

IBM-PC is a registered trademark of International Business Machines Corporation.

The computer program stored in the read only memory of the device contains material copyrighted by Motorola Inc., first published in 1989, and may be used only under a license such as the License For Computer programs (Article 14) contained in Motorola Terms and Conditions of Sale, Rev. 1/79.

### TABLE OF CONTENTS

# TABLE OF CONTENTS

### **CHAPTER 1 GENERAL INFORMATION**

| 1.1 | Introduction                                              | 1-1  |  |  |  |  |  |  |

|-----|-----------------------------------------------------------|------|--|--|--|--|--|--|

| 1.2 | Features1-                                                |      |  |  |  |  |  |  |

| 1.3 | Specifications                                            |      |  |  |  |  |  |  |

| 1.4 | General Description                                       |      |  |  |  |  |  |  |

| 1.5 | Equipment Required                                        | 1-4  |  |  |  |  |  |  |

|     | CHAPTER 2 HARDWARE PREPARATION AND INSTALLA               | ΓΙΟΝ |  |  |  |  |  |  |

| 2.1 | Introduction                                              | 2-1  |  |  |  |  |  |  |

| 2.2 | Unpacking Instructions                                    | 2-1  |  |  |  |  |  |  |

| 2.3 | Hardware Preparation                                      | 2-1  |  |  |  |  |  |  |

| 2.  | 3.1 RAM Chip Enable Select Header (J2)                    | 2-5  |  |  |  |  |  |  |

| 2.  | 3.3 EPROM Chip Select Header (J3)                         | 2-6  |  |  |  |  |  |  |

| 2.  | 3.4 TxD Select Header (J4)                                | 2-7  |  |  |  |  |  |  |

| 2.  | 3.5 RxD Select Header (J5)                                | 2-8  |  |  |  |  |  |  |

| 2.  | 3.6 Clock Input Select Header (J6)                        | 2-9  |  |  |  |  |  |  |

|     | Installation Instructions                                 |      |  |  |  |  |  |  |

|     | 4.1 Power Supply - BCC Interconnection                    |      |  |  |  |  |  |  |

|     | 4.2 Terminal - BCC Interconnection                        |      |  |  |  |  |  |  |

| 2.  | 4.3 Target System - BCC Interconnection                   | 2-14 |  |  |  |  |  |  |

|     | CHAPTER 3 OPERATING INSTRUCTIONS                          |      |  |  |  |  |  |  |

| 3.1 | Introduction                                              | 3-1  |  |  |  |  |  |  |

| 3.2 | Limitations                                               |      |  |  |  |  |  |  |

| 3.  | 2.1 Chip Select Usage                                     |      |  |  |  |  |  |  |

|     | 2.2 Other MCU Resources Used by CPU32Bug                  |      |  |  |  |  |  |  |

|     | Operating Procedure                                       |      |  |  |  |  |  |  |

|     | Monitor Description                                       |      |  |  |  |  |  |  |

|     | 4.1 Memory and Register Display and Modification Commands |      |  |  |  |  |  |  |

|     | 4.2 Breakpoint Capabilities                               |      |  |  |  |  |  |  |

|     | 4.3 System Calls                                          |      |  |  |  |  |  |  |

| 3.  | 4.4 Diagnostic Monitor                                    | 3-10 |  |  |  |  |  |  |

TABLE OF CONTENTS

# **CHAPTER 3 OPERATING INSTRUCTIONS (continued)**

| 3.5                               | 3.5 Assembling/Disassembling Procedure          |                                          |      |  |  |  |

|-----------------------------------|-------------------------------------------------|------------------------------------------|------|--|--|--|

| 3.6                               |                                                 |                                          |      |  |  |  |

|                                   | 3.6.1 Apple Macintosh (with MacTerminal) to BCC |                                          |      |  |  |  |

|                                   | 3.6.2 Ap                                        | ple Macintosh (with White Knight) to BCC | 3-19 |  |  |  |

| 3.6.3 IBM-PC (with KERMIT) to BCC |                                                 |                                          |      |  |  |  |

|                                   | 3.6.4 IB                                        | M-PC (with PROCOMM) to BCC               | 3-22 |  |  |  |

|                                   |                                                 | CHAPTER 4 FUNCTIONAL DESCRIPTION         |      |  |  |  |

| 4.1                               | Introduct                                       | ion                                      | 4-1  |  |  |  |

| 4.2                               | BCC Des                                         | cription                                 | 4-1  |  |  |  |

|                                   | 4.2.1 MC                                        | CU                                       |      |  |  |  |

|                                   | 4.2.1.1                                         | 32-Bit Central Processor Unit            | 4-3  |  |  |  |

|                                   | 4.2.1.2                                         | General-Purpose Timer (GPT)              | 4-3  |  |  |  |

|                                   | 4.2.1.3                                         | Queued Serial Module                     | 4-4  |  |  |  |

|                                   | 4.2.1.4                                         | External Bus Interface                   | 4-4  |  |  |  |

|                                   | 4.2.1.5                                         | Chip Selects                             | 4-4  |  |  |  |

|                                   | 4.2.1.6                                         | System Clock                             | 4-4  |  |  |  |

|                                   | 4.2.1.7                                         | Test Module                              | 4-5  |  |  |  |

|                                   | 4.2.2 Us                                        | er Memory                                | 4-5  |  |  |  |

|                                   | 4.2.3 Te                                        | rminal and Host Computer I/O Port        | 4-5  |  |  |  |

|                                   | 4.2.4 Ba                                        | ckground Mode Interface Port             | 4-5  |  |  |  |

|                                   |                                                 | CHAPTER 5 SUPPORT INFORMATION            |      |  |  |  |

| 5.1                               | Introduct                                       | ion                                      | 5-1  |  |  |  |

| 5.2                               |                                                 | or Signal Descriptions                   |      |  |  |  |

### APPENDIX A S-RECORD INFORMATION

**Figure**

# Freescale Semiconductor, Inc.

TABLE OF CONTENTS

**Page**

# LIST OF ILLUSTRATIONS

| 2-1 | BCC Jumper Header and Connector Location Diagram          | 2-2  |

|-----|-----------------------------------------------------------|------|

| 2-2 | BCC to DB-9 Cable Schematic Diagram                       |      |

| 2-3 | BCC to DB-25 Cable Schematic Diagram                      |      |

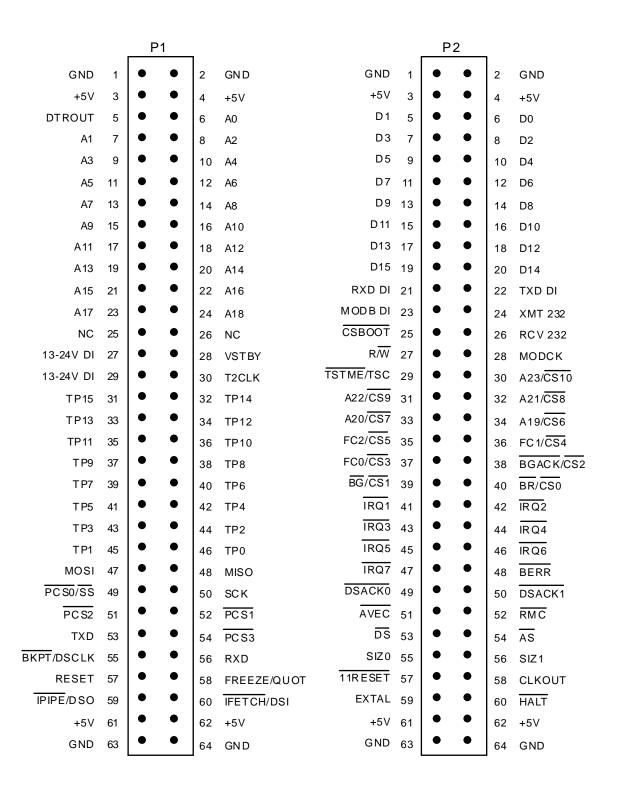

| 2-4 | Expansion Connectors Pin Assignments                      | 2-15 |

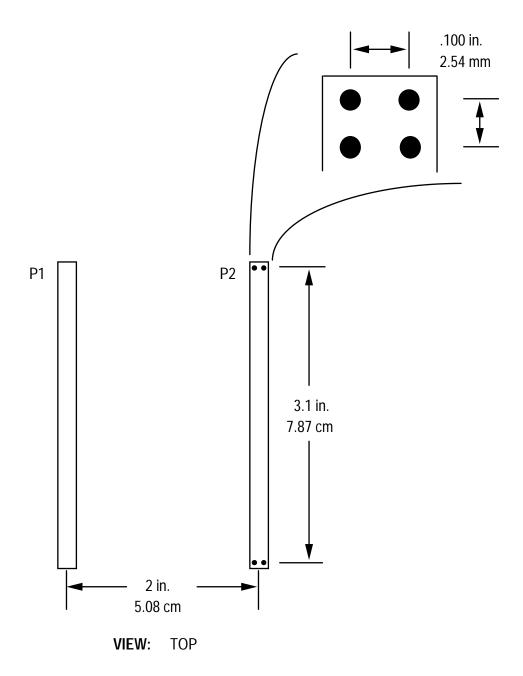

| 2-5 | Target System Expansion Connector Installation Dimensions | 2-16 |

| 4-1 | BCC Block Diagram                                         |      |

| 4-2 | =                                                         |      |

|     | LIST OF TABLES                                            |      |

| Tab | le                                                        | Page |

| 1-1 | BCC Specifications                                        | 1-2  |

| 1-2 | External Equipment Requirements                           |      |

| 2-1 | Jumper Header Types                                       |      |

| 2-2 | Jumper Header Summary                                     |      |

| 3-1 | BCC Rev. B Chip Selection Summary                         | 3-2  |

| 3-2 | BCC Rev. C Chip Selection Summary                         | 3-3  |

| 3-3 | CPU32Bug Exception Vectors                                | 3-4  |

| 5-1 | P1 Expansion Connector Pin Assignments                    | 5-1  |

| 5-2 | P2 Expansion Connector Pin Assignments                    | 5-5  |

| 5-3 | J8 Background Mode Connector Pin Assignments              |      |

| 5-4 | J9 RS-232C Serial Communication Connector Pin Assignments | 5-9  |

TABLE OF CONTENTS

**GENERAL INFORMATION**

# CHAPTER 1 GENERAL INFORMATION

### 1.1 INTRODUCTION

This manual provides general information, hardware preparation, installation instructions, functional description, and support information for the M68331BCC Business Card Computer (hereafter referred as BCC). Appendix A contains BCC downloading S-record information.

### 1.2 FEATURES

The BCC is a single-board computer complete with these features:

- MC68331 Microcontroller Unit (MCU)

- 64k x 16 bit, two erasable programmable read only memories (EPROMs). Programmed into the BCC EPROMs is the M68CPU32BUG Debug Monitor. Refer to the M68CPU32BUG Debug Monitor User's Manual, M68CPU32BUG/AD1.

- 32k x 16 bit, byte addressable random access memory (RAM)

- RS-232C compatible terminal/host computer input/output (I/O) port

- Background mode interface port

- EVS expansion connectors

- 2.25 x 3.875 in. (5.7 x 9.84 cm) PCB

The BCC can be used as a stand-alone evaluation module or can be connected directly to a target system. The BCC is primarily intended to be used with a terminal or host computer. When using a host computer, a user must have a terminal emulation package for BCC downloading operations.

**GENERAL INFORMATION**

# 1.3 SPECIFICATIONS

Table 1-1 lists the BCC specifications.

**Table 1-1. BCC Specifications**

| CHARACTERISTICS                                 | SPECIFICATIONS                                                                         |

|-------------------------------------------------|----------------------------------------------------------------------------------------|

| Internal Clock<br>External Clock                | 32.768 kHz<br>25 kHz to 50 kHz <sup>(1)</sup>                                          |

| Memory<br>32k x 16 RAM<br>64k x 16 EPROM        | 85ns (3 clock bus cycle access @ 16.7 MHz) 200ns (5 clock bus cycle access @ 16.7 MHz) |

| Terminal/Host I/O Port                          | RS-232C compatible (with internal DC-DC converters for +/-10 volts, 10 mA)             |

| Temperature Operating Storage Relative humidity | +25° C<br>-40 to +85° C<br>0 to 90% (non-condensing)                                   |

| Power Requirements Power Supply Battery Backup  | +5 Vdc @ 200 milliamps (min.)<br>+3 Vdc @ 50 microamps (min.)                          |

| Dimensions                                      | 2.25 x 3.875 in. (5.7 x 9.84 cm)                                                       |

An optional high frequency clock source (as high as 16.77 MHz) may be used if MODCK (P2, pin 28) is pulled to a logic low level. A hybrid oscillator is recommended as the external clock.

**GENERAL INFORMATION**

### 1.4 GENERAL DESCRIPTION

Using the BCC, the user can design, debug, and evaluate MC68331 Microcontroller Unit (MCU) based target systems. The BCC simplifies user evaluation of prototype hardware/software products. The BCC requires a user-supplied power supply and an RS-232C compatible terminal for functional operation.

The BCC can operate as a standalone single board computer, or as a well-defined core in larger applications. Mounted on the BCC is a microcontroller, on-board memory, and a serial level converter circuit.

Two 64-pin expansion connectors provide access to the MC68331 pins. Background mode operation and RS-232C serial communication are available through the 64-pin expansion connectors. Additional connectors also provide background mode operation and RS-232C serial communication. See Chapter 5 for interface connector pin assignments.

The BCC is factory tested and shipped with factory installed jumpers. These jumpers allow the user to customize the BCC functionality when special design considerations are required.

The M68CPU32BUG Debug Monitor (CPU32Bug) is programmed into the BCC EPROMs. CPU32Bug is a software evaluation and debug tool which may be used to develop systems built around the MCU. Using the debug monitor, the user interacts with the BCC through pre-defined monitor commands which are entered at the terminal/host computer keyboard. These commands perform functions such as modification of memory, modification of MCU internal registers, program execution under various levels of control, and access to various I/O peripherals in the MCU itself.

To program the BCC EPROMs you must remove the EPROMs and use an EPROM programmer.

**GENERAL INFORMATION**

# 1.5 EQUIPMENT REQUIRED

Table 1-2 lists the external equipment requirements for BCC operation.

### **Table 1-2. External Equipment Requirements**

### **EXTERNAL EQUIPMENT**

A terminal or host computer (RS-232C compatible) with a terminal emulation package (PCKERMIT, PROCOMM, MacTerminal, White Knight, etc.)<sup>(1)</sup>

RS-232C serial communication cable for the terminal or host computer<sup>(2)</sup>.

+5 Vdc at 200 mA power supply(2)

- 1. Refer to Chapter 3 for details on downloading using a host computer with terminal emulation package.

- 2. Refer to Chapter 2 for details.

Semiconductor, Inc.

# Freescale Semiconductor, Inc.

HARDWARE PREPARATION AND INSTALLATION

### **CHAPTER 2**

### HARDWARE PREPARATION AND INSTALLATION

### 2.1 INTRODUCTION

This chapter provides unpacking instructions, hardware preparation, and installation instructions for the BCC prior to target system installation. This description ensures the BCC is properly configured for target system operation.

### 2.2 UNPACKING INSTRUCTIONS

Unpack the BCC from shipping carton. Refer to the packing list and verify that all items are present. Save packing material for storing and shipping the BCC.

### NOTE

If the product arrives damaged, save all packing material, and contact the carrier's agent.

### 2.3 HARDWARE PREPARATION

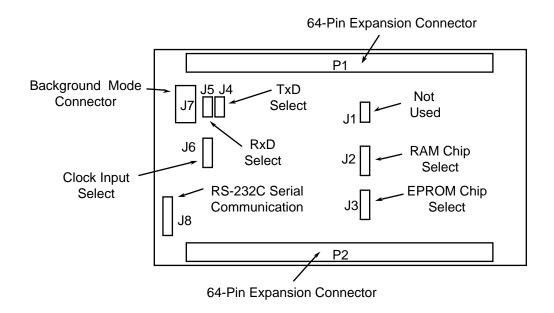

This portion of text describes the inspection and preparation of the BCC prior to installation and ensures the proper configuration for target system operation. The BCC was factory tested and shipped with factory-installed jumpers (Figure 2-1 shows jumper header and connector locations). These jumper headers allow the user to customize BCC functionality. Table 2-1 is a description of the BCC jumper header types, and Table 2-2 is a summary of the BCC jumper headers.

### **CAUTIONS**

Use caution when handling the BCC; the signals are not buffered so the BCC is sensitive to static discharge.

Depending on the application, it may be necessary to cut wiring trace shorts (cut-trace shorts) on the PCB. Be careful not to cut adjacent PCB wiring traces.

Figure 2-1. BCC Jumper Header and Connector Location Diagram

HARDWARE PREPARATION AND INSTALLATION

Table 2-1. Jumper Header Types

| Jumper Header<br>Type <sup>(1)</sup> | Symbol | Description                                                                                                                                                                          |

|--------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| three-pin with jumper                |        | Three-pin jumper header with jumper and designated as JX (X = the jumper header number). To change the factory jumper header configuration, move the jumper to the two desired pins. |

| two-pin with jumper                  |        | Two-pin jumper header with jumper, designated as JX (X = the jumper header number).                                                                                                  |

1. J7 and J8 are designated as jumper headers but they are in fact connectors.

**Table 2-2. Jumper Header Summary**

| Jumper<br>Header  | Туре   | Description                                                                                                                                                                   |  |

|-------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| J1 <sup>(1)</sup> | 2<br>1 | Not used on the M68331BCC.                                                                                                                                                    |  |

| J2 <sup>(1)</sup> | 3 2 1  | Jumper between pins 1 and 2 (factory default); enables the on-board RAM chips (U1 & U3).                                                                                      |  |

|                   | 1      | Jumper between pins 2 and 3; disables the on-board RAM chips. This allows the chip select to be used with off-board memory.                                                   |  |

| J3 <sup>(1)</sup> | 3 2 1  | Jumper between pins 1 and 2 (factory default); enables the on-board EPROM at U2.                                                                                              |  |

|                   | 1      | Jumper between pins 2 and 3; disables the on-board EPROM at U2. This allows the chip select to be used to boot from off-board memory.                                         |  |

| J4(1)             | 2<br>1 | Jumper between pins 1 and 2 (factory default); connects the on-board transmit data serial communication drivers to the MC68331 MCU device.                                    |  |

|                   |        | No jumper; disconnects the on-board transmit data serial communication drivers from the MC68331 MCU device. This allows connection of the MCU serial port to off board logic. |  |

1. These jumper headers are shorted by a trace on the solder side of the PCB (between the pins), as shown in the schematics. Cut the trace when using the optional feature provided by the jumper.

HARDWARE PREPARATION AND INSTALLATION

**Table 2-1. Jumper Header Summary (continued)**

| Jumper<br>Header  | Туре                                            | Description                                                                                                                                                                  |  |

|-------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| J5 <sup>(1)</sup> | 2<br>1                                          | Jumper between pins 1 and 2 (factory default); connects the on-board receive data serial communication drivers to the MC68331 MCU device.                                    |  |

|                   |                                                 | No jumper; disconnects the on-board receive data serial communication drivers from the MC68331 MCU device. This allows connection of the MCU serial port to off board logic. |  |

| J6 <sup>(1)</sup> | 3 2                                             | Jumper between pins 1 and 2; selects an external clock source for the MC68331 MCU device.                                                                                    |  |

|                   |                                                 | Jumper between pins 2 and 3 (factory default); selects the on-board oscillator as the MC68331 MCU device clock source.                                                       |  |

| J7                | 10<br>8<br>6<br>4<br>2<br>9<br>7<br>5<br>3<br>1 | 10-pin background mode connector.                                                                                                                                            |  |

| J8                | 4<br>3<br>2<br>1                                | 4-pin RS-232C serial connector.                                                                                                                                              |  |

1. These jumper headers are shorted by a trace on the solder side of the PCB (between the pins), as shown in the schematics. Cut the trace when using the optional feature provided by the jumper.

Semiconductor, Inc

# 2.3.1 RAM Chip Enable Select Header (J2)

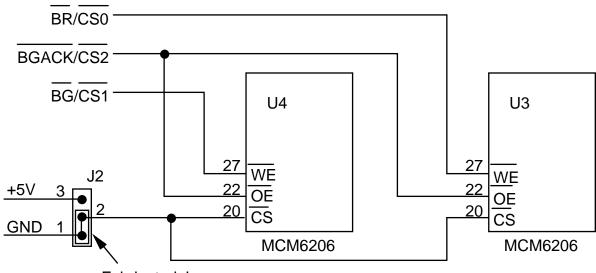

Use the three-pin jumper header J2 (shown below) to enable/disable selection of the on-board RAM. The BCC is shipped from the factory with the RAM chip select connected to GND via a cut-trace short on the bottom of the BCC PCB between pins 1 and 2. A fabricated jumper is also installed between pins 1 and 2. The cut-trace short or a fabricated jumper between pins 1 and 2 enables the BCC on-board RAM.

**Fabricated Jumper**

To disable the RAM from the BCC memory map, cut the trace on the solder side of the board on J2, between pins 1 and 2, and move the fabricated jumper to pins 2 and 3. This jumper disables selection of the on-board RAM by connecting chip enable to +5V. The chip selects are now free for other uses. Refer to the BCC schematic diagram for more detail on RAM chip select signal wiring.

### **CAUTION**

Do not connect the jumper between pins 2 and 3 before removing the cut-trace short between pins 1 and 2. Installing the jumper before the cut-trace short is removed connects +5Vdc to ground. If +5Vdc is shorted to ground the BCC or power supply may be damaged.

### **NOTE**

If the cut-trace short on jumper header J2 is cut, the fabricated jumper must be reinstalled on J2, pins 1 and 2 to return the BCC to its default setting.

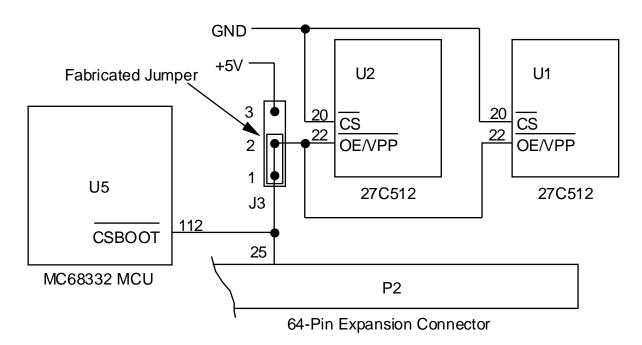

### 2.3.2 EPROM Chip Select Header (J3)

When BCC power is applied or reset occurs, the MC68331 MCU device resets itself and downloads the program in EPROM (U1 & U2). The EPROM contains the boot program. Use the three-pin jumper header J3 (shown below) to disable the BCC on-board EPROM. The BCC is shipped from the factory with the EPROM connected to the MCU bootstrap chip select pin (CSBOOT) via a cut-trace short on the bottom of the BCC PCB between pins 1 and 2. A fabricated jumper is also installed between pins 1 and 2. To boot from a program stored in memory located in the target system, cut this trace, move the jumper to pins 2 and 3, and connect CSBOOT to the target system via P2, pin 25. Cutting the cut-trace short and moving the fabricated jumper to pins 2 and 3, removes U1 & U2 from the BCC memory map. Refer to the BCC schematic diagram for more detail on CSBOOT signal wiring.

### **CAUTION**

Do not connect the jumper between pins 2 and 3 before removing the cut-trace short between pins 1 and 2. Installing the jumper before the cut-trace short is removed connects +5 Vdc to  $(\overline{\text{CSBOOT}})$ . If +5 Vdc is shorted to  $(\overline{\text{CSBOOT}})$  the MCU may be damaged.

### NOTE

If the cut-trace short on jumper header J3 is cut, the fabricated jumper must be reinstalled on J3 pins 1 and 2 to return the BCC to its default setting.

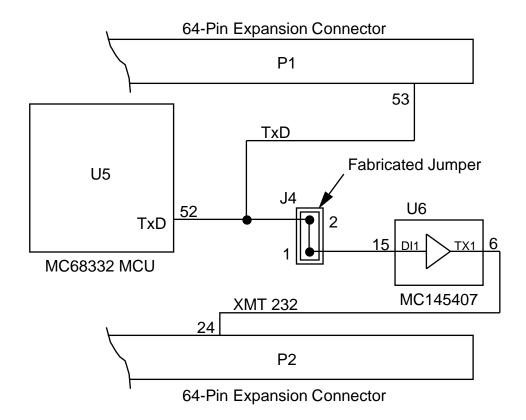

### 2.3.3 TxD Select Header (J4)

Jumper header J4 allows the user to disconnect the transmit TxD serial data pin of the MC68331 MCU device (U5) from the RS-232C receiver/driver (U6) and use a target system receiver/driver. The BCC is shipped from the factory with the receiver/driver connected to MCU TxD (pin 52) via a cut-trace short on the bottom of the BCC PCB between J4, pins 1 and 2 (shown below). A fabricated jumper is also installed on pins 1 and 2. To disconnect the serial pin of the MCU, cut this trace and remove the jumper.

### **NOTE**

If the cut-trace short on jumper header J4 is cut, the fabricated jumper must be reinstalled on J4 to return the BCC to its default setting.

Refer to the BCC schematic diagram for more detail on TxD signal wiring.

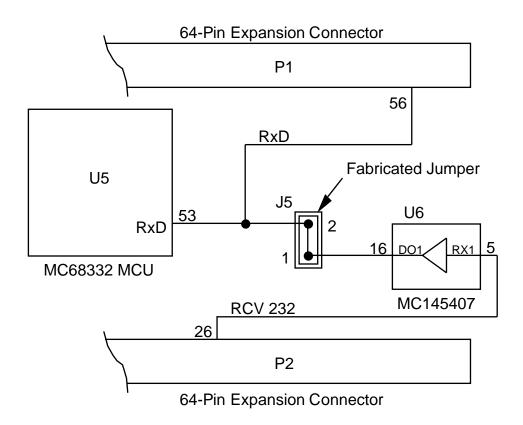

### 2.3.4 RxD Select Header (J5)

Jumper header allows the user to disconnect the receive RxD serial data pin of the MC68331 MCU device (U5) from the RS-232C receiver/driver (U6) and use a target system receiver/driver. The BCC is shipped from the factory with receiver/driver connected to MCU RxD via a cut-trace short on the bottom of the BCC PCB between J5, pins 1 and 2 (shown below). A fabricated jumper is also installed on pins 1 and 2. To disconnect the RxD pin of the MCU, cut this trace and remove the jumper.

### **NOTE**

If the cut-trace short on jumper header J5 is cut, the fabricated jumper must be reinstalled on J5 to return the BCC to its default setting.

Refer to the BCC schematic diagram for more detail on RxD signal wiring.

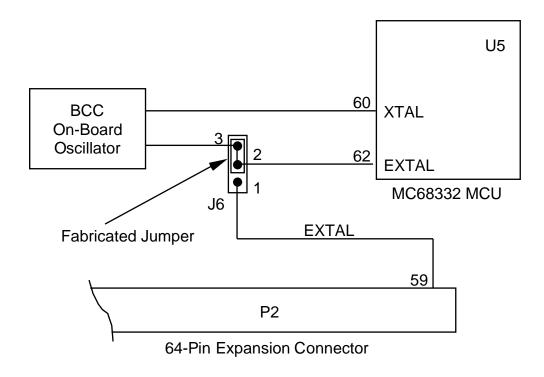

Use the three-pin jumper header J6 (shown below) to select the BCC on-board clock source or an external clock source. The BCC on-board clock source is a 32 kHz crystal, which is frequency multiplied by the MC68331 to a programmable operating frequency. The BCC is shipped with the on-board crystal selected as the clock source. J6 has a cut-trace short on the bottom of the BCC PCB between pins 2 and 3. A fabricated jumper is also supplied, but is not required when the user uses the on-board clock source. Refer to the BCC schematic diagram for more detail on EXTAL signal wiring.

HARDWARE PREPARATION AND INSTALLATION

An optional high frequency oscillator (0 to 16.77 MHz) may be used if MODCK (connector P2, pin 28) is pulled to a logic low level. To use the target-system, external-source CMOS clock; follow these steps:

- a. Turn off power to the BCC.

- b. Cut the printed circuit trace on the bottom of the BCC between pins 2 and 3.

- c. Move the fabricated jumper between pins 2 and 3 to pins 1 and 2.

- d. Supply an external oscillator to connector P2, pin 59 (EXTAL).

- e. Ground connector P2, pin 28 (MODCK).

- f. Apply power to the BCC, start the external oscillator, and drive connector P1, pin 57 (RESET), low.

### **NOTES**

If the cut-trace short on jumper header J6 is cut, the fabricated jumper must be reinstalled on J6 pins 2 and 3 to return the BCC to its default setting.

Use a hybrid oscillator when driving the MCU from an external source.

Any change in the MC68331 MCU device clock speed causes a corresponding change in the SCI baud rate. The operational speed of the MCU is determined by the clock and the synthesizer control register value (SYNCR). The SCI baud rate is then set based on this system clock frequency. If changes are made to the MCU speed and the terminal baud rate is not changed appropriately, terminal communication will fail. Refer to Appendix C of the M68CPU32BUG Debug Monitor User's Manual, M68CPU32BUG/AD1.

Semiconductor, Inc

# 2.4 INSTALLATION INSTRUCTIONS

# A user supplied power supply and RS-232C compatible terminal are required for BCC operation.

An RS-232C compatible host computer, with terminal emulation package, may be connected to the BCC for S-record downloading.

### 2.4.1 **Power Supply - BCC Interconnection**

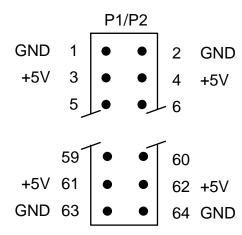

The BCC requires +5 Vdc @ 200 mA (max.) for operation. Use 18 to 20 AWG wire to connect a user supplied power supply to the BCC. This connection is made via expansion connector P1 or P2.

There are two preferred methods for connecting the power supply to the BCC: wire-wrap and crimp-to-wire. When using the crimp-to-wire method, fabricate two wires (+5Vdc and GND) as follows:

- a. Trim back 18 20 AWG wire approximately 0.25 inch.

- b. Attach a crimp-to-wire receptacle (Dupont 46227-0000) to the wire using a crimping tool.

- c. Place heat shrink tubing (Digi-Key W183-ND) on the crimp-to-wire receptacle and shrink using a heat source.

Connect the power supply ground fabricated wire to pin 1, 2, 63, or 64 of P1 or P2. Connect the power supply +5 Vdc fabricated wire to pin 3, 4, 61, or 62 of P1 or P2 (as shown below).

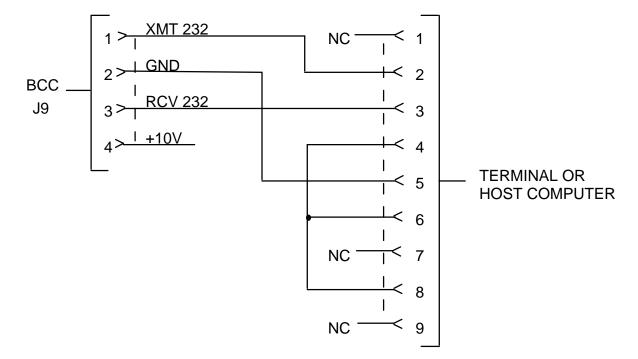

### 2.4.2 Terminal - BCC Interconnection

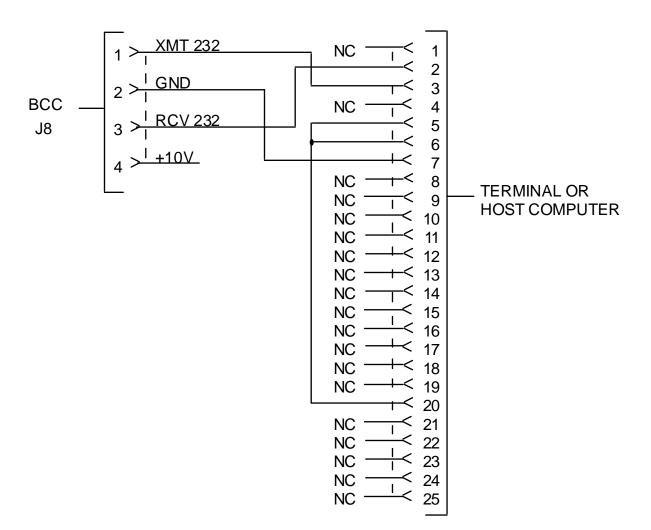

Interconnection of an RS-232C compatible terminal to the BCC is accomplished via a user supplied 9- or 25-conductor cable assembly as shown in Figures 2-2 and 2-3. If the user's terminal/host computer has a DB-9 connector refer to Figure 2-2. If the user's terminal/host computer has a DB-25 connector refer to Figure 2-3. One end of the cable assembly connects to the BCC connector J9 (shown below). The other end of the cable assembly connects to the user supplied terminal or host computer. For connector pin assignments and signal descriptions of BCC terminal port connector J9, refer to Chapter 5.

Figure 2-2. BCC to DB-9 Cable Schematic Diagram

Figure 2-3. BCC to DB-25 Cable Schematic Diagram

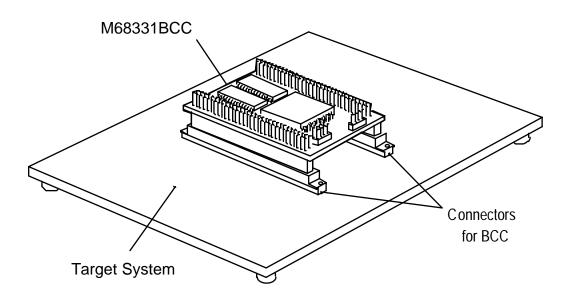

### 2.4.3 Target System - BCC Interconnection

For target system to BCC interconnection the BCC mounts on the target system as shown below. This configuration is used to evaluate the user's hardware design. The 64-pin expansion connectors provide access to most of the MC68331 MCU device pins. Figure 2-4 illustrates the expansion header pin assignments for the BCC. Physical dimension requirements for installing the BCC on a target system are illustrated in Figure 2-5.

**Target System to BCC Interconnection**

Figure 2-4. Expansion Connectors Pin Assignments

Figure 2-5. Target System Expansion Connector Installation Dimensions

Semiconductor, Inc.

OPERATING INSTRUCTIONS

# CHAPTER 3 OPERATING INSTRUCTIONS

### 3.1 INTRODUCTION

The EPROMs on the BCC contain the M68CPU32BUG debug monitor program (hereafter referred to as CPU32Bug). CPU32Bug is a software tool for evaluating and debugging systems built around the MC68331 MCU. CPU32Bug allows loading, debugging, and executing of user programs. Various CPU32Bug routines that handle I/O, data conversion, timer, and string functions are available to user programs through system calls. For a detailed description of the CPU32Bug functions, refer to M68CPU32BUG Debug Monitor User's Manual, M68CPU32BUG/AD1.

### CPU32Bug consists of:

- Memory and register display and modification commands

- Breakpoint capabilities

- System calls

- Diagnostic commands

- A single-line assembler/disassembler

There are two modes of operation in the CPU32Bug monitor; the debugger mode and the diagnostic mode. When the user is in the debugger directory the prompt **CPU32Bug>** appears, and the user has access to the debugger commands (refer to paragraph 3.4). When the user is in the diagnostic mode the prompt **CPU32Diag>** appears, and the user has access to the diagnostic commands (refer to paragraph 3.4.4). These modes are also called directories.

CPU32Bug is command-driven and performs various operations in response to user commands entered at the keyboard. CPU32Bug executes entered commands; upon completion the prompt reappears. However, if a command is entered which causes execution of user target code (i.e., GO), control may or may not return to CPU32Bug. This depends upon the user program function. Entering the help (**HE**) command provides a list of all possible commands and their structure.

### 3.2 LIMITATIONS

CPU32Bug requires some system resources to operate properly: chip selects, level 7 interrupt, software watchdog timer, periodic interrupt timer, and system exception vectors.

**OPERATING INSTRUCTIONS**

### 3.2.1 Chip Select Usage

The MC68331 MCU has chip select signals that enable peripheral devices. The BCC requires some of these chip selects for BCC operation making them unavailable to the user. Do not remove the chip selects used by the BCC, or CPU32Bug will not operate. In addition to the chip selects employed on the BCC, other chip selects are used when the BCC is installed on the M68331EVK (refer to Tables 3-1 and 3-2).

Depending on the user's environment, any or all of the chip selects may be re-configured for an alternate function (i.e., as I/O or address lines). Chip select pins used by the BCC and EVK cannot be used in their alternate capacities.

Although a chip select (CS4 on Rev. B and Rev. C BCCs) is dedicated for the ABORT switch, the pin is not used. Instead the chip select decodes the interrupt acknowledge (IACK) cycle in response to a level 7 interrupt generated by the ABORT switch. Refer the System Integration Module User's Manual (SIM32UM/AD) for more information.

When the BCC is not mounted on the M68300PFB Platform Board (PFB), these chip selects are available to the user. Also if the PFB RAM/EPROM socket pairs (U1/U3, U2/U4) and coprocessor socket U5 are not populated, the chip selects are available to the user.

Table 3-1. BCC Rev. B<sup>(1)</sup> Chip Selection Summary

| Signal | Board/Chip        | Description                                                            | Memory Type |

|--------|-------------------|------------------------------------------------------------------------|-------------|

| CSBOOT | BCC U2            | CPU32Bug EPROM                                                         |             |

| CS0    | BCC U1            | write enable for MSB=UPPER=EVEN                                        | RAM         |

| CS1    | BCC U3            | write enable for LSB=LOWER=ODD                                         | RAM         |

| CS2    | BCC U3/U1         | read enable for MSB/LSB=BOTH                                           | RAM         |

| CS3    | <unused></unused> |                                                                        |             |

| CS4    | PFB               | ABORT push-button autovector                                           |             |

| CS5    | PFB U5            | chip enable for MC68881/882. cut/-jump U5-J3 from CS2 to CS5 required. |             |

| CS6    | PFB U2            | read enable for LSB=LOWER=ODD RAM/EPROM                                |             |

| CS7    | PFB U4            | read enable for MSB=UPPER=EVEN RAM/EPROM                               |             |

| CS8    | PFB U1/U3         | read enable for MSB/LSB=BOTH RAM                                       |             |

| CS9    | PFB U1            | write enable for LSB=LOWER=ODD RAM                                     |             |

| CS10   | PFB U3            | write enable for MSB=UPPER=EVEN RAM                                    |             |

<sup>(1)</sup> There is no Rev. A for the M68331BCC board.

**OPERATING INSTRUCTIONS**

Table 3-2. BCC Rev. C Chip Selection Summary

| Signal | Board/Chip        | Description Memor                                                          |     |  |

|--------|-------------------|----------------------------------------------------------------------------|-----|--|

| CSBOOT | BCC U3            | CPU32Bug EPROM for MSB=UPPER=EVEN                                          |     |  |

| CSBOOT | BCC U4            | CPU32Bug EPROM for LSB=LOWER=ODD                                           |     |  |

| CS0    | BCC U1            | write enable for MSB=UPPER=EVEN                                            | RAM |  |

| CS1    | BCC U2            | write enable for LSB=LOWER=ODD                                             | RAM |  |

| CS2    | BCC U3/U1         | read enable for MSB/LSB=BOTH                                               | RAM |  |

| CS3    | <unused></unused> |                                                                            |     |  |

| CS4    | PFB               | ABORT push-button autovector                                               |     |  |

| CS5    | PFB U5            | chip enable for MC68881/882. cut/-jump U5-<br>J3 from CS2 to CS5 required. |     |  |

| CS6    | PFB U2            | read enable for LSB=LOWER=ODD RAM/EPRON                                    |     |  |

| CS7    | PFB U4            | read enable for MSB=UPPER=EVEN RAM/EPROM                                   |     |  |

| CS8    | PFB U1/U3         | read enable for MSB/LSB=BOTH RAM                                           |     |  |

| CS9    | PFB U1            | write enable for LSB=LOWER=ODD RAM                                         |     |  |

| CS10   | PFB U3            | write enable for MSB=UPPER=EVEN RAM                                        |     |  |

### 3.2.2 Other MCU Resources Used by CPU32Bug

Avoid writing the value zero to bit 7 of the port F pin assignment register (PFPAR); such a value disables the ABORT switch.

The software watchdog timer is disabled via a write-once register (SYPCR) during power-up or reset, so the software watchdog timer cannot be used or re-enabled by the user unless the user modifies the SYPCR\_OR and SYPCR\_AND parameters. Modification of the SYPCR\_OR and SYPCR\_AND parameters is detailed in Appendix C of the M68CPU32BUG Debug Monitor User's Manual, M68CPU32BUG/AD1.

The monitor uses the system exception vectors, so they are unavailable to the BCC user. The monitor debug exception vectors are listed in Table 3-3. The associated debugger facilities (breakpoints, trace mode, etc.) will not operate if the vector offsets in the target program vector table are changed.

**OPERATING INSTRUCTIONS**

Table 3-3. CPU32Bug Exception Vectors

| Vector<br>Number | Offset | Exception         | CPU32Bug Commands                                                                            |

|------------------|--------|-------------------|----------------------------------------------------------------------------------------------|

| 4                | \$10   | Illegal           | Instruction breakpoints (Used by GO, GN, GT)                                                 |

| 9                | \$24   | Trace             | T, TC, TT                                                                                    |

| 31               | \$7C   | Level 7 interrupt | ABORT switch                                                                                 |

| 47               | \$BC   | TRAP #15          | System calls (see Chapter 5 of the M68CPU32BUG Debug Monitor User's Manual, M68CPU32BUG/AD1) |

| 66               | \$108  | User Defined      | Timer Trap #15 Calls (\$4X)                                                                  |

Any change in the MC68331 MCU device clock speed causes a corresponding change in the SCI baud rate. The operational speed of the MCU is determined by the clock and the synthesizer control register value (SYNCR) or by an external clock signal applied to the EXTAL pin of the MCU. The SCI baud rate is then set based on this system clock frequency. If changes are made to the MCU system clock frequency, changes must be made to the customization parameter area (FCRYSTAL or FEXTAL) so the correct baud rate can be calculated for SCI communications by CPU32Bug. See the M68CPU32BUG Debug Monitor User's Manual (M68CPU32BUG/AD1), Appendix C for details.

Additionally, CPU32Bug writes a one (1) to the module mapping (MM) bit of the module control register (MCR). This configures the register block to start at address \$FFF000. As the MM bit is a write-once bit, the user cannot clear it to move the register block to low memory (\$7FF000). The user can move the register block by modifying the MCR\_AND parameter detailed in Appendix C of the M68CPU32BUG Debug Monitor User's Manual, M68CPU32BUG/AD1.

**OPERATING INSTRUCTIONS**

### 3.3 OPERATING PROCEDURE

A Power On Reset (POR) occurs when power is applied to the BCC. This POR condition resets the MCU and user I/O port circuitry. After a POR occurs, processing control passes to the monitor program. All MC68331 registers are set to their reset state during monitor power-up.

The input serial format for the BCC terminal I/O port must be configured for 8 data bits, 1 stop bit, no parity, and 9600 baud.

The terminal then displays this message:

```

CPU32Bug Debugger/Diagnostics - Version X.XX (C) Copyright 1989, 1990 by Motorola Inc. CPU32Bug>

```

where:

eescale Semiconductor, Inc

X.XX is the software revision level

After initialization or return of control to the monitor, the terminal displays the prompt "CPU32Bug>" and waits for a response. If an incorrect response is entered, the terminal displays "Invalid command" followed by the prompt "CPU32Bug>".

CPU32Bug waits for a command line input from the user terminal. When a proper command is entered, the operation continues in one of two basic modes. If the command causes execution of a user program, the monitor may or may not be reentered, depending upon the desire of the user. For the alternate case, the command is executed under the control of the monitor, and the system returns to a waiting condition after the command is completed. During command execution, additional user input may be required, depending on the command function.

The user can use any of the commands supported by the monitor. A standard input routine controls the BCC operation while the user types a command line. Command processing begins only after the command line has been terminated by pressing the keyboard carriage return <CR> key.

OPERATING INSTRUCTIONS

### 3.4 MONITOR DESCRIPTION

CPU32Bug performs various operations in response to user commands entered at the keyboard. When the debugger prompt **CPU32Bug>** appears on the terminal screen, the debugger is ready to accept commands.

As the command line is entered it is stored in an internal buffer. Execution begins only after the carriage return is entered. This lets the user correct entry errors using the control characters described in the M68CPU32BUG Debug Monitor User's Manual, M68CPU32BUG/AD1.

After the debugger executes a command it returns with the **CPU32Bug>** prompt. However, if the entered command causes execution of user target code, (i.e., **GO**), then control may or may not return to the debugger. This depends on the user program function. For example, if a breakpoint is specified, control returns to the debugger when the breakpoint is encountered during user program execution. The user program also returns control to the debugger by means of the TRAP #15 system call function, **.RETURN**.

Included as part of the CPU32Bug firmware is a single-line assembler/disassembler function. The assembler is an interactive assembler/editor in which source programs are not saved. Each source line is translated into MC68331 MCU machine language code and stored line-by-line into memory as it is entered. In order to display an instruction, the machine code is disassembled and the instruction mnemonic and operands are displayed. All valid MC68331 MCU instructions are supported.

The CPU32Bug assembler is effectively a subset of the M68000 Family Structured Assembler (M68MASM). It has some limitations as compared with the M68MASM assembler, such as not allowing line numbers and labels; however, it is a useful tool for creating, modifying, and debugging MC68331 MCU code.

# Freescale Semiconductor, Inc.

**OPERATING INSTRUCTIONS**

### 3.4.1 Memory and Register Display and Modification Commands

Various commands are available to the user for displaying and modifying memory. For more information, refer to Chapter 3 of the M68CPU32BUG Debug Monitor User's Manual, M68CPU32BUG/AD1. The memory display and modification commands are:

- **BF** (block of memory fill) fills the specified range of memory with a data pattern.

- **BM** (block of memory move) copies the contents of the memory addresses defined by <RANGE> to another place in memory, beginning at <ADDR>.

- **BS** (block of memory search) searches the specified range of memory for a match with a user-entered data pattern.

- **BV** (block of memory verify) compares the specified range of memory against a data pattern.

- MD (memory display) displays the contents of multiple memory locations.

- **MM** (memory modify) examines and changes memory locations.

- MS (memory set) writes data to memory starting at a specified address.

- **RD** (register display) displays the contents of the MCU registers.

- **RM** (register modify) examines and changes register contents.

- **RS** (register set) writes data to a specified register.

### 3.4.2 Breakpoint Capabilities

A breakpoint lets the user set a target code instruction address stopping point for debugging purposes. Target code execution halts when a breakpoint is encountered. For more information on breakpoints, refer to Chapter 3 of the M68CPU32BUG Debug Monitor User's Manual, M68CPU32BUG/AD1. The breakpoint commands are:

- **BR/NOBR** (breakpoint insert/delete) allows the user to set/remove a target code instruction address as a breakpoint address for debugging purposes.

- **GD** (go direct) starts target code execution and ignores breakpoints.

- **GN** (go to temporary breakpoint) sets a temporary breakpoint at the address of the next instruction, that is, the one following the current instruction.

- **GT** (go to temporary breakpoint) sets a temporary breakpoint at the current instruction and starts target code execution.

- **TT** (trace to temporary breakpoint) sets a temporary breakpoint at a specified address and traces until encountering a breakpoint.

Semiconductor, Inc

# Freescale Semiconductor, Inc.

OPERATING INSTRUCTIONS

### 3.4.3 **System Calls**

The CPU32Bug TRAP #15 handler allows system calls from user programs. A system call accesses selected functional routines contained in CPU32Bug, including input and output routines. TRAP #15 also transfers control to CPU32Bug at the end of a user program. For more information on system calls, refer to Chapter 5 of the M68CPU32BUG Debug Monitor User's Manual, M68CPU32BUG/AD1. System calls include:

- **.INCHR** (input character) reads a character from the default input port.

- **.INSTAT** (input serial port status) checks for characters in the default input port buffer.

- **.INLN** (input line (pointer/pointer format)) reads a line from the default input port.

- .READSTR (input string (pointer/count format)) reads a string of characters from the default input port into a buffer.

- .READLN (input line (pointer/count format)) reads a string of characters from the default input port.

- .CHKBRK (check for break) returns zero (0) status in condition code register if break status is detected at the default input port.

- **.OUTCHR** (output character) outputs a character to the default output port.

- **.OUTSTR** (output string in pointer/pointer format) outputs a string of characters to the default output port.

- .OUTLN (output line in pointer/pointer format) outputs a character strings followed by a carriage return (**CR**>) and a line feed (**LF**>) sequence.

- .WRITE (output string in pointer/count format) formats character strings with a count byte and outputs the string to the default output port. After formatting, the count byte is the first byte in the string.

- .WRITELN (output line in pointer/count format) formats character strings with a count byte and outputs the string to the default output port. After formatting, the count byte is the first byte in the string.

- .PCRLF (output carriage return and line feed) sends a <CR> and a <LF> sequence to the default output port.

- **.ERASLN** (erase line) erases the line at the present cursor position.

- .WRITD (output string with data in pointer/count format) uses the monitor I/O routine which outputs a user string containing embedded variable fields. The user passes the starting address of the string and the data stack address containing the data which is inserted into the string. The output goes to the default output port.

**OPERATING INSTRUCTIONS**

- **.WRITDLN** (output line with data in pointer/count format) uses the monitor I/O routine which outputs a user string containing embedded variable fields. The user passes the starting address of the string and the data stack address containing the data which is inserted into the string. The output goes to the default output port.

- .SNDBRK (send break) sends a break to the default output port.

- .TM\_INI (timer initialization) initializes the MC68331 MCU device periodic interrupt timer.

- .TM STR0 (start timer at T=0) resets the timer to zero and starts it.

- .TM RD (read timer) reads the timer count.

- .DELAY (timer delay) generates timing delays.

- **.RETURN** (return to CPU32Bug) returns control to CPU32Bug from the target program.

- **.BINDEC** (convert binary to Binary Coded Decimal) calculates the BCD equivalent of a specified binary number.

- .CHANGEV (parse value) parses value in user specified buffer.

- **.STRCMP** (compare two strings in pointer/count format) compares equality and returns a Boolean flag to the caller.

- **.MULU32** (multiply two 32-bit unsigned integers) multiplies two 32-bit unsigned integers and returns the product on the stack as a 32-bit unsigned integer.

- **.DIVU32** (divide two 32-bit unsigned integers) divides two 32-bit unsigned integers and returns the quotient on the stack as a 32-bit unsigned integer.

Semiconductor, Inc

# Freescale Semiconductor, Inc.

**OPERATING INSTRUCTIONS**

### 3.4.4 Diagnostic Monitor

The diagnostic monitor is a series of self-tests for the MC68331 MCU device. The diagnostic monitor is programmed into the BCC EPROM. For more information on the diagnostic monitor, refer to Chapter 6 of the M68CPU32BUG Debug Monitor User's Manual, M68CPU32BUG/AD1. The diagnostic monitor commands are:

- **HE** (help) command displays a menu of the top level directory.

- ST (self test) command executes self-test diagnostics.

- **SD** (switch directories) command toggles between the CPU32Bug directory and the CPU32Diag directory.

- LE (loop-on-error) endlessly repeats a test at the point where an error is detected.

- **SE** (Stop-On-Error) halts a test at the point where an error is detected.

- LC (loop-continue) endlessly repeats a test or series of tests.

- **NV** (non-verbose)suppresses all error messages except PASSED or FAILED.

- **DE** (display error counters) displays the results of a particular test.

- **ZE** (clear error counters) resets all error counters to zero.

- **DP** (display pass count) is the number of passes in loop-continue mode. Under this command the count is displayed with other information at the conclusion of each pass.

- **ZP** (zero pass count) resets the pass counter to zero.

### Available utilities are:

- WL Write Loop

- RL Read Loop

- WR Read/Write Loop

CPU tests are a series of diagnostics provided to test the CPU portion of the MC68331 MPU:

- **CPU A** Register Test

- CPU B Instruction Test

- **CPU C** Address Mode Test

- CPU D Exception Processing Test

**OPERATING INSTRUCTIONS**

Memory tests are a series of diagnostics that verify random access memory (read/write) that may reside on the BCC.

- MT A Set Function Code

- MT B Set Start Address

- MT C Set Stop Address

- MT D Set Bus Data Width

- MT E March Address Test

- **MT F** Walk a Bit Test

- MT G Refresh Test

- MT H Random Byte Test

- **MT I** Program Test

- MT J TAS Test

Bus error test (**BERR**) tests for internal bus access time-out and internal to external bus access time-out error conditions, including:

- Bus errors when accessing the BCC RAM.

- Bus errors when reading the BCC EPROM.

- Bus errors when accessing the PFB optional memory.

- Internal bus access time-outs when reading and writing from an undefined function code/memory location internal to the MCU.

- Internal to external bus access time-outs reading or writing to an undefined function code/memory location external to the MCU.

**OPERATING INSTRUCTIONS**

#### 3.5 ASSEMBLING/DISASSEMBLING PROCEDURE

The assembler/disassembler is an interactive, one-line assembler/editor in which the source program is not saved. Each source line is converted into machine language code and is stored in memory on a line-by-line basis at the time of entry. In order to display an instruction, the machine code is disassembled and the instruction mnemonic and operands are displayed. All valid opcodes are converted to assembly language mnemonic. All invalid opcodes return a Declare Constant Word (DC.W) conversion.

The memory modify (**mm**;**di**) command lets the user create, modify, and debug MC68331 MCU code. Assembler input must have exactly one space between the mnemonic and the operand. There must be no space inside the operand field. Assembler input must be terminated by a carriage return. No comments are allowed after the instruction input and no line labels are permitted.

After each new assembler input line, the new line is disassembled for the user before stepping to the new instruction. The new line may assemble to a different number of bytes than the previous one.

For Branch if Higher or Same (BHS)/Branch if Carry Clear (BCC) mnemonics, disassembly displays the BCC mnemonic. For Branch if Lower (BLO)/Branch if Carry Set (BCS) mnemonics, disassembly displays the BCS mnemonic.

Branch address offsets are automatically calculated by the assembler, so the user should input the destination address rather than an offset value.

The assembler is terminated by entering a period (.) followed by a carriage return as the only entry on the command input line. Entering a carriage return alone on an input line steps to the next instruction.

The following pages describe how to operate the assembler/disassembler by creating a typical program loop, and debugging the program using CPU32Bug monitor commands. A typical program loop is first assembled. Routine examples then illustrate how to set a breakpoint, proceed from a breakpoint, display and modify registers, and initiate user program execution.

Semiconductor, Inc.

# Freescale Semiconductor, Inc.

**OPERATING INSTRUCTIONS**

Enter the periodic interrupt timer (PIT) time-out program starting at address \$5000:

# EXAMPLE PROGRAM

# PROGRAM DESCRIPTION

| CPU32Bı | ag>MM 5000;DI <cr></cr>               | Memory modify at location \$5000 with disassembly option. |

|---------|---------------------------------------|-----------------------------------------------------------|

| 5000    | MOVE.L #\$501C,\$78 <cr></cr>         | Set-up level six vector table.                            |

| 5008    | MOVE.L #\$061E0120,\$FFFA22 <cr></cr> | Initialize PIT.                                           |

| 5012    | LPSTOP #\$2500 <cr></cr>              | Execute LPSTOP Instruction.                               |

| 5018    | BRA.W \$5012 <cr></cr>                | Loop                                                      |

| 501C    | MOVEA.W #\$5100,A0 <cr></cr>          | Beginning of message.                                     |

| 5020    | MOVEA.W #\$510E,A1 <cr></cr>          | End of message.                                           |

| 5024    | BTST.B #\$0,\$FFFC0C <cr></cr>        | Check for SCI not busy.                                   |

| 502C    | BEQ.B \$5024 <cr></cr>                | Branch until free.                                        |

| 502E    | MOVE.B (A0)+,\$FFFC0F <cr></cr>       | Send message byte.                                        |

| 5034    | CMPA.W A0,A1 <cr></cr>                | Check for end of message.                                 |

| 5036    | BNE.W \$5024 <cr></cr>                | Branch until done.                                        |

| 503A    | RTE <cr></cr>                         | Return from print routine.                                |

Enter the ASCII code for the output message, PIT TIME-OUT. Each time this message appears when running the program, indicates the program has completed a loop. Enter the following ASCII code at memory location \$5100:

CPU32Bug>MS 5100 'PIT TIME-OUT'ODOA<CR>

*Memory modify at location \$5100.*

Semiconductor, Inc.

# Freescale Semiconductor, Inc.

**OPERATING INSTRUCTIONS**

After entering the PIT time-out program display the instructions at location \$5000

# EXAMPLE PROGRAM

# PROGRAM DESCRIPTION

CPU32Bug>MD 5000;DI<CR>

Display memory at location \$5000 with disassembly option.

|       |                                      |                                                  |          |                                          | aisassembiy opiion.                                |

|-------|--------------------------------------|--------------------------------------------------|----------|------------------------------------------|----------------------------------------------------|

| 5     | 000                                  | 21FC0000                                         | 501C0078 | MOVE.L                                   | #\$501C,(\$78).W                                   |

| 5     | 8008                                 | 23FC061E                                         | 012000FF |                                          |                                                    |

|       |                                      | FA22                                             |          | MOVE.L                                   | #\$061E0120,(\$FFFA22).L                           |

| 5     | 012                                  | F80001C0                                         | 2500     | LPSTOP.W                                 | #\$2500                                            |

| 5     | 5018                                 | 6000FFF8                                         |          | BRA.W                                    | \$5012                                             |

| 5     | 01C                                  | 307C5100                                         |          | MOVEA.W                                  | #\$5100,A0                                         |

| 5     | 020                                  | 327C510E                                         |          | MOVEA.W                                  | #\$510E,A1                                         |

| 5     | 024                                  | 08390000                                         | 00FFFC0C | BTST.B                                   | #\$0,(\$FFFC0C).L                                  |

| 5     | 02C                                  | 67F6                                             |          | BEQ.B                                    | \$5024                                             |

| _     | 1D1120D                              |                                                  |          |                                          | D. 1                                               |

| C     | PU32Bu                               | g>< <b>CR</b> >                                  |          |                                          | Display next eight instructions.                   |

|       | :P032Bu<br>502E                      | g>< <b>CR</b> > 13D800FF                         | FC0F     | MOVE.B                                   | Display next eight instructions. (A0)+,(FFFC0F).L. |

| 5     |                                      |                                                  | FC0F     | MOVE.B<br>CMPA.W                         |                                                    |

| 5     | 02E                                  | 13D800FF                                         | FC0F     |                                          | (A0)+,(FFFCOF).L.                                  |

| 5     | 502E<br>5034                         | 13D800FF<br>B2C8                                 | FC0F     | CMPA.W                                   | (A0)+,(FFFCOF).L.<br>A0,A1                         |

| 5 5 5 | 502E<br>5034<br>5036                 | 13D800FF<br>B2C8<br>6600FFEC                     | FC0F     | CMPA.W<br>BNE.W                          | (A0)+,(FFFCOF).L.<br>A0,A1                         |

| 5 5 5 | 502E<br>5034<br>5036<br>503A         | 13D800FF<br>B2C8<br>6600FFEC<br>4E73             | FC0F     | CMPA.W<br>BNE.W<br>RTE                   | (A0)+,(FFFCOF).L.<br>A0,A1<br>\$5024               |

|       | 502E<br>5034<br>5036<br>503A<br>503C | 13D800FF<br>B2C8<br>6600FFEC<br>4E73<br>0000FFFF | FC0F     | CMPA.W<br>BNE.W<br>RTE<br>ORI.B          | (A0)+,(FFFCOF).L.<br>A0,A1<br>\$5024<br>#\$FF,D0   |

|       | 502E<br>5034<br>5036<br>503A<br>503C | 13D800FF<br>B2C8<br>6600FFEC<br>4E73<br>0000FFFF | FC0F     | CMPA.W<br>BNE.W<br>RTE<br>ORI.B<br>ORI.B | (A0)+,(FFFCOF).L. A0,A1 \$5024  #\$FF,D0 #\$FF,D0  |

The message displayed on the terminal

```

CPU32Bug>MD 5100<CR>

```

00005100 5049 5420 5449 4D45 2D4F 5554 0D0A FFFF PIT TIME-OUT....

Semiconductor, Inc

## Freescale Semiconductor, Inc.

**OPERATING INSTRUCTIONS**

The following routines are performed on the preceding program loop:

## **TERMINAL**

# ROUTINE DESCRIPTION

```

Display memory at address 5000

CPU32Bug>MD 5000;DI<CR>

00005000

21FC0000 501C0078

#$501C,($78).W

MOVE.L

00005008

23FC061E 012000FF

#$061E0120, (FFFA22)

FA22

MOVE.L

00005012

F80001C0 2500

LPSTOP.W

#$2500

00005018

6000FFF8

BRA.W

$5012

0000501C

307C5100

MOVEA.W

#$5100,A0

00005020

327C510E

MOVEA.W

#$510E,A1

00005024

08390000 00FFFC0C

BTST.B

#$0,($FFFC0C).L

0000502C

67F6

BEQ.B

$5024

Modify memory at location 500C.

CPU32Bug>MM 500C<CR>

Change PIT time-out speed.

0000500C

0120? 00FF.

CPU32Bug>g 5000<CR>

Go to address 5000 and begin execution.

Effective address: 00005000

Periodic interrupt timer time-out message.

PIT TIME-OUT

PIT TIME-OUT

PIT TIME-OUT

:

```

Press the ABORT switch on the PFB to terminate the loop program.

```

Exception: ABORT

=00005018

PC

SR

=2500=TR:OFF_S_5_....

VBR

=00000000

SFC

=5=SD

DFC

=5=SD

USP

=0000FC00

SSP*

=00010000

D2

D0

=00000000

D1

=00000000

=00000000

D3

=00000000

D4

=00000000

D5

=00000000

Dб

=00000000

D7

=00000000

Α0

=0000510E

Α1

=0000510E

Α2

=00000000

Α3

=00000000

Α4

=00000000

Α5

=00000000

Аб

=00000000

Α7

=00010000

00005018

6000FFF8

BRA.W.W

$5012

Trace one instruction.

CPU32Bug>T 1<CR>

=00005018

=2500=TR:OFF_S_5_....

VBR

=00000000

SFC

=5=SD

DFC

=5=SD

USP

=0000FC00

SSP*

=00010000

D0

=00000000

D1

=00000000

D2

=00000000

D3

=00000000

=00000000

D4

=00000000

D5

Dб

=00000000

D7

=00000000

Α0

=0000510E

Α1

=0000510E

Α2

=00000000

Α3

=00000000

=00000000

Α5

=00000000

Аб

=00000000

Α7

=00010000

LPSTOP.W

00005012

2500

F80001C0

#$2500

Set breakpoint at 5034.

CPU32Bug>BR 5034<CR>

BREAKPOINTS

00005034

Go to address 5000 and begin execution.

CPU32Buq>g 5000<CR>

Effective address: 00005018

At Breakpoint

=00000000

PC

=00005034

SR

=2600=TR:OFF_S_6_....

VBR

SFC

=5=SD

DFC

=5=SD

USP

=0000FC00

SSP*

=0000FFF8

=00000000

=00000000

D1

D2

=00000000

D3

=00000000

D0

=00000000

D5

=00000000

D6

=00000000

=00000000

D4

D7

Α0

=00005101

Α1

=0000510E

Α2

=00000000

Α3

=00000000

=00000000

=00000000

=00000000

=0000FFF8

Α5

Аб

00005034

B2C8

CMPA.W

A0,A1

```

Semiconductor, Inc.

# Freescale Semiconductor, Inc.

**OPERATING INSTRUCTIONS**

#### 3.6 DOWNLOADING PROCEDURES

Downloading transfers information from a host computer to the BCC, via the load (LO) command. The procedure described below lets the user download with an IBM personal computer (PC) or Apple Macintosh host computer.

The **LO** command moves data in S-record format (see Appendix A) from an external host computer to the EVK user pseudo ROM.

Subsections 3.6.1 through 3.6.4 list instructions for downloading to the EVK from an Apple Macintosh with MacTerminal or Red Ryder, or from an IBM-PC with Kermit or PROCOMM.

**OPERATING INSTRUCTIONS**

#### 3.6.1 Apple Macintosh (with MacTerminal) to BCC

The MacTerminal downloading program serves as a terminal emulator for the Apple Macintosh computer. To download a Motorola S-record file from the Apple Macintosh computer to the BCC:

a. Select the following menu Terminal Settings:

Terminal: VT100

Mode: ANSI

Cursor Shape: Underline

Line Width: 80 Columns

Select: On Line

Auto Repeat

Click on: OK

b. Select the following menu Compatibility Settings:

Baud rate: 9600

Bits per Character: 8 Bits

Parity: None

Handshake: XOn/XOff

Connection: Another Computer

Connection Port: Modem

Click on: OK

c. Select the following menu File Transfer Settings:

**Settings for Pasting**

or Sending Text: Word Wrap Outgoing Text

File Transfer

Protocol: Text

**Settings for Saving**

Lines Off Top: Retain Line Breaks

Click on: OK

# Freescale Semiconductor, Inc.

**OPERATING INSTRUCTIONS**

- d. Apply power to the BCC.

- e. Press Apple Macintosh computer keyboard carriage return (<CR>) key to display applicable BCC monitor prompt.

- f Apple Macintosh computer displays the CPU32Bug> prompt.

- g. Enter BCC monitor download command as follows:

CPU32Bug>LO<CR>

- h. Operate pull-down File menu, and select (choose): Send File ...

- i. Use dialog box and select applicable S-record object file.

Click on: Send

Motorola S-record file is now transferred to the BCC.

#### **NOTE**

S-record file will not be displayed during the file transfer to the BCC.

The underline cursor flashes and the beeper sounds when the S-record has finished downloading. Press the carriage return twice to return to the CPU32Bug prompt:

<**CR**>

<**CR**>

CPU32Bug>

# Freescale Semiconductor, Inc.

**OPERATING INSTRUCTIONS**

#### 3.6.2 Apple Macintosh (with White Knight) to BCC

The White Knight downloading program serves as a terminal emulator for the Apple Macintosh computer. To download a Motorola S-record file from the Apple Macintosh computer to the BCC:

- a. Execute White Knight program.

- b. Set up computer program to match BCC baud rate (typically) as follows: 9600 baud, no parity, 8-bits, 1-stop bit, full duplex

- c. Apply power to BCC.

- d. Press Apple Macintosh computer keyboard carriage return (<**CR**>) key to display applicable BCC monitor prompt.

- e Enter BCC monitor download command as follows:

CPU32Bug>LO<CR>

f. Operate pull-down File menu, and select (choose):

Send File - ASCII...

g. Use dialog box and select applicable S-record object file.

Click on: Send

Motorola S-record file is now transferred to the BCC.

#### NOTE

S-record file will not be displayed during the file transfer to the BCC.

The underline cursor flashes and the beeper sounds when the S-record has finished downloading. Press the carriage return twice to return to the CPU32Bug prompt:

$\langle CR \rangle$

<CR>

CPU32Bug>

Semiconductor, Inc

# Freescale Semiconductor, Inc.

**OPERATING INSTRUCTIONS**

#### 3.6.3 IBM-PC (with KERMIT) to BCC

Before performing any IBM-PC operation, ensure that both IBM-PC and BCC baud rates are 9600, and that the IBM-PC asynchronous port is configured for terminal mode of operation. If the asynchronous port is hard wired for host mode of operation and cannot be re-configured for a terminal mode of operation, the use a null modem (cross-coupled transmit (TxD), and receive (RxD), and associated handshake lines) is required.

#### NOTE

IBM-PC to BCC connection requires one serial communication cable assembly. This cable is connected to the BCC terminal I/O port connector J9 for downloading operations.

To perform IBM-PC to BCC downloading procedure:

**EXAMPLE**

#### **DESCRIPTION**

C>KERMIT<CR>

IBM-PC prompt. Enter Kermit program.

IBM-PC Kermit-MS VX.XX

Type ? for help

Kermit-MS>SET BAUD 9600<CR>

Set IBM-PC baud rate.

Kermit-MS>CONNECT<CR>

Connect IBM-PC to BCC.

[Connecting to host, type Control-] C to return to PC]

<CR>

CPU32Bug>LO<CR> BCC download command (via terminal

port) entered.

(CTRL)]C

Kermit-MS>PUSH<CR>

The IBM Personal Computer DOS

Version X.XX (C)Copyright IBM Corp. 1981, 1982, 1983

C>TYPE (File Name) > COM1<CR> Motorola S-record file name.

C>EXIT<CR> S-record downloading completed.

Kermit-MS>CONNECT<CR> Return to BCC monitor program.

**OPERATING INSTRUCTIONS**

The underline cursor flashes and the beeper sounds when the S-record has finished downloading. Press the carriage return twice to return to the CPU32Bug prompt:

<CR>

<CR>

CPU32Bug>

CPU32Bug>(CTRL) ]C

KERMIT-MS>EXIT<CR>

Exit Kermit program.

# Freescale Semiconductor, Inc.

**OPERATING INSTRUCTIONS**

#### 3.6.4 IBM-PC (with PROCOMM) to BCC

To perform the IBM-PC to BCC downloading procedure with PROCOMM:

- a. Execute the PROCOMM.EXE program.

- b. Setup PROCOMM to match BCC baud rate and protocol (type (Alt)P, then the number 11) as follows:

9600 baud, no parity, 8 bits, 1 stop bit, full duplex

c. Setup ASCII transfer parameters (type (Alt)S, then the number 6) as follows:

Echo Local - No

Expand Blank Lines - Yes

Pace Character - 0

Character pacing - 15 (milliseconds)

Line Pacing - 10

CR Translation - None

LF Translation - None

Save above settings to disk for future use.

- d. Apply power to BCC.

- e. Press IBM-PC keyboard carriage return (<**CR**>) key to display applicable BCC monitor prompt.

- f Enter BCC monitor download command as follows:

CPU32Bug>LO<CR>

g. Instruct PROCOMM to send the S-record file by pressing the Pg Up key on the PC, then follow PROCOMM instructions on the display screen to select the S-record file using an ASCII protocol.

Motorola S-record file is transferred to the BCC when the beeper sounds and the underline cursor flashes. Press the carriage return twice to return to the CPU32Bug prompt:

$\langle CR \rangle$

<**CR**>

CPU32Bug>

# CHAPTER 4 FUNCTIONAL DESCRIPTION

## 4.1 INTRODUCTION

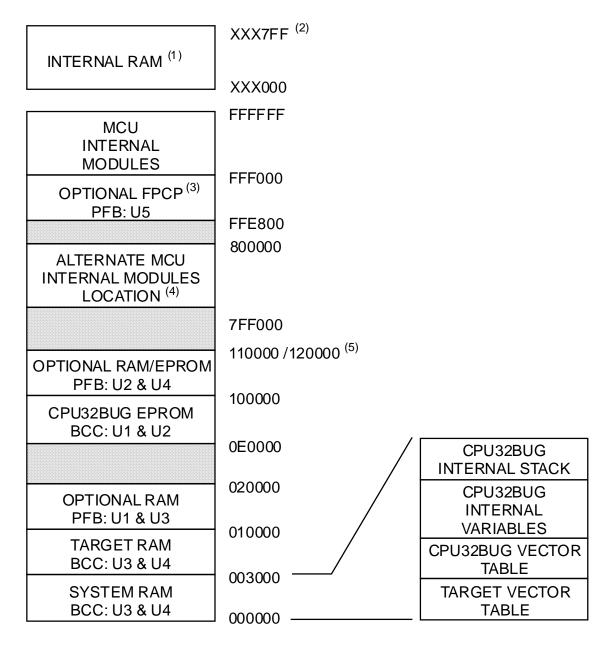

This chapter provides a functional description of the BCC. This description is supported by a block diagram (Figure 4-1) and a memory map diagram (Figure 4-2). Refer to Chapter 5 for the BCC schematic diagram.

#### 4.2 BCC DESCRIPTION

The MC68331 Microcontroller Unit (MCU) resident on the BCC provides resources for designing, debugging, and evaluating MC68331 MCU based target systems and simplifies user evaluation of prototype hardware/software products.

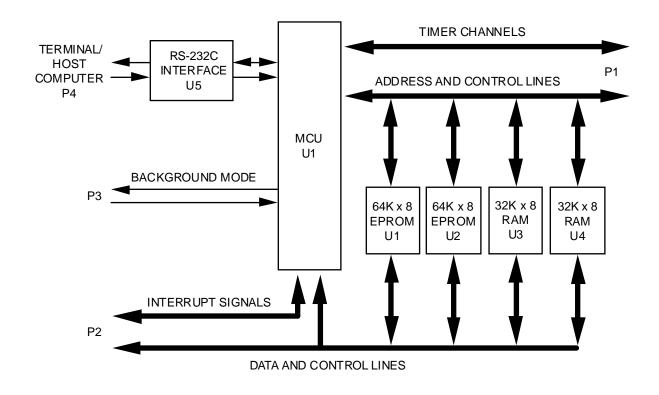

Figure 4-1 is a block diagram of these BCC circuits:

- MCU

- User memory

- Terminal and host computer I/O port

- Background mode interface port

Figure 4-1. BCC Block Diagram

#### 4.2.1 MCU

The resident MC68331 Microcontroller Unit (MCU) of the BCC provides resources for designing, debugging, and evaluating MC68331 MCU based target systems and simplifies user evaluation of prototype hardware/software products.

The MCU device is a 32-bit integrated microcontroller, combining high-performance data manipulation capabilities with powerful peripheral subsystems. The MCU includes:

- 32-bit central processor unit (CPU32)

- General Purpose Timer (GPT)

- Queued serial module (QSM)

- · External bus interface

- · Chip selects

- System clock

- Test module

Semiconductor, Inc

# Freescale Semiconductor, Inc.

**FUNCTIONAL DESCRIPTION**

#### 4.2.1.1 32-Bit Central Processor Unit

The CPU32 is the MC68331 MCU central processor. The CPU32 is source- and object-code compatible with the MC68000 and MC68010. All user-state programs can be executed unchanged. The CPU32 features are:

- 32-bit internal data path and arithmetic hardware 16-bit external data bus

- 32-bit internal address bus 24-bit external address bus

- Powerful instruction set

- Eight 32-bit general purpose data registers

- Seven 32-bit general purpose address registers

- Separate user and supervisor stack pointers and address spaces

- Separate program and data address spaces

- Flexible addressing modes

- Full interrupt processing

#### **4.2.1.2** General-Purpose Timer (GPT)

The GPT is a simple, flexible 11-channel timer for use in systems that require a moderate degree of external visibility and control. The GPT consists of two nearly independent submodules: the compare/capture unit and the pulse-width modulation (PWM) unit. The former features three input capture channels, four output compare channels, and one input capture/output compare channel (function selected via control register). These channels share a 16-bit free-running counter (TCNT) that derives its clock signal from a nine-stage prescaler or from the external clock input pin, PCLK. The timer counter also contains one pulse accumulator channel. The pulse accumulator logic includes its own 8-bit counter and can operate in either event counting mode or gated time accumulation mode.

The PWM submodule is associated with two output pins. The outputs are periodic wave forms whose duty cycles may be independently selected and modified by user software. The PWM unit has its own 16-bit free-running counter that is clocked by an output of the nine-stage prescaler (the same prescaler used by the compare/capture unit) or by the clock input pin, PCLK.

If not needed for timing functions, any of the pins associated with the GPT may be used for general-purpose input/output. The input capture and output compare pins are bi-directional and may be used to form an 8-bit parallel port. The PWM pins are outputs only. PAI and PCLK are inputs only.

**FUNCTIONAL DESCRIPTION**

## 4.2.1.3 Queued Serial Module

The QSM contains two serial ports. The queued serial peripheral interface (QSPI) port provides easy peripheral expansion or inter-processor communications via a full-duplex, synchronous, three-line bus: data-in, data-out, and a serial clock. Four programmable peripheral select pins provide address-ability for as many as 16 peripheral devices. A QSPI enhancement is an added queue in a small RAM. This lets the QSPI handle as many as 16 serial transfers of 8- to 16-bits each, or to transmit a stream of data as long as 256 bits without CPU intervention. A special wrap-around mode lets the user continuously sample a serial peripheral, automatically updating the QSPI RAM for efficient interfacing to serial peripheral devices (such as analog-to-digital converters).