i.MX Machine Learning User's Guide Rev. LF6.6.3\_1.0.0 — 29 March 2024

User guide

#### **Document information**

| Information | Content                                                                                                                                                                                                                                              |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | i.MX, Linux, LF6.6.3_1.0.0                                                                                                                                                                                                                           |

| Abstract    | The NXP eIQ Machine Learning Software Development Environment (hereinafter referred to as "NXP eIQ") provides a set of libraries and development tools for machine learning applications targeting NXP microcontrollers and applications processors. |

# **1** Software Stack Introduction

The NXP eIQ Machine Learning Software Development Environment (hereinafter referred to as "NXP eIQ") provides a set of libraries and development tools for machine learning applications targeting NXP microcontrollers and application processors. The NXP eIQ is contained in the *meta-imx/meta-ml* Yocto layer. See also the *i.MX Yocto Project User's Guide* (IMXLXYOCTOUG) for more information.

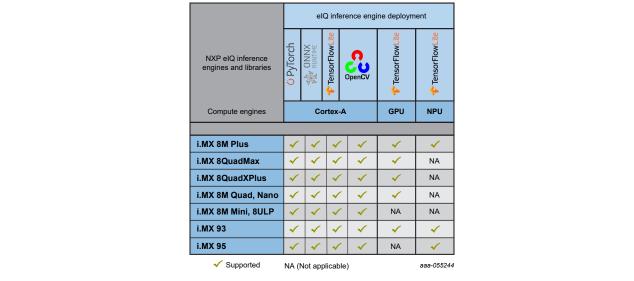

The following four inference engines are currently supported in the NXP eIQ software stack: TensorFlow Lite, ONNX Runtime, PyTorch, and OpenCV. The following figure shows the supported eIQ inference engines across the computing units.

Figure 1. NXP elQ supported compute vs. inference engines

The NXP eIQ inference engines support multi-threaded execution on Cortex-A cores. Additionally, TensorFlow Lite also supports acceleration on the GPU or NPU. Generally, the NXP eIQ is prepared to support the following key application domains:

- Vision

- Multi-camera observation

- Active object recognition

- Gesture control

- Voice

- Voice processing

- Home entertainment

- Sound

- Smart sense and control

- Visual inspection

- Sound monitoring

# 2 TensorFlow Lite

TensorFlow Lite is an open-source software library focused on running machine learning models on mobile and embedded devices (available at <u>http://www.tensorflow.org/lite</u>). It enables on-device machine learning inference with low latency and small binary size. TensorFlow Lite also supports hardware acceleration:

• Using the VX Delegate on i.MX 8 series.

- Using the Ethos-U Delegate on i.MX 93.

- Using the Neutron Delegate on i.MX 95.

The TensorFlow Lite source code for this Yocto Linux release is available at this <u>repository</u>, branch If-6.6.3\_1.0.0. This repository is a fork of the mainline <u>https://github.com/tensorflow/tensorflow</u>, and it is optimized for NXP i.MX 8 and i.MX 9 platforms.

Features:

- TensorFlow Lite v2.14.0

- Multithreaded computation with acceleration using Arm Neon SIMD instructions on Cortex-A cores

- Parallel computation using GPU/NPU hardware acceleration (on shader or convolution units)

- C++ and Python API (supported Python version 3)

- Per-tensor and Per-channel quantized models support

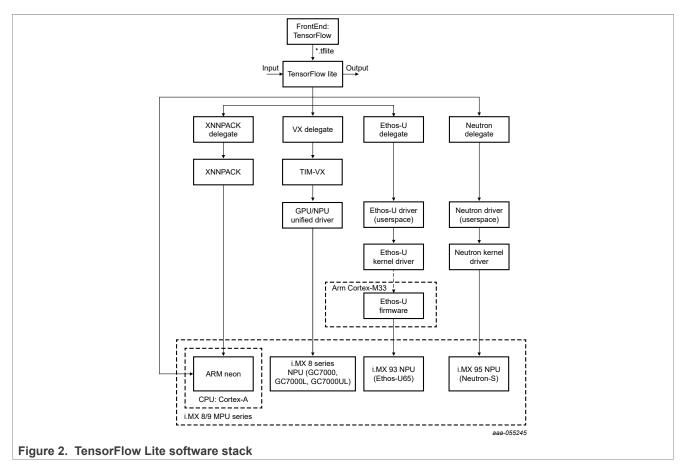

#### 2.1 TensorFlow Lite software stack

The TensorFlow Lite software stack is shown in the following picture. The TensorFlow Lite supports computation on the following hardware units:

- CPU Arm Cortex-A cores

- GPU/NPU hardware accelerator using the VX Delegate on i.MX 8 Series

- NPU hardware acceleration using Ethos-U Delegate on i.MX 93 NPU

- NPU hardware acceleration using Neutron Delegate on i.MX 95 NPU

See <u>Section 1</u> for some details about supporting of computation on GPU/NPU hardware accelerator on different hardware platforms.

IMXMLUG

#### i.MX Machine Learning User's Guide

#### Note:

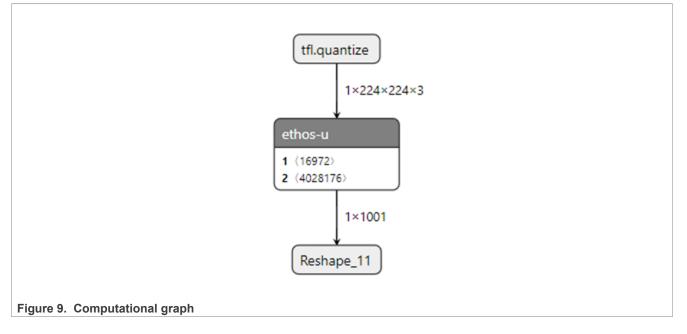

The first execution of the model inference using the delegate takes longer, because of the time required for computational graph compilation and initialization for the hardware accelerator. The following iterations performs much quicker. The computational graph is the representation of the operations and their dependencies to perform computation specified by the model. The computation graph is built during the model parsing phase. See <u>Section 7</u> for details.

The VX Delegate implementations use the OpenVX library for computational graph execution on the GPU/NPU hardware accelerator. Therefore, OpenVX library support must be available for the selected device to be able to use the acceleration. For more details on the OpenVX library availability, see the i.MX Graphics User's Guide (IMXGRAPHICUG).

Refer to i.MX Graphics Users Guide for list GPUs with OpenVX support. Note the GC7000 Lite and GC7000 Ultra Lite GPUs does not support full OpenVX however still capable to run ML workload.

The GPU/NPU hardware accelerator driver supports both per-tensor and per-channel quantized models. The GPU/NPU hardware accelerator on the i.MX 8 family is optimized for per-tensor quantized models. In case of per-channel quantized models, the performance might be lower. The actual impact depends on the model used.

# 2.2 Compute backends and delegates

TensorFlow Lite comes with options to execute compute operations of various compute units. We will refer to them as inference backends.

#### 2.2.1 Built-in kernels

Default inference backend is the CPU with reference kernels from TensorFlow Lite implementation. Built-in kernels provide full support for TensorFlow Lite operator set.

The built-in kernels are built with RUY matrix multiplication library enabled, which increases the performance of the kernels for floating point and quantized operations.

#### 2.2.2 XNNPACK delegate

XNNPACK library is a highly optimized library of floating-point neural network inference operators for ARM, WebAssembly, and x86 platforms. The XNNPACK library is available through XNNPACK delegate in TensorFlow Lite. The XNNPACK delegate computation is performed on the CPU.

It provides optimized implementation for a subset of TensorFlow Lite operator set for floating point operators. In general, it provides better performance than the built-in kernels for floating point operators.

**Note:** Since TensorFlow Lite 2.6.0, the floating point models are executed via the XNNPACK Delegate by default.

#### 2.2.3 VX Delegate

VX Delegate enables accelerating the inference on on-chip hardware accelerator on i.MX 8 series. The VX Delegate directly uses the hardware accelerator driver (OpenVX with extension) to fully utilize the accelerator capabilities.

The VX Delegate is available as *external delegate*<sup>1</sup>. The corresponding library is available in /usr/lib/libvx\_delegate.so.

VX Delegate is supported in both C++ and Python API. For using VX Delegate (or any external delegate), see the <u>external\_delegate\_provider</u> implementation in C++ and/or <u>label\_image.py</u> for Python. List of supported operators are available in <u>op\_status.md</u>.

#### 2.2.4 Ethos-U Delegate

Ethos-U Delegate is an external delegate on i.MX 93 Linux platforms. It enables accelerating the inference on the on-chip hardware accelerator. The Ethos-U Delegate directly uses the hardware accelerator driver (Ethos-U driver stack) to fully utilize the accelerator capabilities.

The Ethos-U Delegate is available as *external delegate*. The corresponding library is available in /usr/lib/ libethosu delegate.so.

Ethos-U Delegate is supported in both C++ and Python API. For using Ethos-U Delegate (or any external delegate), see the <code>external\_delegate\_provider</code> implementation in C++ and/or <code>label\_image.py</code> for Python. List of supported operators are available in <u>SUPPORTED\_OPS.md</u>.

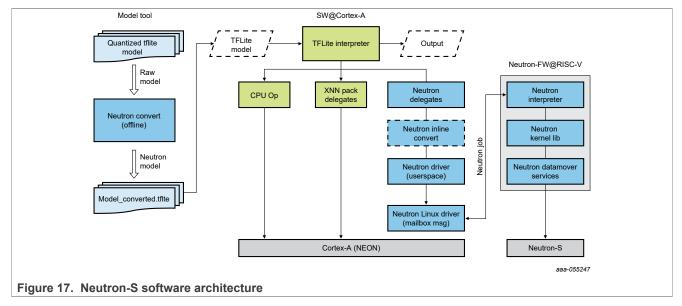

#### 2.2.5 Neutron Delegate

Neutron Delegate is an external delegate on i.MX 9 series Linux platform containing Neutron-S NPU. It captures the operators and aggregates them as a neutron graph node, which can be directly offloaded and accelerated by the Neutron-S NPU.

The delegate library is available in /usr/lib/libneutron\_delegate.so. It can be used in both C+ + and Python API environments. For using Neutron Delegate, see the external\_delegate\_provider implementation in C++ and/or label\_image.py for Python usage.

IMXMLUG

© 2024 NXP B.V. All rights reserved.

<sup>1</sup> An external delegate is a special Tensorflow Lite delegate that is simply initialized from loading a dynamic library which encapsulates an actual <u>TensorFlow Lite delegate implementation</u>

#### Note:

For the offline compilation, the model should be converted through the eIQ toolkit first. In the converted model, the neutronGraph node is already generated. The neutron-delegate only captures the neutronGraph node and offloads the work to Neutron-S. Inline compilation is not supported yet.

### 2.3 Delivery package

The TensorFlow Lite is available using Yocto Project recipes.

The TensorFlow Lite delivery package contains:

- TensorFlow Lite shared libraries

- TensorFlow Lite header files

- Python Module for TensorFlow Lite

- Image classification example application for C++ (label image) and for Python (label image.py)

- TensorFlow Lite benchmark application (benchmark model)

- TensorFlow Lite evaluation tools (coco\_object\_detection\_run\_eval, imagenet\_image\_ classification run eval, inference diff run eval), see <u>TensorFlow Lite Delegates</u> for details.

For application development, the TensorFlow Lite shared libraries and header files are available in the SDK. See <u>Section 2.5</u> for more details.

There are following delegates available in the TensorFlow Lite 2.14.0 delivery package:

- XNNPACK Delegate

- VX Delegate

- Ethos-U Delegate

- Neutron Delegate

# 2.4 Build details

TensorFlow Lite uses CMake build system for compilation. Notable remarks to package build are:

- RUY matrix multiplication library is enabled (TFLITE\_ENABLE\_RUY=On). RUY matrix multiplication library offers better performance compared to kernels build with Eigen and GEMLOWP.

- XNNPACK Delegate support (TFLITE ENABLE XNNPACK=On)

- External Delegate support (TFLITE ENABLE EXTERNAL DELEGATE=On)

- The runtime library is built and provided as a shared library (TFLITE\_BUILD\_SHARED\_LIB=On). If static linking of the TensorFlow Lite library to the application is preferred, keep this switch in off state (default settings). This might be convenient if the application is built with CMake as described in the Section <u>Section 2.5.1</u>.

- The package is compiled with the default -O2 optimization level. Some CPU kernels, such as RESIZE\_BILINEAR, are known to perform better with -O3 optimization level. However, some performs better with -O2, such as ARG\_MAX. We recommend to adjust the optimization level, based on the application needs.

Yocto project builds the TensorFlow Lite with these settings. The build configuration can be changed by either updating the TensorFlow Lite Yocto recipe in the meta-imx layer (located in meta-imx/meta-ml/recipes-libraries/tensorflow-lite/), or building the TensorFlow Lite from source code using the CMake and the Yocto SDK.

# 2.5 Application development

This section describes how to use TensorFlow Lite C++ API in the application development.

IMXMLUG

6 / 107

© 2024 NXP B.V. All rights reserved

To start with TensorFlow Lite C++ application development, a Yocto SDK must be generated firstly. See the *i.MX Yocto Project User's Guide* (IMXLXYOCTOUG) for detailed information how to generate Yocto SDK environment for cross-compiling. To activate this Yocto SDK environment on your host machine, use this command:

\$ source <Yocto SDK install folder>/environment-setup-aarch64-poky-linux

To build an application which uses the TensorFlow Lite, following options are available:

- Create CMake project which uses TensorFlow Lite (CMake superbuild pattern)

- Using Yocto SDK precompiled libraries

The TensorFlow Lite's CMake configuration file is in tensorflow/lite/CMakeLists.txt from the root repository.

#### 2.5.1 Create CMake project which uses TensorFlow Lite

The recommended way is to create a CMake project which uses TensorFlow Lite as described in <u>Build</u> <u>TensorFlow Lite with CMake</u>. CMake takes care of dependencies preparation, including download, configure and build steps.

To demonstrate this build option, there is a minimal example project available in tensorflow/lite/ examples/minimal. To build it:

- 1. Set up the Yocto SDK as described above

- 2. Configure the project using CMake:

```

$ mkdir build-minimal-example; cd build-minimal-example

$ cmake -DCMAKE_TOOLCHAIN_FILE=${OE_CMAKE_TOOLCHAIN_FILE} -

DTFLITE_ENABLE_XNNPACK=on \

-DTFLITE_ENABLE_RUY=on \

../tensorflow/lite/examples/minimal

```

3. Build the project:

```

$ cmake --build . -j4

```

4. The minimal example is available in the build directory:

```

$ file minimal

minimal: ELF 64-bit LSB shared object, ARM aarch64, version 1 (GNU/

Linux), dynamically linked, interpreter /lib/ld-linux-aarch64.so.1,

BuildID[sha1]=4a928894439e0b33217ea28790378690ab4ce7cd, for GNU/Linux

3.14.0, with debug_info, not stripped

```

5. Optionally you can strip the final binary:

```

$ $STRIP --remove-section=.comment --remove-section=.note --strip-unneeded

<file>

```

This build option has several advantages:

- · Automatic dependency resolution based on configure options

- Option to choose between static or dynamic linking (TFLITE BUILD SHARED LIB=on/off)

- Building the whole project (including its dependencies) in the Debug mode (CMAKE\_BUILD\_TYPE=Debug/ Release/...), for enhanced debugging experience

IMXMLUG

#### 2.5.2 Using Yocto SDK precompiled libraries

Another option is to use the precompiled binaries and header files which are directly available in the Yocto SDK. The TensorFlow Lite artifacts are in the Yocto SDK as follows:

- TensorFlow Lite shared library (libtensorflow-lite.so) in /usr/lib

- TensorFlow Lite header files in /usr/include

**Note:** Not all TensorFlow Lite dependencies are installed in the Yocto SDK and it is necessary to download and optionally build them manually. For the required versions see the <code>tensorflow/lite/tools/cmake/modules/folder</code>.

To build the image classification demo (label\_image), located in tensorflow/lite/examples/label\_image/, follow these steps:

1. Create build directory:

```

$ mkdir build-manual

$ cd build-manual

```

2. Download the Abseil library dependency:

```

$ wget https://github.com/abseil/abseil-cpp/

archive/6f9d96a1f41439ac172ee2ef7ccd8edf0e5d068c.tar.gz -0 abseil-cpp.tar.gz

$ tar -xzf abseil-cpp.tar.gz

$ mv abseil-cpp-6f9d96a1f41439ac172ee2ef7ccd8edf0e5d068c abseil-cpp

```

3. Build the label\_image example:

```

$ $CC ../tensorflow/lite/examples/label_image/label_image.cc ../tensorflow/

lite/examples/label_image/bitmap_helpers.cc ../tensorflow/lite/tools/

evaluation/utils.cc ../tensorflow/lite/tools/delegates/delegate_provider.cc -

Iabseil-cpp -02 -ltensorflow-lite -lstdc++ -lpthread -lm -ldl -lrt -I../

```

# 2.6 Enabling TensorFlow Operators in TensorFlow Lite Runtime

The TensorFlow Lite Operator Set counts more than a hundred of frequently used operators and layers, and majority of Machine Learning models can fit into it. Still the TensorFlow Lite Operator Set is only a subset of TensorFlow Operator Set, so not every model is convertible.

To tackle this limitation, TensorFlow offers an option to use TensorFlow Operator inside the TensorFlow Lite runtime. See <u>https://www.tensorflow.org/lite/guide/ops\_select</u>. It shows how this feature can be used with NXP i.MX devices with Yocto Linux platform.

#### 2.6.1 TensorFlow and TensorFlow Lite Operator Set

If the model is not convertible within the standard TensorFlow Lite Operator Set, the TensorFlow Lite converter raises an error, indicating particular operator is not available in TensorFlow Lite, for example:

```

Some ops are not supported by the native TFLite runtime, you can enable TF

kernels fallback using TF Select. See instructions: https://www.tensorflow.org/

lite/guide/ops_select

TF Select ops: Roll

Details: tf.Roll(tensor<?x10xf32>, tensor<i32>, tensor<i32>) -> (tensor<?

x10xf32>) : {device = ""}

```

To Convert such a model, the Select TensorFlow Ops feature needs to be enabled in the Converter, by allowing the TensorFlow Operator Set as follows:

```

converter.target_spec.supported_ops = [

tf.lite.OpsSet.SELECT_TF_OPS # enable TensorFlow ops.

]

```

When the model converted with SELECT\_TF\_OPS is enabled, the corresponding TensorFlow Operators need to be supported in the TensorFlow Lite runtime. This is supported through Flex Delegate. The Flex Delegate is the TensorFlow Lite counterpart for the "Select TensorFlow Operators" and bridges the TensorFlow Lite and TensorFlow Runtimes.

#### 2.6.2 Building the TensorFlow Lite Library with the Flex Delegate for i.MX Linux platforms

The library can be built directly by bazel on any supported host or inside the Docker container, which is available for TensorFlow. It is recommend to use Docker because the environment is ready for TensorFlow compilation. Compilation outside of Docker might fail for multiple reasons. This document focuses on building the TensorFlow Lite Library with Flex Delegate inside the TensorFlow's Docker image.

#### Note:

To build the library outside the Docker image, the <code>bazel</code> build system needs to be installed on the machine. The TensorFlow requires an exact version of <code>bazel</code>, which is specific to particular TensorFlow version. Therefore, use <code>bazelisk</code> to handle the <code>bazel</code> version management. Find the <code>bazelisk</code> tool on its GitHub space <u>https://github.com/bazelbuild/bazelisk</u>, with prebuilt executables for multiple platforms available.

It is recommended to have at least 32 GB RAM to build the Flex Delegate, and ensure that enough inodes are available in build-related directories, such as /tmp.

#### 2.6.2.1 Checking out the TensorFlow repository

To build the TensorFlow Lite library, check out the TensorFlow sources:

Clone the tensorflow-imx repository from <u>https://github.com/nxp-imx/tensorflow-imx</u> and check out the corresponding release branch:

```

$ git clone https://github.com/nxp-imx/tensorflow-imx.git -b lf-6.6.3_1.0.0

$ cd tensorflow-imx

```

#### 2.6.2.2 Setting up Docker VM

For more details about the Docker VM setup for TensorFlow, see https://www.tensorflow.org/install/docker.

#### Note:

Depending on the host, the Docker may require administrative privileges to run (e.g., *sudo* in Linux). Alternatively, the Docker Daemon can run as a non-root user (Rootless mode), as described here <u>https://docs.</u> docker.com/engine/security/rootless/.

1. Download the tensorflow/tensorflow:devel Docker image. The devel image contains the bazel and other required tooling for TensorFlow compilation.

\$ docker pull tensorflow/tensorflow:devel

2. Run the Docker VM. During the build process, Bazel downloads various packages from the Internet. Therefore, Internet access inside the instantiated container is required. In case of conflict, a minimal setup

IMXMLUG

is to initialize  $http\_proxy$  and  $https\_proxy$  environmental variables when launching the Docker image. Particular steps depend on the host configuration.

```

$ docker run -e "http_proxy=<your-http-proxy>" \

-e "https_proxy=<your-https-proxy>" \

-e "no_proxy=localhost,127.0.0.1" \

-it -w /tensorflow -v /<path-to-tensorflow-sources>:/tensorflow

-e HOST_PERMS="\\((id -u):\\)(id -g)" \

tensorflow/tensorflow:devel bash

```

#### 2.6.2.3 Building the TensorFlow Lite with Flex Delegate

NXP i.MX platforms (i.MX 8 family, i.MX 9) use Arm CPU (aarch64) and the build for Linux environment (Yocto Linux). Therefore, use the elinux aarch64 configuration, which is available for TensorFlow.

1. Configure the project using the configure script:

```

$ ./configure

```

The Flex Delegate sources and bazel build recipes are located in /tensorflow/lite/delegates/ flex. There are two libraries defined:

- tensorflowlite\_flex\_[full|reduced] TensorFlow Lite Flex Delegate shared library (libtensorflowlite\_flex.so)

- delegate\_[full|reduced] special target to be used for static linking of the TensorFlow Lite Flex Delegate. Similar to object library concept in CMake.

Additionally Bazel targets for building different variants of the benchmark\_model binary are provided in the /tensorflow/lite/delegates/flex/test/BUILD, for evaluation purposes:

benchmark model plus flex [dynamic] [full|reduced]

2. Build the benchmark model plus flex target with a full TensorFlow Operator Set:

```

$ bazel --output_base=/tensorflow/docker-build/ build --config=monolithic

--config=elinux_aarch64 -c opt --cxxopt='--std=c++17' --

host_crosstool_top=@bazel_tools//tools/cpp:toolchain //tensorflow/lite/

delegates/flex/test:benchmark_model_plus_flex_full

```

**Note:** To preserve the Bazel's cache, use the *--output\_base* switch to override the default output base. For the build outside the Docker, this switch can be omitted. The directory shall be available prior to running Bazel build.

The output is the <code>benchmark\_model\_plus\_flex</code> binary with statically linked Flex Delegate. This can be directly used on NXP MPU platforms.

The -c (or --compilation\_mode) affects code generation option. It can be set to fastbuild, dbg or opt. See <a href="https://bazel.build/docs/user-manual#build-semantics">https://bazel.build/docs/user-manual#build-semantics</a>. To build the Flex Delegate for debugging purposes, use the -c dbg option.

The following table lists the benchmark\_model\_plus\_flex\_\* build configurations.

| Operator set          | Static linkage                        | Dynamic linkage                                       |

|-----------------------|---------------------------------------|-------------------------------------------------------|

| Full Flex Delegate    | benchmark_model_plus_flex_full        | benchmark_model_plus_flex_dynamic_full                |

| Reduced Flex Delegate | benchmark_model_plus_flex_<br>reduced | <pre>benchmark_model_plus_flex_dynamic_ reduced</pre> |

#### Table 1. benchmark\_model build configurations

#### 2.6.3 Reducing the size of the Flex Delegate library

The previous section describes how to build a TensorFlow Lite Library with a complete TensorFlow Operator Set. The approach is useful for quick evaluation, but for practical use, it generates an oversized binary. Moreover, typically only a small subset of TensorFlow operators are required.

To minimize the size, there is a model-dependent build option which extracts the required operators from the models, and selectively includes them in the deployed TensorFlow Lite library. For more details, see <u>https://www.tensorflow.org/lite/guide/reduce\_binary\_size</u>.

For example, there are targets with the \_reduced suffix, which builds the TensorFlow Lite library for the / tensorflow/lite/delegates/flex/test/simple\_flex\_model\_int8.tflite example model. The model contains a single TensorFlow operation: tf.roll().

```

$ bazel --output_base=/tensorflow/docker-build/ build --config=monolithic

--config=elinux_aarch64 -c opt --cxxopt='--std=c++17' --

host_crosstool_top=@bazel_tools//tools/cpp:toolchain

//tensorflow/lite/delegates/flex/test:benchmark_model_plus_flex_reduced

```

To build the TensorFlow Lite library for custom model, use a bazel function tflite\_flex\_cc\_library (for static library) or tflite\_flex\_shared\_library (for shared library), and list the models into the models attribute:

```

tflite_flex_cc_library(

name = "delegate_reduced",

models = [

"simple_flex_model_int8.tflite",

],

visibility = ["//visibility:public"],

)

```

This library can be used inside the bazel to link to a custom TensorFlow Lite binary, like this:

#### 2.6.4 Flex Delegate deployment on NXP i.MX Linux platform

For the statically linked binary (in this usecase, benchmark\_model\_plus\_flex\_[full|reduced]), copy the binary to target the device rootfs.

For the dynamically linked binary (in this usecase, benchmark\_model\_plus\_flex\_dynamic\_[full| reduced]), copy both libtensorflowlite\_flex.so and the binary to target the device rootfs. The libtensorflowlite\_flex.so should be copied to /usr/lib/, or alternatively the LD\_LIBRARY\_PATH should be set, to load the library by the dynamic linker or loader.

1. Copy the simple\_flex\_model\_int8.tflite example model on the i.MX platform, e.g., to /usr/bin/ tensorflow-lite-2.14.0/examples/.

```

$ scp tensorflow/lite/delegates/flex/test/simple_flex_model_int8.tflite

root@<imx-board>:/usr/bin/tensorflow-lite-2.14.0/examples/

```

2. Run the example application benchmark model:

```

$ ./benchmark_model_plus_flex_dynamic_full --graph=/usr/bin/tensorflow-

lite-2.14.0/examples/simple_flex_model_int8.tflite

```

```

With --enable op profiling=true, the FlexDelegate invocation is displayed:

```

| ====================================== |             |          |           |          |      |

|----------------------------------------|-------------|----------|-----------|----------|------|

|                                        |             |          |           |          |      |

| [Node ty                               | pe] [count] | [avg ms] | [avg %]   | [cdf %]  | [mem |

| KB] [times calle                       | ed]         |          |           |          |      |

| TfLiteXNNPackDeleg                     | ate 3       | 2.821    | 81.250%   | 81.250%  |      |

| 0.000 3                                |             |          |           |          |      |

| TfLiteFlexDeleg                        | ato 1       | 0.640    | 18.433%   | 99.683%  |      |

| 0.000 1                                | 1           | 0.010    | 10.1000   | JJ.0038  |      |

|                                        |             | 0 000    | 0 0 0 0 0 | 00 01 40 |      |

| RESH                                   | IAPE I      | 0.008    | 0.230%    | 99.914%  |      |

| 0.000 1                                |             |          |           |          |      |

| SOFT                                   | 'MAX 1      | 0.003    | 0.086%    | 100.000% |      |

| 0.000 1                                |             |          |           |          |      |

#### 2.6.5 Using hardware accelerators

The TensorFlow Operators are not part of the TensorFlow Lite Operators Set, so the hardware accelerator on i.MX platforms does not support these operators, though the acceleration of the TensorFlow Lite operators present in the model is supported.

For the hardware Acceleration on i.MX8 Linux platforms, use the VX Delegate (external delegate). The <code>benchmark\_model\_plus\_flex</code> already includes support for external delegates, so the <code>-external\_delegate\_path</code> CLI option can be used for inference acceleration:

```

$ ./benchmark_model_plus_flex_dynamic_full --graph=/usr/bin/tensorflow-

lite-2.14.0/examples/simple_flex_model_int8.tflite --enable_op_profiling=true --

external_delegate_path=/usr/lib/libvx_delegate.so

```

For the hardware acceleration on the i.MX 9 Linux platform, use the Ethos-U Delegate for i.MX 93 or Neutron Delegate for i.MX 95.

Alternativelly, convert the model with the Arm Vela Compiler as described in <u>Section 7.2.3</u>, and also use the Ethos-U Delegate.

```

$ vela /usr/bin/tensorflow-lite-2.14.0/examples/simple flex model int8.tflite

```

Run benchmark model with the Ethos-u Delegate.

```

$ ./benchmark_model_plus_flex_dynamic_full --graph=/usr/bin/tensorflow-

lite-2.14.0/examples/simple_flex_model_int8.tflite --enable_op_profiling=true --

external_delegate_path=/usr/lib/libethosu_delegate.so

```

#### 2.6.6 Flex Delegate limitations

The Flex Delegate has the following limitations:

#### **CPU support only for TensorFlow Operators**

Flex Delegate operators are not supported on the hardware accelerators of i.MX platforms. The TensorFlow Operators fall back to CPU. The acceleration of supported TensorFlow Lite Ops in the model is not impacted. The model can freely combine TensorFlow Lite and TensorFlow Operators. Supported TensorFlow Lite operators of the model will be accelerated.

#### 2.7 Running image classification example

A Yocto Linux BSP image with machine learning layer included by default contains a simple pre-installed example called 'label\_image' usable with image classification models. The example binary file is located at:

/usr/bin/tensorflow-lite-2.14.0/examples

Figure 3. TensorFlow image classification input Demo instructions:

To run the example with mobilenet model on the CPU, use the following command:

```

$ ./label_image -m mobilenet_v1_1.0_224_quant.tflite -i grace_hopper.bmp -l

labels.txt

```

The output of a successful classification on the i.MX 8MPlus SoC for the 'grace\_hopper.bmp' input image is as follows:

```

Loaded model mobilenet_v1_1.0_224_quant.tflite

resolved reporter

invoked

average time: 39.271 ms

0.780392: 653 military uniform

0.105882: 907 Windsor tie

0.0156863: 458 bow tie

0.0117647: 466 bulletproof vest

0.00784314: 835 suit

```

Note: For floating point layers, the TensorFlow Lite uses XNNPACK delegated by default.

#### 2.7.1 Running the example on the i.MX 8 platform hardware accelerator

To run the example application on the CPU without using the XNNPACK delegate, use the -- use xnnpack=false switch.

To run the example with the same model on the GPU/NPU hardware accelerator, add --external\_delegate\_path=/usr/lib/libvx\_delegate.so (for VX Delegate) command line argument. To differentiate between the 3D GPU and the NPU, use the USE\_GPU\_INFERENCE environmental variable. For example, to run the model accelerated on the NPU hardware using VX Delegate, use this command:

```

$ USE_GPU_INFERENCE=0 ./label_image -m mobilenet_v1_1.0_224_quant.tflite

-i grace_hopper.bmp -l labels.txt --external_delegate_path=/usr/lib/

libvx_delegate.so

```

The output of the NPU acceleration on the i.MX 8MPlus processor is as follows:

```

INFO: Loaded model ./mobilenet_v1_1.0_224_quant.tflite

INFO: resolved reporter

Vx delegate: allowed_builtin_code set to 0.

Vx delegate: error_during_init set to 0.

Vx delegate: error_during_prepare set to 0.

Vx delegate: error_during_invoke set to 0.

EXTERNAL delegate created.

INFO: Applied EXTERNAL delegate.

W [HandleLayoutInfer:257]Op 18: default layout inference pass.

INFO: invoked

INFO: average time: 2.567 ms

INFO: 0.768627: 653 military uniform

INFO: 0.105882: 907 Windsor tie

INFO: 0.0196078: 458 bow tie

INFO: 0.0117647: 466 bulletproof vest

INFO: 0.00784314: 835 suit

```

#### 2.7.2 Running the example on the i.MX 93 platform hardware accelerator

To use the hardware acceleration on i.MX 93, use the Ethos-U delegate. Alternatively, convert the model using the Vela compiler first, and run the model with Ethos-U delegate. For details, see <u>Section 7.2.3</u>.

To run the example with the model on the NPU hardware accelerator, add the --external\_delegate\_ path=/usr/lib/libethosu\_delegate.so (for Ethos-U Delegate) command line argument. For example, to run the model accelerated on the NPU hardware using Ethos-U Delegate, use this command:

```

$ ./label_image -m mobilenet_v1_1.0_224_quant.tflite

-i grace_hopper.bmp -l labels.txt --external_delegate_path=/usr/lib/

libethosu_delegate.so

```

#### 2.7.3 Running the example on the i.MX 9 platform with Neutron-S

To use the hardware Acceleration on i.MX 9 with Neutron-S NPU, convert the model using the neutronconverter using the eIQ Toolkit. For details, see the <u>eIQ Toolkit documentation</u>.

```

Run the benchmark example with option:

```

```

--external_delegate_path=/usr/lib/libneutron_delegate.so

```

IMXMLUG

© 2024 NXP B.V. All rights reserved.

```

• Run the Python example with option:

```

```

-e /usr/lib/libneutron_delegate.so

```

#### 2.7.4 Running the Python example

Alternatively, the example using the TensorFlow Lite interpreter-only Python API can be run. The example file is located at:

/usr/bin/tensorflow-lite-2.14.0/examples

To run the example using the predefined command line arguments, use the following command:

```

$ python3 label_image.py

```

The output should be as follows:

```

Warm-up time: 159.1 ms

Inference time: 156.5 ms

0.878431: military uniform

0.027451: Windsor tie

0.011765: mortarboard

0.011765: bulletproof vest

0.007843: sax

```

The Python example supports external delegates also. The switch --ext\_delegate <PATH> and -- ext\_delegate\_options <EXT\_DELEGATE\_OPTIONS>, can be used to specify the external delegate library and optionally its arguments.

# 2.8 Running benchmark applications

A Yocto Linux BSP image with machine learning layer included by default contains a pre-installed benchmarking application. It performs a simple TensorFlow Lite model inference and prints benchmarking information. The application binary file is located at:

/usr/bin/tensorflow-lite-2.14.0/examples

Benchmarking instructions are as follows:

To run the benchmark with computation on CPU, use the following command:

\$ ./benchmark model --graph=mobilenet v1 1.0 224 quant.tflite

You can optionally specify the number of threads with the --num\_threads=X parameter to run the inference on multiple cores. For highest performance, set X to the number of cores available.

The output of the benchmarking application should be similar to:

```

STARTING!

Log parameter values verbosely: [0]

Graph: [mobilenet_v1_1.0_224_quant.tflite]

Loaded model mobilenet_v1_1.0_224_quant.tflite

Going to apply 0 delegates one after another.

The input model file size (MB): 4.27635

Initialized session in 3.051ms.

```

#### i.MX Machine Learning User's Guide

Running benchmark for at least 1 iterations and at least 0.5 seconds but terminate if exceeding 150 seconds. count=4 first=160408 curr=155384 min=155384 max=160408 avg=156869 std=2076 Running benchmark for at least 50 iterations and at least 1 seconds but terminate if exceeding 150 seconds. count=50 first=155586 curr=155424 min=155274 max=155622 avg=155443 std=81 Inference timings in us: Init: 3051, First inference: 160408, Warmup (avg): 156869, Inference (avg): 155443 Note: as the benchmark tool itself affects memory footprint, the following is only APPROXIMATE to the actual memory footprint of the model at runtime. Take the information at your discretion. Peak memory footprint (MB): init=4.49219 overall=10.6133

To run the inference without the XNNPACK delegate, add the --use xnnpack=false switch.

To run the inference using the GPU/NPU hardware accelerator, use the --external delegate path switch:

- For VX Delegate on i.MX 8: --external delegate path=/usr/lib/libvx delegate.so

- For Ethos-U Delegate on i.MX 93: --external delegate path=/usr/lib/libethosu delegate.so

- For Neutron Delegate on i.MX 95: --external\_delegate\_path=/usr/lib/libneutron\_delegate. so

The output with GPU/NPU module acceleration enabled (for VX Delegate) should be similar to:

```

STARTING!

Log parameter values verbosely: [0]

Graph: [mobilenet v1 1.0 224 quant.tflite]

External delegate path: [/usr/lib/libvx delegate.so]

Loaded model mobilenet v1 1.0 224 quant.tflite

Vx delegate: allowed builtin code set to 0.

Vx delegate: error during init set to 0.

Vx delegate: error_during_prepare set to 0.

Vx delegate: error_during_invoke set to 0.

EXTERNAL delegate created.

Going to apply 1 delegates one after another.

Explicitly applied EXTERNAL delegate, and the model graph will be completely

executed by the delegate.

The input model file size (MB): 4.27635

Initialized session in 13.437ms.

Running benchmark for at least 1 iterations and at least 0.5 seconds but

terminate if exceeding 150 seconds.

W [HandleLayoutInfer:257]Op 18: default layout inference pass.

count=1 curr=4586473

Running benchmark for at least 50 iterations and at least 1 seconds but

terminate if exceeding 150 seconds.

count=398 first=2541 curr=2419 min=2419 max=2549 avg=2467.87 std=13

Inference timings in us: Init: 13437, First inference: 4586473, Warmup (avg):

4.58647e+06, Inference (avg): 2467.87

Note: as the benchmark tool itself affects memory footprint, the following is

only APPROXIMATE to the actual memory footprint of the model at runtime. Take

the information at your discretion.

Peak memory footprint (MB): init=7.24609 overall=34.0117

```

The delegates are not required to support the full set of operators defined by the TensorFlow Lite runtime. If the model contains such an operation, which is not supported by the particular delegate, this operation execution falls back to CPU using the TensorFlow Lite reference kernels. This way the computational graph represented by the model gets divided into segments and each segment is executed. The graph segmentation or also called graph partitioning is the process, where the computational graph defined by the model is divided into smaller

segments (or partitions) and each of them is executed via the delegate or on the CPU using reference kernels (CPU fallback), based on operation supported by the delegate.

The benchmark application is also useful to check the optional segmentation of the models if accelerated on GPU/NPU hardware accelerator. For this purpose, the combination of the --enable\_op\_profiling=true and --max\_delegated partitions=<br/>tig number> (e.g., 1000) options can be used.

Which generates detailed profiling information, such as:

| Profiling Info for Bench                                                                                                                                       | nmark Initia                                             | alization:<br>Bun Order ==                                           |                                                         |                                 |                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------|---------------------------------|-------------------------------|

| [node type]                                                                                                                                                    | [start]                                                  | [ [first]                                                            | [avg ms]                                                | [%]                             | [cdf%]                        |

| ModifyGraphWithDelegate                                                                                                                                        | 0.000                                                    | 0 4.597                                                              | 4.597                                                   | 95.791%                         | 95.791%                       |

| AllocateTensors                                                                                                                                                | 4.528                                                    | 8 0.198                                                              | 0.101                                                   | 4.209%                          | 100.000%                      |

| <pre>[node type]<br/>ModifyGraphWithDelegate<br/>AllocateTensors<br/>Number of nodes executed</pre>                                                            | [start]<br>0.000<br>4.528<br>1: 2                        | [ [first]<br>0 4.597<br>3 0.198                                      | [avg ms]<br>4.597<br>0.101                              | [%]<br>95.791%<br>4.209%        | [cdf%]<br>95.791%<br>100.000% |

| [Node type]<br>ModifyGraphWithDelegate<br>AllocateTensors<br>Timings (microseconds):<br>Memory (bytes): count=0<br>2 nodes observed<br>Operator-wise Profiling | [count] [avo<br>1 4<br>1 (<br>count=1 cur<br>Info for Re | g ms] [avg<br>4.597 95.793<br>0.202 4.209<br>cr=4799<br>egular Bench | <pre>k] [cdf %] [n<br/>1% 95.791%<br/>9% 100.000%</pre> | mem KB] [ti<br>684.000<br>0.000 | mes called]<br>1<br>2         |

| [node type] [                                                                                                                                                  | [start]                                                  | [first]                                                              | [avg ms]                                                | [%]                             | [cdf%]                        |

| Vx Delegate 0.000                                                                                                                                              | 14.890                                                   | 14.894                                                               | 11.349%                                                 | 11.3                            | 49%                           |

| RESIZE_BILINEAR                                                                                                                                                | 14.896                                                   | 1.331                                                                | 1.331                                                   | 1.014%                          | 12.363%                       |

| Vx Delegate 16.227                                                                                                                                             | 2.944                                                    | 2.909                                                                | 2.216%                                                  | 14.5                            | 79%                           |

| RESIZE_BILINEAR                                                                                                                                                | 19.137                                                   | 0.279                                                                | 0.277                                                   | 0.211%                          | 14.790%                       |

| RESIZE_BILINEAR                                                                                                                                                | 19.415                                                   | 44.316                                                               | 44.496                                                  | 33.905%                         | 48.695%                       |

| ARG_MAX                                                                                                                                                        | 63.912                                                   | 67.438                                                               | 67.332                                                  | 51.305%                         | 100.000%                      |

| [node type]                                                                                                                                                    | [start]                                                  | [first] [a                                                           | avg ms]                                                 | [%]                             | [cdf%]                        |

| ARG_MAX                                                                                                                                                        | 63.912                                                   | 67.438                                                               | 67.332                                                  | 51.305%                         | 51.305%                       |

| RESIZE_BILINEAR                                                                                                                                                | 19.415                                                   | 44.316                                                               | 44.496                                                  | 33.905%                         | 85.210%                       |

| Vx Delegate 0.000                                                                                                                                              | 14.890                                                   | 14.894                                                               | 11.349%                                                 | 96.5                            | 59%                           |

| Vx Delegate 16.227<br>RESIZE_BILINEAR<br>RESIZE_BILINEAR<br>Number of nodes executed                                                                           | 19.137<br>1: 6                                           | 0.279                                                                | 0.277                                                   | 0.211%                          | 100.000%                      |

| [Node type] [cou<br>ARG_MAX<br>RESIZE_BILINEAR<br>Vx Delegate 2 17<br>Timings (microseconds):<br>std=616<br>Memory (bytes): count=0<br>6 nodes observed        | ant] [avg ms<br>1 67.33<br>3 46.10<br>7.802 13.50        | s] [avg %]<br>32 51.306%<br>02 35.129%<br>55% 100.000                | [cdf %] [1<br>51.306%<br>86.435%<br>0% 0.000            | mem KB] [ti<br>0.000<br>0.000   | mes called]<br>1<br>3<br>2    |

Based on section "Number of nodes executed" in the output, it can be determined which part of the computation graph was executed on GPU/NPU hardware accelerator. Every node except Vx Delegate falls back to CPU. In the example above, the ARG\_MAX and RESIZE\_BILINEAR nodes fall back to CPU.

#### 2.9 Post training quantization using TensorFlow Lite converter

TensorFlow offers several methods for model quantization:

· Post training quantization with TensorFlow Lite Converter

#### i.MX Machine Learning User's Guide

- Quantization aware training using Model Optimization Toolkits and TensorFlow Lite Converter

- Various other methods available in previous TensorFlow releases

#### Note:

The model quantization is also supported by the "eIQ Toolkit". See also eIQ Toolkit User's Guide (EIQTUG).

Covering all of them is beyond the scope of this documentation. This section describes the approach for the post training quantization using the TensorFlow Lite Converter.

The Converter is available as a part of standard TensorFlow desktop installation. It is used to convert and optionally quantize TensorFlow models into TensorFlow Lite model format (\*.tflite). There are two options how to use the tool:

- The Python API (recommended)

- · Command line script

The post training quantization using the Python API is described in this chapter. The documentation useful for model conversion and quantization is available here:

- Python API documentation: <u>https://www.tensorflow.org/versions/r2.14/api\_docs/python/tf/lite/TFLiteConverter</u>

- Guide for model conversion: www.tensorflow.org/lite/convert

- Guide for model quantization: https://www.tensorflow.org/lite/performance/post\_training\_quantization

- Guide for model optimization: <u>https://www.tensorflow.org/model\_optimization</u>

#### Note:

The guides on TensorFlow page usually covers the most up to date version of TensorFlow, which might be different from the version available in the NXP eIQ. To see what features are available, check the corresponding API for the specific version of the TensorFlow or TensorFlow Lite.

The current version of the TensorFlow Lite available in the NXP eIQ is 2.14.0. It is recommended to use the TensorFlow Lite converter from corresponding TensorFlow version. The TensorFlow Lite runtime should be compatible with models generated by previous version of TensorFlow Lite Converter, however this backward compatibility is not guaranteed. Usage of successive version of TensorFlow Lite converter shall be avoided.

The 2.14.0 version of the converter has the following properties:

- In the post training quantization regime, the per-channel quantization is the only option. The per-tensor quantization is available only in connection with quantization aware training.

- Input and output tensors quantization is supported by setting the required data type in inference\_input\_type and inference\_output\_type.

- TOCO or MLIR based conversions are available. This is controlled by the <code>experimental\_new\_converter</code> attribute. As TOCO is becoming obsolete, MLIR-based conversion is already set by default in the 2.14.0 version of the converter.

MLIR converter uses dynamic tensor shapes, what means the batch size of the input tensor is unspecified. Dynamic tensor shapes are not supported by the GPU and NPU hardware accelerators and this shall be turned off. Standard installation of TensorFlow does not provide API to control the dynamic tensor shape feature, but can be deactivated in the tensorflow installation, as follows. Locate the cpython-installdir>/site-packages/tensorflow/lite/python/lite.py file and change the private method

TFLiteConverterBase. is unknown shapes allowed (self) to return False value, as follows:

```

def _is_unknown_shapes_allowed(self):

# Unknown dimensions are only allowed with the new converter.

# Return self.experimental_new_converter

# Disable unknown dimensions support.

return False

```

#### Note:

IMXMLUG

MLIR is a new NN compiler used by TensorFlow, which supports quantization. Before MLIR, quantization was performed by TOCO (or TOCO Converter), which is now obsolete. See <u>https://www.tensorflow.org/api\_docs/</u>python/tf/compat/v1/lite/TocoConverter. For details about MLIR, see <u>https://www.tensorflow.org/mlir</u>.

#### Note:

Do not use the dynamic range method for models being run on NN accelerators (GPU or NPU). It converts only the weights to 8-bit integers, but retains the activations in fp32, which results in the inference running in fp32 with an additional overhead for data conversion. In fact, the inference is even slower compared to a fp32 model, because the conversion is done on the fly.

For the full-integer post training quantization, a representative dataset is needed. The proper choice of samples in representative dataset highly influences the accuracy of the final quantized model. The best practices for creating the representative dataset are:

- Use train samples for which the original floating points model has very good accuracy, based on metrics the model used (e.g., SoftMax score for classification models, IOU for object detection models, etc.).

- There shall be enough samples in representative dataset.

- The size of representative dataset and the specific samples available in it are considered as hyperparameters to tune, with respect of the required model accuracy.

# 2.10 TensorFlow Lite for Microcontrollers on Xtensa HiFi4 core

TensorFlow Lite for Microcontrollers (TFLM) is a lightweight re-implementation of the TensorFlow Lite library for microcontroller CPU cores and NN accelerators (like the Xtensa HiFi4 core on i.MX 8ULP or Arm Ethos-U on i.MX 93). Compared to TensorFlow Lite, it uses less memory, has no C/C++ library dependencies and uses only static memory allocation. On the other hand, the list of supported operators is more limited and optimized kernels are available only for Cortex-M and Xtensa cores or the ARM Ethos-U accelerator. The main purpose of TFLM on the i.MX platform is low-power applications.

To use TFLM on the Xtensa HiFi4 core, the DSP firmware has to be rebuilt with the TFLM library and a TensorFlow Lite model included. As the Xtensa HiFi4 core is also used for audio encoding/decoding, the TFLM library has to be wrapped into an Xtensa Audio Framework (XAF) component to allow simultaneous audio and model inference execution. Moreover, the XAF client/server protocol implements input and output buffer passing to and from the CPU core via the Linux XAF API. The DSP firmware and usage example source codes are available at <a href="https://github.com/NXP/imx-audio-framework">https://github.com/NXP/imx-audio-framework</a>. See the DSP User's Guide in the docs subfolder for information on toolchain setup and build instructions.

To build the DSP firmware with the TFLM library (after the toolchain is installed), use the following Makefile options:

make PLATF=imx8ulp TFLM=1 DSP FIRMWARE

The command produces a hifi4\_tflm\_imx8ulp.bin file which has to be copied to the /lib/firmware/imx/dsp folder of the Yocto Linux BSP image.

To build the TFLM usage example for Linux, use the following Makefile options:

make PLATF=imx8ulp TFLM=1 UNIT TEST

The command compiles the unit\_test/src/dsp\_tflm\_test.c source file and produces a dsp\_tflm\_test.out binary executable file which demonstrates a simple keyword detection application processing a built-in static audio buffer with "yes" and "no" speech command data samples.

By default, TFLM included in the DSP firmware is compiled with reference kernel implementations due to licensing. To improve the library performance on Xtensa HiFi4 cores, the library has to be built with proprietary licensed optimized kernel implementations provided by Cadence at <a href="https://github.com/foss-xtensa/nnlib-hifi4">https://github.com/foss-xtensa/nnlib-hifi4</a>

(see the license file in the GitHub repository). Add the <code>OPTIMIZED\_KERNEL\_DIR=xtensa</code> option into the <code>dsp\_framework/tensorflow\_lite\_micro.inc</code> file to automatically download the Cadence library and build TFLM with the optimized kernels:

```

cd $(SRC_DIR)/tflite-micro && make -f tensorflow/lite/micro/tools/make/

Makefile TARGET=xtensa TARGET_ARCH=hifi4 OPTIMIZED_KERNEL_DIR=xtensa

XTENSA_USE_LIBC=true microlite

```

A DSP firmware file with the same name as previously is produced, which has to be copied to the /lib/ firmware/imx/dsp folder of the Yocto Linux BSP image.

# 3 Arm Compute Library

Arm Compute Library (ACL) is a collection of low-level functions optimized for Arm CPU and GPU architectures targeted at image processing, computer vision, and machine learning.

Source codes are available at https://github.com/nxp-imx/arm-computelibrary-imx.

Features:

- Arm Compute Library 23.11

- · Multithreaded computation with acceleration using Arm Neon SIMD instructions on Cortex-A CPU cores

- C++ API only

- Low-level control over computation

#### Note:

The GPU OpenCL backend is not supported on i.MX 8 devices.

#### 3.1 Running a DNN with random weights and inputs

Arm Compute Library comes with examples for most common DNN architectures like: AlexNet, MobileNet, ResNet, Inception v3, Inception v4, SqueezeNet, etc.

All available examples can be found in this example build location:

/usr/bin/arm-compute-library-23.11/examples

Each model architecture can be tested using graph\_[dnn\_model] application.

For example, to run the MobileNet v2 DNN model, use the following command:

\$ ./graph\_mobilenet\_v2 --data=<path\_cnn\_data> --image=<input\_image> -labels=<labels> --target=neon --type=<data\_type> --threads=<num\_of\_threads>

The parameters are not mandatory. When not provided, the application runs the model with random weights and inputs. If inference finishes successfully, the "Test passed" message is printed.

#### 3.1.1 Running AlexNet using graph API

In 2012, AlexNet shot to fame when it won the ImageNet Large Scale Visual Recognition Challenge (ILSVRC), an annual challenge that aims to evaluate algorithms for object detection and image classification. AlexNet is made up of eight trainable layers: five convolution layers and three fully connected layers. All the trainable layers are followed by a ReLu activation function, except for the last fully connected layer, where the Softmax function is used.

Location of the C++ AlexNet example implementation using the graph API is in this folder:

```

/usr/bin/arm-compute-library-23.11/examples

```

Demo instructions:

- Download the archive file (compute\_library\_alexnet.zip) to the example location folder.

- · Create a new sub-folder and unzip the file:

```

$ mkdir assets_alexnet

$ unzip compute library alexnet.zip -d assets alexnet

```

• Set environment variables for execution:

```

$ export PATH ASSETS=/usr/bin/arm-compute-library-23.11/examples/assets alexnet/

```

• Run the example with following command line arguments:

```

$ ./graph_alexnet --data=$PATH_ASSETS --image=$PATH_ASSETS/go_kart.ppm --labels=

$PATH_ASSETS/labels.txt --target=neon --type=f32 --threads=4

```

The output of a successful classification should be similar as the one below:

```

----- Top 5 predictions -----

0.9736 - [id = 573], n03444034 go-kart

0.0108 - [id = 751], n04037443 racer, race car, racing car

0.0118 - [id = 518], n03127747 crash helmet

0.0022 - [id = 817], n04285008 sports car, sport car

0.0006 - [id = 670], n03791053 motor scooter, scooter

Test passed

```

# 4 ONNX Runtime

ONNX Runtime is an open-source inference engine to run ONNX models, which enables the acceleration of machine learning models across all of your deployment targets using a single set of API. Source codes are available at <a href="https://github.com/nxp-imx/onnxruntime-imx">https://github.com/nxp-imx/onnxruntime-imx</a>.

#### Note:

For the full list of the CPU supported operators, see the 'operator kernels' documentation section: <u>OperatorKernels</u>.

Features:

- ONNX Runtime 1.16.1

- Multithreaded computation with acceleration using Arm Neon SIMD instructions on Cortex-A cores provided by the CPU execution provider

- C++ and Python API (supported Python version 3)

- ONNX Runtime 1.16.1 supports ONNX 1.14 and Opset version 19.

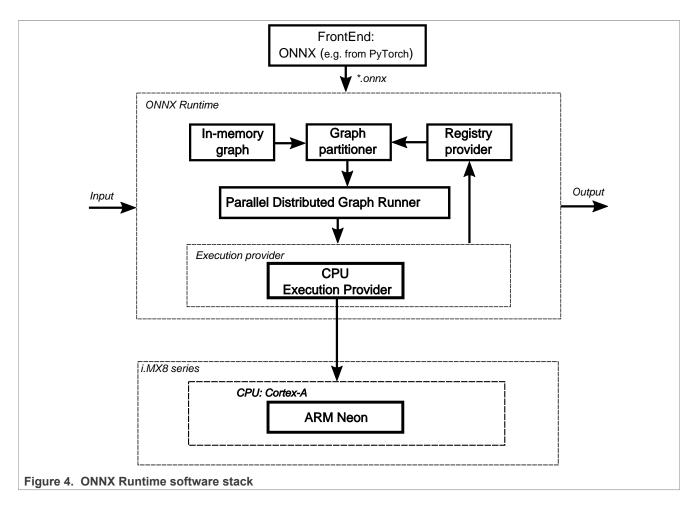

### 4.1 ONNX Runtime software stack

The ONNX Runtime software stack is shown in the following figure. The ONNX Runtime supports computation on the following HW units:

· CPU Arm Cortex-A cores using CPU execution provider

#### i.MX Machine Learning User's Guide

# 4.2 ONNX model test

ONNX Runtime provides a tool that can run the collection of standard tests provided in the ONNX Model Zoo. The tool named onnx\_test\_runner is installed in /usr/bin/onnxruntime-1.16.1.

ONNX models are available at <u>https://github.com/onnx/models</u> and consist of models and sample test data. Because some models require a lot of disk space, it is advised to store the ONNX test files on a larger partition, as described in the SD card image flashing section.

Here is an example with the steps required to run the mobilenet version 2 test:

• Download and unpack the mobilenet version 2 test archive to some folder, for example to/home/root:

```

$ cd /home/root

$ wget https://github.com/onnx/models/raw/main/vision/classification/mobilenet/

model/mobilenetv2-7.tar.gz

$ tar -xzvf mobilenetv2-7.tar.gz

$ ls ./mobilenetv2-7

mobilenetv2-7.onnx test_data_set_0

```

• Run the onnx\_test\_runner tool providing mobilenetv2-7 folder path and setting the execution provider:

```

$ /usr/bin/onnxruntime-1.16.1/onnx_test_runner -j 1 -c 1 -r 1 -e cpu ./

mobilenetv2-7/

result:

Models: 1

```

© 2024 NXP B.V. All rights reserved.

```

Total test cases: 3

Succeeded: 3

Not implemented: 0

Failed: 0

Stats by Operator type:

Not implemented(0):

Failed:

Failed Test Cases:

S

```

#### Note:

Use onnx\_test\_runner -h for the full list of supported options.

# 4.3 C API

ONNX Runtime also provides a C API sample code described here: <u>https://github.com/microsoft/onnxruntime/</u> <u>blob/v1.16.1/docs/C\_API\_Guidelines.md</u>

To build the sample from the <u>repository</u>, run the following build command under the generated Yocto SDK environment (make sure that the onnxruntime-dev Yocto package is installed in the SDK, it should be installed by default):

```

$CXX -std=c++0x -I$SDKTARGETSYSROOT/usr/include/onnxruntime/core/session -

lonnxruntime C Api Sample.cpp -o onnxruntime sample

```

#### Note:

SqueezeNet model included in the BSP can be used with the executables.

#### 4.3.1 Enabling execution provider

To enable a specific execution provider, you need to do the following in your code:

- Set the execution provider in code (see the previous C API sample how that is done for the CUDA EP). If not set, the default CPU EP would be used: OrtSessionOptionsAppendExecutionProvider\_ <execution\_provider>(<parameters>);

- Include headers based on the EP used in the code: #include "<execution\_provider>\_provider\_ factory.h".

- Add includes to the build command: -I/usr/include/onnxruntime/core/providers/<execution\_ provider>/

# 4.4 ONNX performance test

To run model benchmarks, ONNX Runtime provides a tool that measures performance. The tool named onnxruntime\_perf\_test is installed in /usr/bin/onnxruntime-1.16.1. In order to run it, the user must provide an *.onnx* model file together with test data. To benchmark the SqueezeNet model running a single iteration using the CPU execution provider, run to the following command:

```

/usr/bin/onnxruntime-1.16.1/onnxruntime_perf_test /usr/bin/onnxruntime-1.13.1/

squeezenet/model.onnx -r 1 -e cpu

```

#### Note:

```

Use onnxruntime_perf_test -h for the full list of supported options.

```

# 5 PyTorch

PyTorch is a scientific computing package based on Python that facilitates building deep learning projects using power of Graphics Processing Units (GPUs).

Features:

- PyTorch 2.0.0

- Python version 3 supported

- Deep neural networks built on a tape-based autograd system

#### Note:

Only the CPU is supported. By default, the PyTorch runtime is running with floating point model. To enable quantized model, the quantized engine should be specified explicitly as follows:

torch.backends.quantized.engine = 'qnnpack'

# 5.1 Running image classification example

There is an example located in the examples folder, which requires urllib, PIL, and maybe some other Python3 modules depending on your image. You may install the missing modules using pip3.

\$ cd /usr/bin/pytorch/examples

To run the example with inference computation on the CPU, use the following command. There are no arguments and the resources will be downloaded automatically by the script:

```

$ python3 pytorch_mobilenetv2.py

```

The output should be similar as follows:

```

File does not exist, download it from

https://download.pytorch.org/models/mobilenet_v2-b0353104.pth

... 100.00%, downloaded size: 13.55 MB

File does not exist, download it from

https://raw.githubusercontent.com/Lasagne/Recipes/master/examples/resnet50/

imagenet_classes.txt

... 100.00%, downloaded size: 0.02 MB

File does not exist, download it from

https://s3.amazonaws.com/model-server/inputs/kitten.jpg

... 100.00%, downloaded size: 0.11 MB

('tabby, tabby cat', 46.34805679321289)

('Egyptian cat', 15.802854537963867)

('lynx, catamount', 1.1611212491989136)

('lynx, catamount', 1.1611212491989136)

('tiger, Panthera tigris', 0.20774540305137634)

```

# 5.2 Building and installing wheel packages

This release includes building script for PyTorch and TorchVision on aarch64 platform. Currently, it supports the native building on the NXP aarch64 platform with BSP SDK.

**Note:** Generally, in the yocto rootfs of the BSP SDK, the PyTorch and TorchVision wheel packages are already integrated. There is no need to build and install from scratch. If you would like to build them by your own, perform the steps below.

#### 5.2.1 How to build

Perform the following steps:

- 1. Get the latest i.MX BSP from <a href="https://github.com/nxp-imx/imx-manifest">https://github.com/nxp-imx/imx-manifest</a>.

- 2. Set up the build environment for one of the NXP aarch64 platforms and edit the *local.conf* to add the following dependency for PyTorch native build:

```

IMAGE_INSTALL_append = " python3-dev python3-pip python3-wheel python3-pillow

python3-setuptools python3-numpy python3-pyyaml

python3-cffi python3-future cmake ninja packagegroup-core-buildessential git

git-perltools libxcrypt libxcrypt-dev

```

3. Build the BSP images using the following command:

```

$ bitbake imx-image-full

```

4. Get into the pytorch folder and execute the build script on NXP aarch64 platform to generate wheel packages. You can get the source from <a href="https://github.com/NXPmicro/pytorch-release">https://github.com/NXPmicro/pytorch-release</a> as well:

```

$ cd /path/to/pytorch/src

$ ./build.sh

```

#### 5.2.2 How to install

If the building is successful, the wheel packages should be found under /path/to/pytorch/src/dist:

```

$ pip3 install /path/to/torch-1.9.1.post2-cp310-cp310-linux_aarch64.whl

$ pip3 install /path/to/torchvision-0.10.0-cp310-linux_aarch64.whl

```

# 6 TVM

Apache TVM is an open source machine learning compiler framework for CPUs, GPUs, and NPUs. It aims to enable machine learning engineers to optimize and run computations efficiently on any hardware backend.

Features:

- TVM 0.7.0

- · Compilation of deep learning models into minimum deployable modules

- · Infrastructure to automatic generate and optimize models on more backend with better performance

- Support for i.MX 8M Plus platforms with OpenVX library

- TVM builder supported for Ubuntu 18.04, x86 64 platform

#### Note:

For more detailed information, see TVM Documentation.

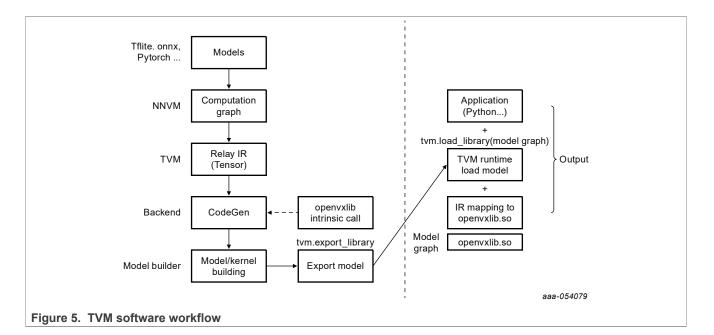

#### 6.1 TVM software workflow

The pre-trained model will be transformed into the Relay IR and passed through to the TVM model optimizations like constant-folding, memory planning, and finally passed to a codegen phase. In this phase, the operators supported by the target device are transformed as intrinsic calls into the offloading library which connects the model accelerator devices such as GPU/NPU.

© 2024 NXP B.V. All rights reserved.

# **NXP Semiconductors**

# **IMXMLUG**

#### i.MX Machine Learning User's Guide

# 6.2 Getting started

#### 6.2.1 Running example with RPC verification

TVM provides the Remote Procedure Call (RPC) capability to run a model on the remote device.

User can run examples at tests/python/contrib/test\_vsi\_npu with RPC verification. The model running result on device will be verified against the result on host with same input.

• Launch the RPC server on the device

\$ python3 -m tvm.exec.rpc\_server --host 0.0.0.0 --port=9090

• Export the system variables:

```

$ export TVM_HOME=/path/to/tvm

$ export PYTHONPATH=$TVM HOME/python

```

• Run the specified models on the host PC:

```

$ python3 tests/python/contrib/test_vsi_npu/test_rpc_tflite_models.py -i

{device_ip} -m mobilenet_v2_1.0_224_quant

```

#### • Run all supported TensorFlow Lite models on the host PC:

```

$ python3 tests/python/contrib/test_vsi_npu/test_rpc_tflite_models.py -i

{device_ip}

```

**Note:** This test will download the model automatically, please be sure the network can access the public internet. Example scripts may import additional Python libraries. Please check scripts and make sure they are installed correctly.

```

IMXMLUG

User guide

```

To test pytorch/onnx/keras model, additional python packages needs to be installed on the host PC:

```

$ python3 -m pip install torch==1.7.0 torchvision==0.8.1

$ python3 -m pip install onnx=1.8.1 onnxruntime==1.8.1

$ python3 -m pip install tensorflow==2.5.0

```

#### 6.2.2 Running example individually on device

In this mode, the model is compiled on the host offline and saved as model.so. Please refer tests/python/ contrib/test\_vsi\_npu/compile\_tflite\_models.py to compile a TensorFlow Lite model on the host.

Below script snippet shows how to load and run a compiled model at the device:

```

ctx = tvm.cpu(0)

# load the compiled model

lib = tvm.runtime.load_module(args.model)

m = graph_runtime.GraphModule(lib["default"](ctx))

# set inputs

data = get_img_data(args.image, (args.input_size, args.input_size),

args.data_type)

m.set_input(args.input_tensor, data)

# execute the model

m.run()

# get outputs

tvm_output = m.get_output(0)

```

Please refer tests/python/contrib/test\_vsi\_npu/label\_image.py to a complete label image example with pre-processing of image decoding and post-processing to generate label.

#### 6.3 How to build TVM stack on host

Conceptually, TVM can be split into two parts:

- TVM build stack: compiles the deep learning model at host

- · TVM runtime: loads and interprets the model at device

This build stack is using the LLVM to cross-compile the generated source as a deployable dynamic library for device. Please, follow the <u>LLVM Doc</u> to install LLVM on the host. If installed successfully, llvm-config should be found under /usr/bin.

To build the tvm, please be sure below dependence packages installed on the host:

- cmake

- python3-dev

- build-essential

- Ilvm-dev

- g++-aarch64-linux-gnu

- libedit-dev

- libxml2-dev

- python3-numpy

- python3-attrs

- python3-tflite

For Ubuntu 18.04, the user could use below commands to install all dependences:

\$ sudo apt-get update

#### i.MX Machine Learning User's Guide

```

$ sudo apt-get install -y python3 python3-dev python3-setuptools

$ sudo apt-get install -y cmake llvm llvm-dev g++-aarch64-linux-gnu gcc-aarch64-

linux-gnu

$ sudo apt-get install -y libtinfo-dev zliblg-dev build-essential libedit-dev

libxml2-dev

$ python3 -m pip install numpy decorator scipy attrs six tflite

```

Follow below instructions to build TVM stack on the host:

```

$ export TOP_DIR=`pwd`

$ git clone --recursive <u>https://github.com/nxp-imx/eiq-tvm-imx/</u> tvm-host

$ cd tvm-host

$ mkdir build

$ cp cmake/config.cmake build

$ cd build

$ sed -i 's/USE_LLVM\ OFF/USE_LLVM\ \/usr\/bin\/llvm-config/' config.cmake

$ cmake ..

$ make tvm -j4 # make tvm build stack

```

# 6.4 Supported models

Table 2. TVM models ZOO

The following models are verified with TVM.

| Model                  | float32               | int8                            | Input size |

|------------------------|-----------------------|---------------------------------|------------|

| mobilenet_v1_0.25_128  | mobilenet_v1_0.25_128 | mobilenet_v1_0.25_128_<br>quant | 128        |

| mobilenet_v1_0.25_224  | mobilenet_v1_0.25_224 | mobilenet_v1_0.25_224_<br>quant | 224        |

| mobilenet_v1_0.5_128   | mobilenet_v1_0.5_128  | mobilenet_v1_0.5_128_<br>quant  | 128        |

| mobilenet_v1_0.5_224   | mobilenet_v1_0.5_224  | mobilenet_v1_0.5_224_<br>quant  | 224        |

| mobilenet_v1_0.75_128  | mobilenet_v1_0.75_128 | mobilenet_v1_0.75_128_<br>quant | 128        |

| mobilenet_v1_0.75_224  | mobilenet_v1_0.75_224 | mobilenet_v1_0.75_224_<br>quant | 224        |

| mobilenet_v1_1.0_128   | mobilenet_v1_1.0_128  | mobilenet_v1_1.0_128_<br>quant  | 128        |

| mobilenet_v1_1.0_224   | mobilenet_v1_1.0_224  | mobilenet_v1_1.0_224_<br>quant  | 224        |

| mobilenet_v2_1.0_224   | mobilenet_v2_1.0_224  | mobilenet_v2_1.0_224_<br>quant  | 224        |

| inception_v1           | N/A                   | inception_v1_224_quant          | 224        |

| inception_v2           | N/A                   | inception_v2_224_quant          | 224        |

| inception_v3           | inception_v3          | inception_v3_quant              | 299        |

| inception_v4           | inception_v4          | inception_v4_299_quant          | 299        |

| deeplab_v3_257_mv_gpu  | deeplab_v3_256_mv_gpu | N/A                             | 257        |

| deeplab_v3_mnv2_pascal | N/A                   | deeplab_v3_mnv2_pascal          | 513        |

IMXMLUG User guide © 2024 NXP B.V. All rights reserved.

| Table 2. TVM models ZOOcontinued |                                        |      |            |

|----------------------------------|----------------------------------------|------|------------|

| Model                            | float32                                | int8 | Input size |

| ssdlite_mobiledet                | ssdlite_mobiledet_cpu_<br>320x320_coco | N/A  | 320        |

# 7 NN Execution on Hardware Accelerators

#### 7.1 Hardware acceleration on i.MX 8 Series

#### 7.1.1 Hardware accelerator description

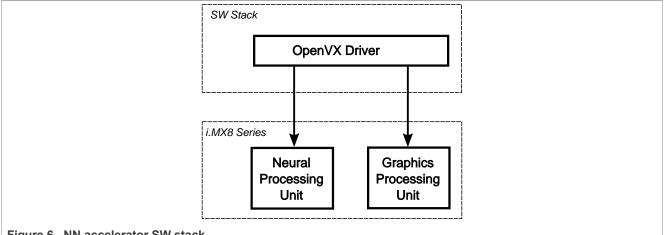

The i.MX 8 class devices are deployed with two kind of NN accelerators (see also the figure below):

- Neural Processing Unit (NPU)

- Graphics Processing Unit (GPU)

Neural processing unit is optimized for fixed point arithmetic, in 8-bit and 16-bit width. For optimal performance on the NPU, quantized models shall be used.

Graphics processing unit is optimized for fixed point arithmetic and half precision floating point arithmetic. For optimal performance on the GPU, quantized models or floating-point models with half precision shall be used.

#### Note:

The TensorFlow Lite framework enables to compute the floating-point models directly in 16-bit half precision arithmetic.

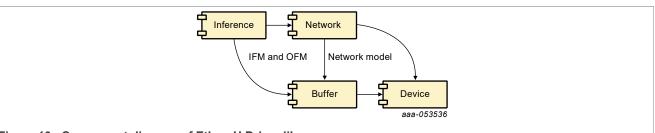

Figure 6. NN accelerator SW stack

Interface to NPU/GPU HW accelerator is provided via the OpenVX v1.3 with NN Extensions. OpenVX is an open, royalty-free standard for cross platform acceleration of computer vision applications. It provides:<sup>2</sup>

- A library of predefined and customizable vision functions

- · A graph-based execution model to combine function enabling both task and data independent execution

- A set of memory objects that abstract the physical memory

Open VX defines a C-application programming interface for building, verifying and coordinating graph execution and accessing memory objects. More information about OpenVX can be find on the OpenVX <u>home page</u>.

#### Note:

<sup>2</sup> OpenVX 1.3 specification: https://registry.khronos.org/OpenVX/specs/1.3/html/OpenVX\_Specification\_1\_3.html

*In the current OpenVX driver implementation, the maximum number of nodes supported in OpenVX graph is 2048.*

#### 7.1.2 Profiling on hardware accelerators

This section describes how to enable profiler on the GPU/NPU, and how to capture logs.

- 1. Stop the EVK board in the U-Boot by pressing Enter.

- 2. Update mmcargs by adding galcore.showArgs=1 and galcore.gpuProfiler=1.

```

u-boot=> editenv mmcargs

edit: setenv bootargs ${jh_clk} ${mcore_clk} console=${console} root=

${mmcroot} galcore.showArgs=1 galcore.gpuProfiler=1

u-boot=> boot

```

- 3. Boot the board and wait for the Linux OS prompt.

- 4. The following environment flags should be enabled before executing the application.

VIV\_VX\_DEBUG\_LEVEL and VIV\_VX\_PROFILE flags should always be 1 during the process of profiling. The CNN\_PERF flag enables the driver's ability to generate per layer profile log. NN\_EXT\_SHOW\_PERF shows the details of how compiler estimates performance and determines tiling based on it.

export CNN PERF=1 NN EXT SHOW PERF=1 VIV VX DEBUG LEVEL=1 VIV VX PROFILE=1

- 5. Capture the profiler log. We use the sample ML example part of standard NXP Linux release to explain the following section.

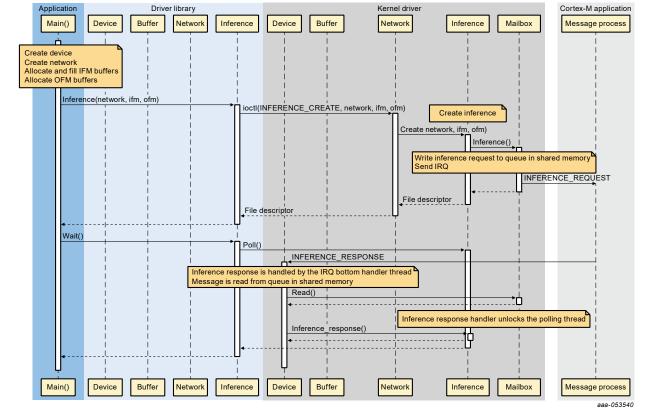

- TensorFlow Lite profiling