# NXP RELEASES NEW VOLTAGE LEVEL TRANSLATORS – NEXT GENERATION OF INNOVATION IMPROVES SYSTEM PERFORMANCE

### **Featured Speakers:**

#### **Steve Blozis**

Global Product Marketing Manager BU Secure Interfaces and Power, High-Performance Analog

#### **Emmanuel Nana**

Technical Marketing Manager

BU Secure Interfaces and Power

## WHAT IS LEVEL TRANSLATION AND WHY IT'S SO ESSENTIAL?

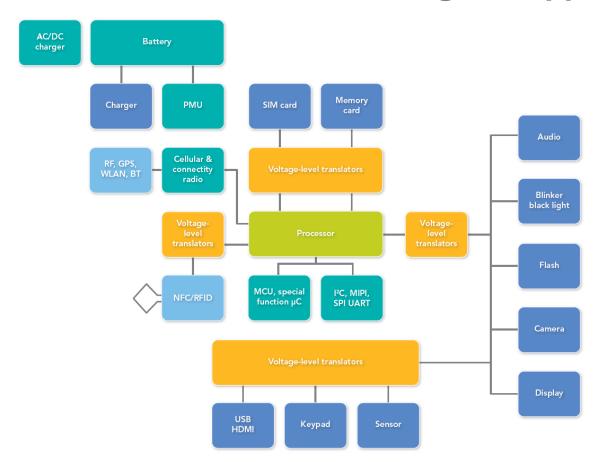

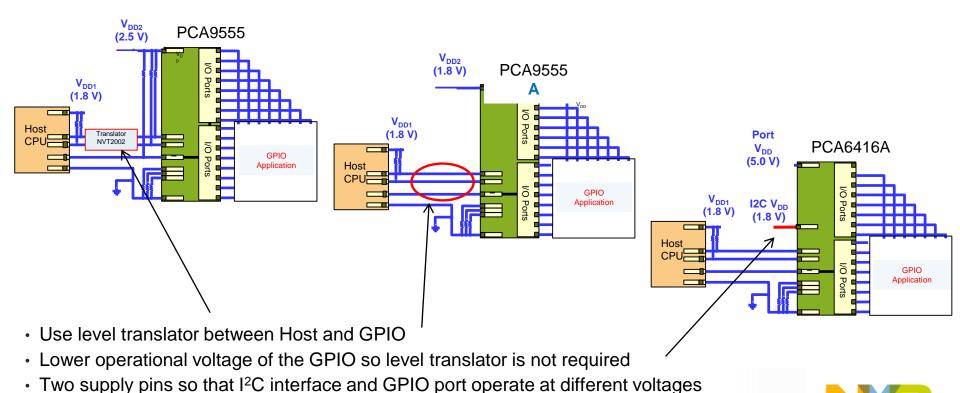

### **Level Translators Applications**

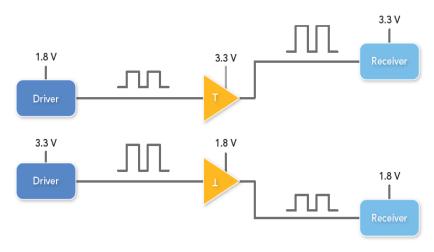

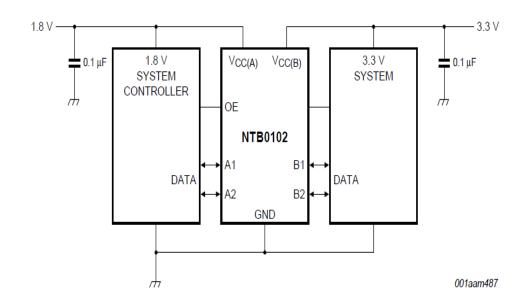

Figure 1-2. Shifting the output voltage level up or down

#### A quick overview

In most mixed-voltage designs, the output voltage level of a driver device needs to be shifted up or down so that the receiver device can interpret it correctly, or vice versa (Figure 1-2).

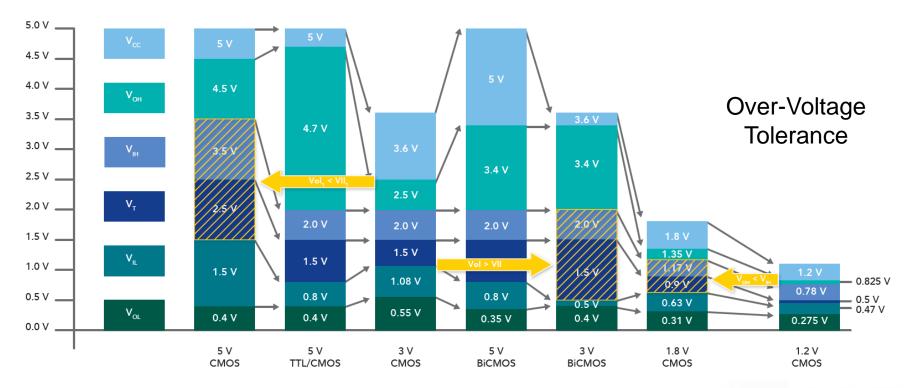

There are often variations in the logic switching input ( $V_{IH}$  and  $V_{IL}$ ) and the output levels ( $V_{OH}$  and  $V_{OL}$ ) for commonly used logic devices in the range of 3 and 5 V (Figure 1-3).

## **Level Translators Applications**

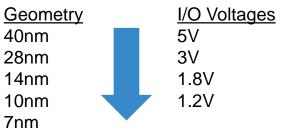

### Trend: Digital IC's Driving for Lower Voltages & Lower Power

Result: More opportunities for Level Translators; peripherals aren't changing as quickly

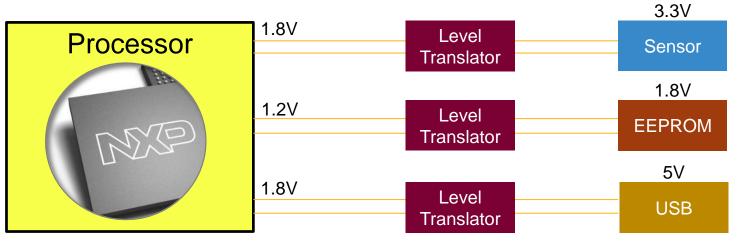

Level Translators are needed to support new lower voltage nodes to interface into legacy higher voltage nodes.

## **Level Translators Service Wide Range of Applications**

## HOW IS LEVEL TRANSLATION ACCOMPLISHED?

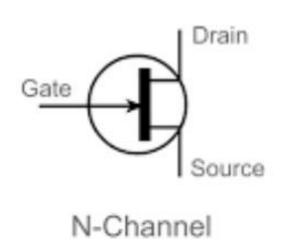

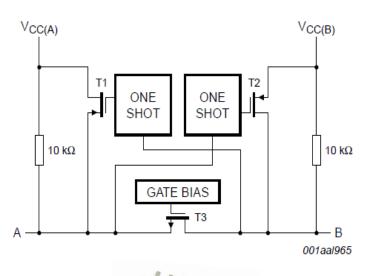

### **Level Translation - FET or Buffer**

- Biased gate cuts off high voltage

- Allows bi-directional translation without control pin

- Any open drain or push pull application

- Different voltage domains for A and B port

- Needs direction control

- Push pull application shown

## WHAT ARE THE OFFERINGS FROM NXP?

## **Voltage Level Translator Types and Features**

#### **I2C Family**

#### Features:

- Single and Dual supply

- Bidirectional

- Auto-sensing

- Capacitive isolation

- High noise margin

- SCL/SDA 2 bits

#### Applications

- I<sup>2</sup>C buffering

- Long cable

- Hot-swap

#### **FET Family**

#### Features:

- Dual supply

- Bidirectional

- Auto-sensing

- Passive

- OD or PP

- External pull-ups required

- 1 10 bits wide

#### Applications

- Control interfaces

- I<sup>2</sup>C-bus

#### **NTS Family**

#### Features:

- Dual supply

- Bidirectional

- · Auto-sensing

- Passive

- OD or PP

- Integrated Pull up resistors

- 1 8 bits wide

#### Applications

- Control Interfaces

- I<sup>2</sup>C-bus

- ш.

#### **NTB Family**

#### Features:

- Dual supply

- Bidirectional

- Auto-sensing

- Isolates capacitance

- Push-pull only

- Low output drive

- 1 8 bits wide

#### **Applications**

Control interfaces with active drive

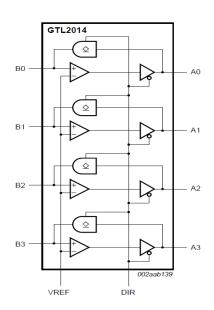

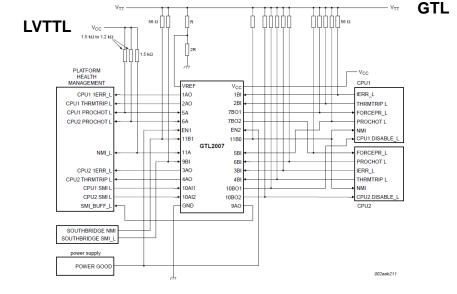

#### **GTL Family**

#### Features:

- · Supports 'GTL' logic

- Dual supply

- Bidirectional

- Direction Pin

- Isolates capacitance

- GTL to LVTTL level translation OD to PP

- 1 8 bits wide

#### Applications

Supports GTL levels on Intel-processors

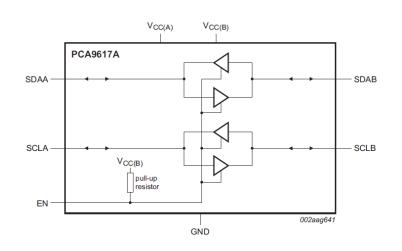

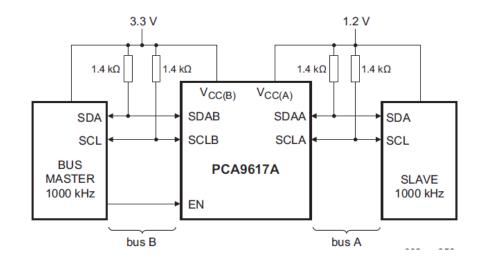

## I<sup>2</sup>C Level Translating Buffer (Direction Sensing)

- I<sup>2</sup>C-bus up to 1 MHz

- Bi-directional with static offset on B Port for direction control

- Decided for I<sup>2</sup>C but can be used for any OD or PP application

- A Port works 0.8 V to 5.5 V

- B Port works 2.3 V to 5.5 V

- Different domains Pull up resistor to rail

- Master and or slaves in any combination on either side

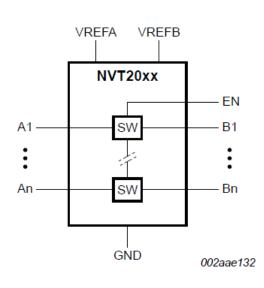

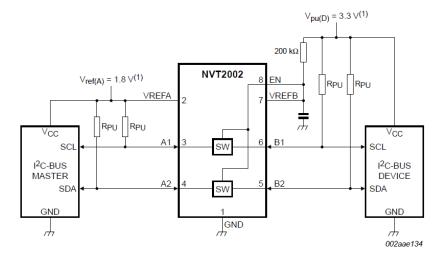

## I<sup>2</sup>C Level Translating FET (Direction Sensing)

- I2C-bus up to 3.4 MHz RC time constant

- Bidirectional without control pin

- Any open drain or push pull application

- The applied voltages at V<sub>ref(A)</sub> and V<sub>pu(D)</sub> should be such that V<sub>ref(B)</sub> is at least 1 V higher than V<sub>ref(A)</sub> for best translator operation.

- VREFA works 1.0V to 4.5V

- VREFB works 2.0V to 5.5V

- Lowest voltage clamps Vol pull up resistor to rail

- Master and or slaves in any combination on either side

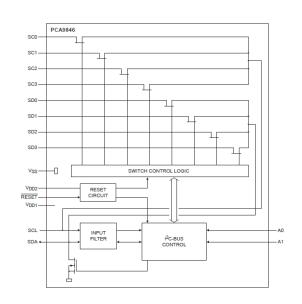

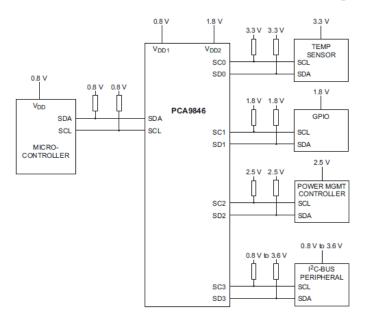

## I<sup>2</sup>C Level Translating Mux (Direction Sensing)

- I<sup>2</sup>C-bus up to 1 MHz

- Bidirectional without control pin

- Only for I<sup>2</sup>C-bus application

- VDD1 works 0.8 V to 3.6 V

- VDD2 works 1.65 V to 3.6 V

- Lowest voltage clamps Vol pull up resistor to rail

- Master and or slaves in any combination on either side but need master on "inlet" to control state machine

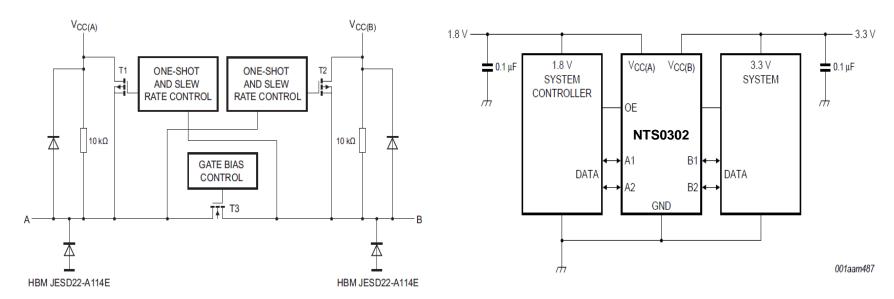

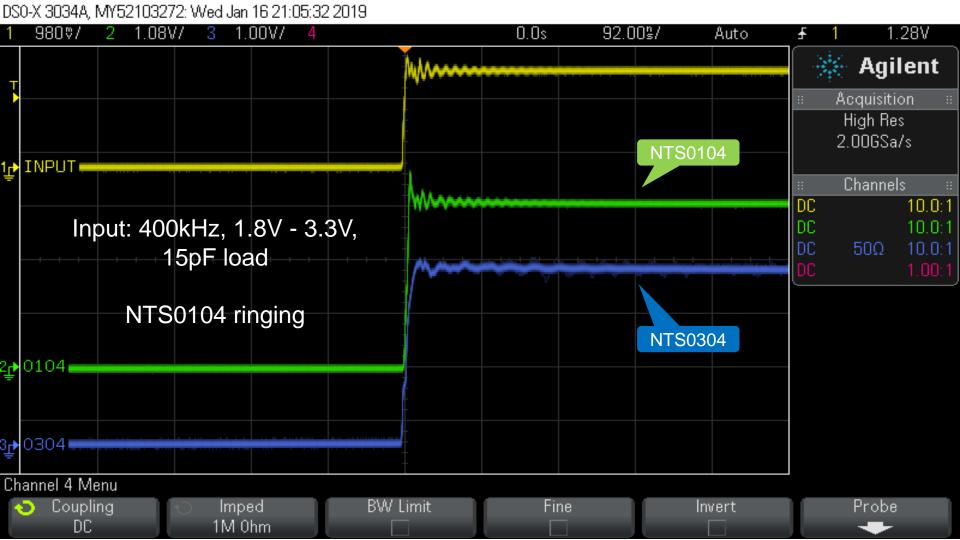

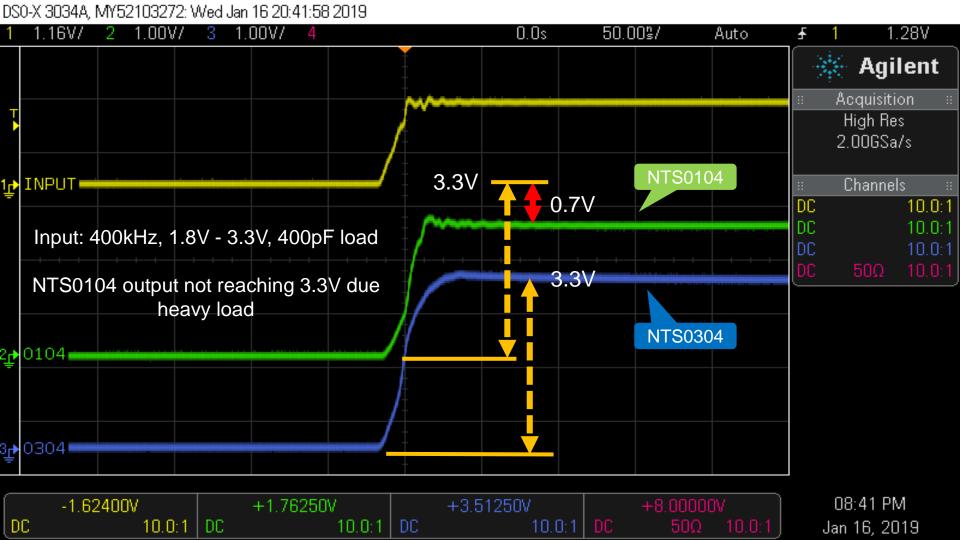

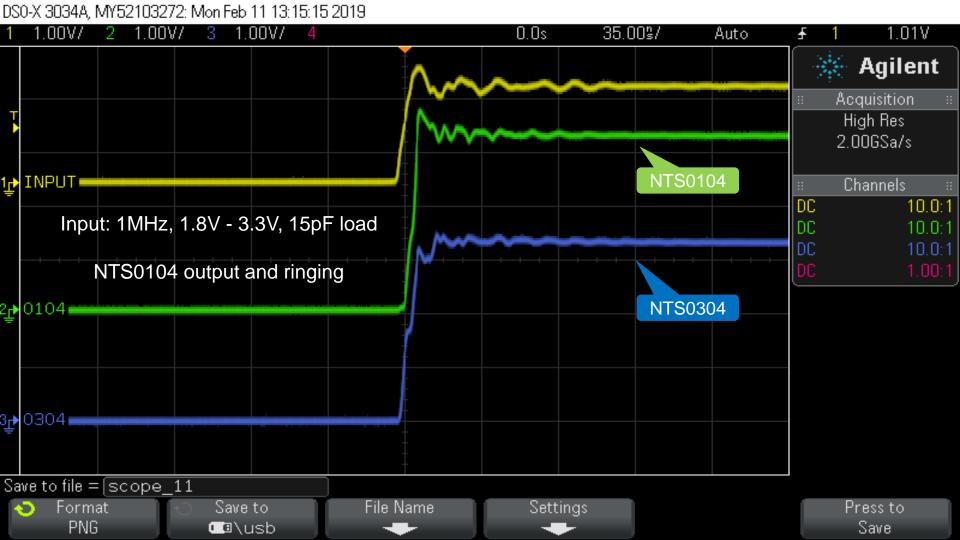

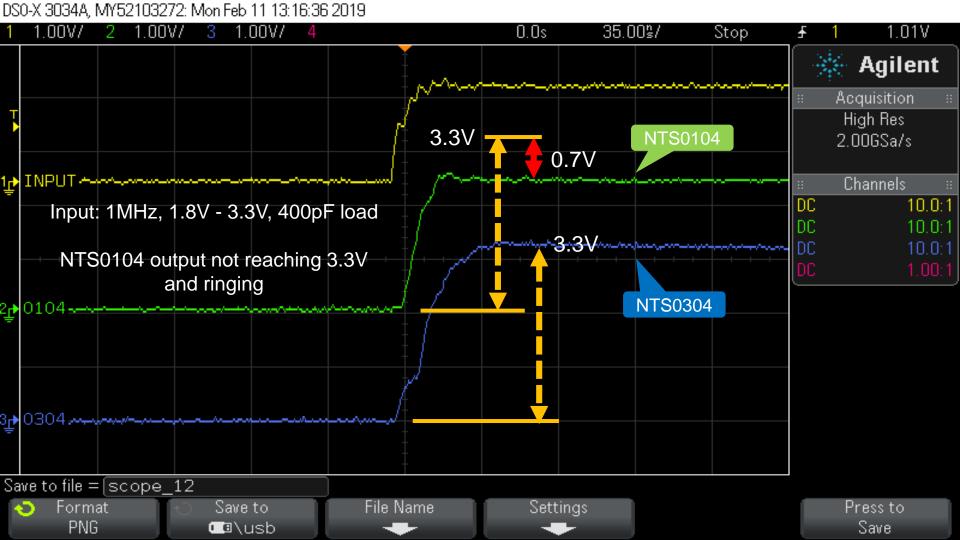

## I<sup>2</sup>C Level Translating FET with one shot (Direction Sensing)

- I2C-bus up to 2MHz

- One shot potential ringing

- Bidirectional without control pin

- Any open drain or push pull application

- A Port works 0.95V to 3.6V

- B Port works 1.65V to 5.5V

- Lowest voltage clamps Vol internal (or external) pull up resistor to rail and one shot

- Master and or slaves in any combination on either side

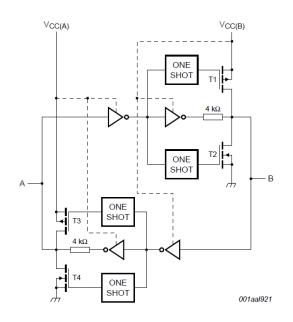

### Level Translating Buffer with One Shot (Direction Sensing)

- Can not be used for I<sup>2</sup>C-bus

- Bi-directional without control pin Weak output overdriven during reverse in direction

- Can be used for push pull application

- A Port works 1.2 V to 3.6 V

- B Port works 1.65 V to 5.5 V

- Buffer pulls to rail one shot high and low

- Master and or slaves in any combination on either side

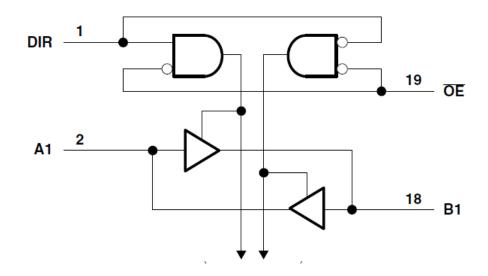

## Level Translating Logic Buffer (No Direction Sensing)

- Can not be used for I<sup>2</sup>C-bus

- **Direction pin** for control

- Can be used for open drain or push pull application

- A Port works 3.0 V to 3.6 V not 5V tolerant

- B Port works to 3.6 V threshold set by 2/3 of VTT

- A Port LVTTL Buffer pulls to rail

- B Port open drain pull up resistor to VTT (1.2 V)

- Standard logic is LVTTL both sides

## Level Translating Logic Buffer (No Direction Sensing)

## WHAT ARE THE ADVANTAGES OF NXP'S VLT?

## Introducing the NTS030x Level Translator

Wide & Ultra-Low Voltage VCC(A): 0.95 V to 3.6 V & VCC(B): 1.65 V to 5.5 V

8 kV System-Level ESD Protection (B-Port of 4 and 8-Ch)

"Smart" One-Shot 50 ns Pulse & EMI Rejection

Complete Family 1, 2, 4, and 8-Ch Level Translators

## Q&A

## **Level Translation Applications**

## FOR MORE INFO PLEASE CONTACT STEPHEN.BLOZIS@NXP.COM