# Freescale Semiconductor RDB Board Specification

Document Number: P1025RDB-PA Agile # UMS-26826 2.0, 08/2011

# P1025RDB-PA Specification

# **QorIQ Integrated Communications Processor**

The reference design board (RDB) is a system featuring the P1025E QorIQ processor, which includes a built-in security accelerator and QUICC Engine. This low-cost, high-performance system solution consists of a printed circuit board (PCB) assembly and a software board support package (BSP). This BSP enables the fastest possible time-to-market for development or integration of applications including printer engines, broadband gateways, no-new-wires home adapters/access points, and home automation boxes.

This document describes the hardware features of the board including specifications, block diagram, connectors, interfaces, and hardware straps. It also describes the board settings and physical connections needed to boot the RDB. Finally, it considers the software shipped with the platform.

When you finish reading this document, you should be familiar with:

- The board layout and its interfaces

- The board configuration options

- How to get started and boot the board

#### Contents

| 1  | Introduction                                   |   |

|----|------------------------------------------------|---|

| 2  | P1025RDB Hardware                              |   |

| 3  | Memory Interface                               |   |

| 4  | SerDes Interfaces (PCIe/SGMII)                 |   |

| 5  | Enhanced Local Bus Controller (eLBC) Interface |   |

| 6  | Ethernet                                       | 1 |

| 7  | eSPI                                           | 1 |

| 8  | eSDHC Interface                                | 1 |

| 9  | GPIO                                           | 1 |

| 10 | I <sup>2</sup> C                               | 1 |

| 11 | USB Interface                                  | 2 |

| 12 | Dual RS-232 Ports                              | 2 |

| 13 | Lattice PLD                                    | 2 |

| 14 | POR Configuration                              | 2 |

| 15 | JTAG/COP                                       | 2 |

| 16 | Interrupts                                     | 2 |

| 17 | DMA                                            | 2 |

| 18 | RS485                                          | 2 |

| 19 | PMC                                            | 2 |

| 20 | Connectors, Headers, Push Buttons and LEDs     | 2 |

| 21 | Power Related                                  | 3 |

| 22 | 1588                                           | 3 |

| 23 | Clocking                                       | 3 |

| 24 | Reset                                          | 3 |

| 25 | Switch Settings                                | 3 |

| 26 | Getting Started                                | 4 |

| 27 | Danisian III-tama                              | 4 |

This document contains information on a product under development. Freescale reserves the right to change or discontinue this product without notice.

© Freescale Semiconductor, Inc., 2011. All rights reserved.

Introduction

## 1 Introduction

This document is applicable for PCBA Rev2.0 and PLD Rev2.6. The revision information is shown in the log file of board booting.

# 1.1 Acronyms and Abbreviations

Table 1 lists commonly used acronyms and abbreviations.

Table 1. Acronyms and Abbreviations

| COP  | Debug Port in Powerpc       | PHY    | Physical Layer Interface Device |

|------|-----------------------------|--------|---------------------------------|

| DDR  | Double Data Rate DRAM       | PLL    | Phase Lock Loop                 |

| LYNX | High Speed Serial Interface | SERDES | Serializer/Deserializer         |

| PCIe | PCI Express®                | USB    | Universal Serial Bus            |

| QE   | QUICC Engine                | TDM    | Time Division Multiplex         |

#### 1.2 Reference Documents

The following documents are available on Freescale's intranet library.

- P1025E QorIQ Integrated Processor Family Reference Manual

- P1025E QorIQ Integrated Processor Hardware Specification

## 2 P1025RDB Hardware

This section covers the features, block diagram, specifications, and mechanical data of the RDB.

### 2.1 P1025E Features

The board features are as follows:

- P1025E running at 533 MHz, platform 266 MHz, DDR3 667 MHz

- Memory subsystem:

- 1Gbyte unbuffered DDR3 SDRAM discrete devices (32-bit bus)

- 16 Mbyte NOR flash single-chip memory

- 32 Mbyte NAND flash memory

- 256 Kbit M24256 I2C EEPROM

- 16 Mbyte SPI memory

- SD connector to interface with the SD memory card

- Interfaces:

- PCIe

- x1 PCIe slot

- x1 mini-PCIe slot

- 10/100/1000 BaseT Ethernet ports:

- eTSEC1, RGMII: one 10/100/1000 port using Atheros<sup>™</sup> AR8021

- eTSEC2, SGMII: one 10/100/1000 port using Vitesse<sup>™</sup> VSC8221

- eTSEC3, RGMII: one 10/100/1000 port using Atheros<sup>™</sup> AR8021

- 10/100 BaseT Ethernet ports:

- UEC1,MII: one 10/100 port using Micrel<sup>™</sup> KSZ8041

- UEC5,RMII: one 10/100 port using Micrel<sup>™</sup> KSZ8041

- USB 2.0 port:

- ULPI PHY interface: SMSC USB3300 USB PHY and Genesys Logic's GL850A USB2.0 HUB Controller with 4 downstream ports

- Two USB 2.0 Type A receptacles

- One USB 2.0 signal to Mini PCIe slot

- Dual RJ45 UART ports:

- DUART interface: Supports two UARTs up to 115200 bps for console display

- Two 10-Pin RJ45 RS485 ports

- Both ports are full duplex mode

- Board connectors:

- Open frame power supply connector

- JTAG/COP for debugging

- PMC connector

- UMI(PLC)connector

- IEEE Std. 1588<sup>TM</sup> signals for test and measurement

- Real-time clock on I<sup>2</sup>C bus

- PCB

- 6-layer routing (4-layer signals, 2-layer power and ground)

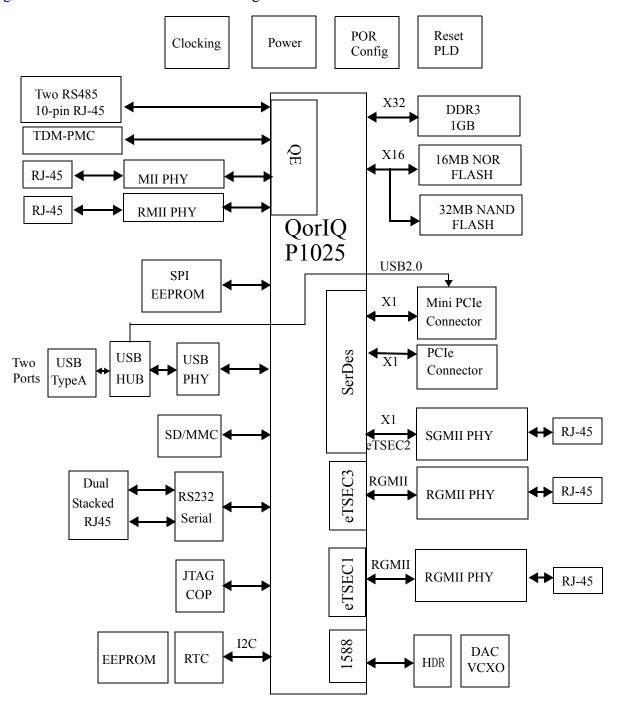

#### P1025RDB Hardware

Figure 1 shows the P1025RDB block diagram.

Figure 1. Block Diagram

# 2.2 Specifications

Table 2 lists the specifications of the P1025RDB.

**Table 2. RDB Specifications**

| Characteristics                                 | Specifications                                              |

|-------------------------------------------------|-------------------------------------------------------------|

| Chassis Power requirements                      | Typical Maximum 40W 90~264VAC input open frame power supply |

| Communication processor                         | P1025E cores running at 533 MHz                             |

| Operating temperature                           | 0° C to 70° C (room temperature)                            |

| Storage temperature                             | -25°C to 85°C                                               |

| Relative humidity                               | 5% to 90% (noncondensing)                                   |

| PCB dimensions:<br>Length<br>Width<br>Thickness | 8860 mil<br>8270 mil<br>62 mil                              |

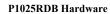

# 2.3 Mechanical Data

Figure 2 shows the P1025RDB-PA dimensions. The board measures 225 mm  $\times$  210 mm (8860 mil  $\times$  8270 mil)

Figure 2. Dimensions of the RDB

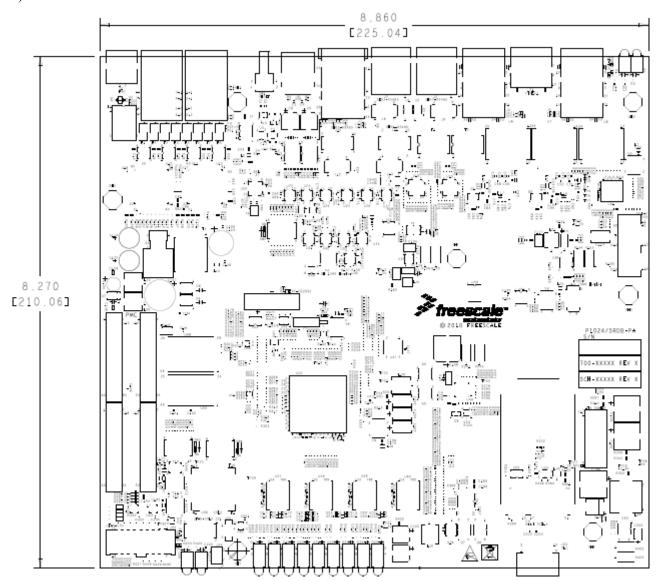

# **3** Memory Interface

## 3.1 Description

The memory interface on the RDB is configured as DDR3 and is implemented as a single bank discrete chips(x8). ECC is not supported on the design. The memory size supported on the board is shown in Table 3.

Table 3. Memory Size

| P1025RDB-PA<br>(32-bit)              |

|--------------------------------------|

| 1GB<br>(4 chips * 2Gbit chips)/8bits |

The PCB design is capable of running up to a clock rate of up 333 MHz (667 MHz data rate). The actual and final speed of the memory design is determined by the final supported DDR3 frequency of the processor.

The DDR3 interface uses the SSTL driver/receiver and 1.5 V power. A Vref 1.5 V/2 is needed for all SST L receivers in the DDR3 interface. For details on DDR3 timing design and termination, refer to the Freescale application note entitled *Hardware and Layout Design Considerations for DDR Memory Interfaces (AN2582)*

Signal integrity test results show this design does not require terminating resistors (series resistor ( $R_S$ ) and termination resistor ( $R_T$ )) for the discrete DDR3 devices used. DDR3 supports on-die termination; the DDR3 chips and P1025E are connected directly.

The interface is 1.5 V and is provided by an on-board voltage regulator. VREF, which is half the interface voltage, or 0.75 V, is supplied by the same voltage regulator.

SerDes Interfaces (PCIe/SGMII)

Figure 3 shows the DDR3 SDRAM controller connection.

Figure 3. DDR3 SDRAM Connection

## 3.2 Termination

The DDR3 address, control, and command signals are terminated to the VTT rail via a 47 Ohm resistor.

# 4 SerDes Interfaces (PCIe/SGMII)

P1025E supports the SGMII and PCI Express high-speed I/O interface standards.

Table 4 details the SerDes connections.

**Table 4. SerDes Connectivity**

| SerDes Lane | Mode          | Connected to          | Comment                                                   |

|-------------|---------------|-----------------------|-----------------------------------------------------------|

| Lane 0      | PCI Express 1 | Mini-PCIe slot        | Used for WLAN type cards                                  |

| Lane 1      | PCI Express 2 | Standard x1 PCIe slot | PCIe Slot is only intended for cards that are 10W or less |

P1025RDB-PA Specification, 2.0

| Table 4. SerDes | Connectivity |

|-----------------|--------------|

|-----------------|--------------|

| SerDes Lane | Mode     | Connected to      | Comment |

|-------------|----------|-------------------|---------|

| Lane 2      | SGMII    | Vitesse SGMII PHY |         |

| Lane 3      | not used | not used          |         |

### **4.1 PCIe**

On the RDB, lanes 0 and 1 are configured as two independent x1 PCI Express Interfaces. These interfaces are compliant with the PCI Express Base Specification Revision 1.0a. The physical layer of the PCI Express interface operates at a transmission rate of 2.5 Gbaud (data rate of 2.0 Gbps) per lane. The theoretical unidirectional peak bandwidth is 2 Gbps per lane. Receive and transmit ports operate independently, resulting in an aggregate theoretical bandwidth of 4 Gps per lane.

### 4.2 SGMII

Lane 2 is used in the serial gigabit media independent interface (SGMII).SGMII is a high-speed interface linking the Ethernet controller with an Ethernet PHY. SGMII uses differential signalling for electrical robustness. It requires only four signals: receive data and its inverse, and send data and its inverse.

Lane 3 of the SerDes Interface is not used on the card.

# 4.3 SerDes Clocking

The clocking for the SerDes interface is 100MHz provided by the PI6C557-05 clock chip.

# 5 Enhanced Local Bus Controller (eLBC) Interface

The eLBC port connects to a wide variety of external memories, DSPs, and ASICs.

Three state-machines, the GPCM, UPM, and FCM, share the same external pins and can be programmed separately to access different types of devices.

- GPCM, or general-purpose chip select machine, controls access to asynchronous devices using a simple handshake protocol.

- UPM, or user-programmable machine, can be programmed to interface with synchronous devices or custom ASIC interfaces.

- FCM, or NAND Flash control machine, further extends interface options.

Every chip select signal can be configured so that the associated chip interface is controlled by the GPCM, UPM, or FCM state-machine. All state-machines can reside in the same system.

#### Enhanced Local Bus Controller (eLBC) Interface

To interface with the standard memory device, an address latch is needed on the upper address bits since they are multiplexed with the data bus. The LALE is used as the latching signal. The followings modules are connected to the local bus:

- 16 Mbyte NOR flash memory

- 32 Mbyte NAND flash memory

- PLD (Lattice LCMXO1200C)

- PMC Connectors

## 5.1 NOR Flash Memory

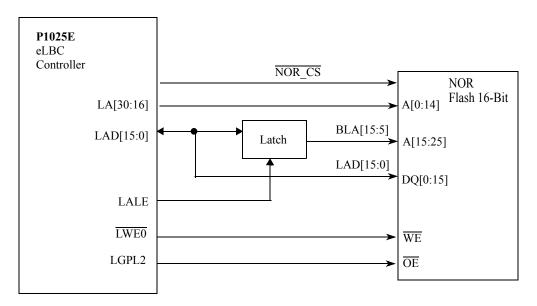

Through the general-purpose chip-select machine (GPCM), the P1025RDB provides 16Mbyte of flash memory. The flash memory used is configured in a 16-bit port size. Figure 4 shows the hardware connections for the flash memory.

\*NOTE:  $\overline{NOR}$  can be either  $\overline{CSO}$  or  $\overline{CS1}$  depending on boot location. See switch settings.

Figure 4. NOR Flash Connection

The NOR flash can be split into two logical halves by setting the FBANK\_SEL signal. The FBANK\_SE L signal is controlled by setting SW4[8]. Refer to Table 5 for details on changing the addresses using FBANK\_SEL.

| Setting  | NOR BANK used                                                 |

|----------|---------------------------------------------------------------|

| SW4[8]=0 | upper bank used for booting<br>starting at address 0xEFF80000 |

| SW4[8]=1 | lower bank used for booting<br>starting at address 0xEF780000 |

**Table 5. Logical NOR Banks**

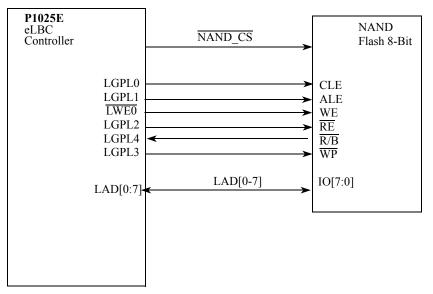

# 5.2 NAND Flash Memory

The P1025E has native support for NAND Flash memory through its NAND Flash control machine (FCM). The P1025RDB implements an 8-bit NAND Flash with 32 Mbyte in size. Figure 5 shows the NAND Flash connection.

\*NOTE: NAND\_CS can be either CSO or CS1 depending on boot location. See switch settings.

Figure 5. NAND Flash Connection

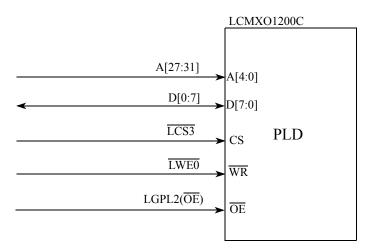

### 5.3 Lattice PLD

Lattic PLD LCMXO1200C is connected to the local bus of the processor. This gives the processor the ability to access the 8-bit registers in the PLD. For more details, refer to *P1025RDB-PA CPLD Specification-V0.3*. Figure 6 shows the connection between PLD and the P1025E.

P1025RDB-PA Specification, 2.0

#### Ethernet

Figure 6. Local Bus Connection of PLD

Table 6 summarizes the eLBC connectivity.

Table 6. eLBC Connectivity

| eLBC chip select                                                                                                                         | Manufacturer | Device          | Comment                              |

|------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------|--------------------------------------|

| LCS0 or LCS1 Assignment dependent on which device is used for booting. Handled automatically by the POR PLD based on the switch setting. | Spansion     | S29GL128P       | NOR FLASH Memory<br>16 Mbyte (16bit) |

| LCS0 or LCS1 Assignment dependent on which device is used for booting. Handled automatically by the POR PLD based on the switch setting. | Samsung      | K9F5608U0D-PCB0 | NAND Flash<br>32 Mbytes (8bit)       |

| LCS2                                                                                                                                     | Freescale    | PQ-MDS-T1       | PMC Card                             |

| LCS3                                                                                                                                     | Lattice      | LCMXO1200C      | PLD                                  |

| LCS4-LCS7                                                                                                                                | not used     | not used        |                                      |

# 6 Ethernet

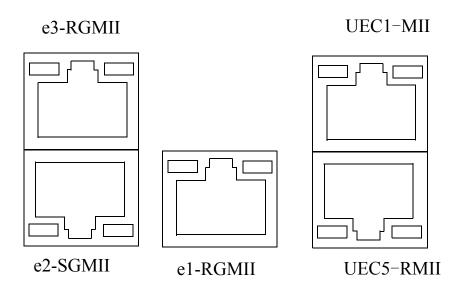

The RDB supports five Ethernet ports.

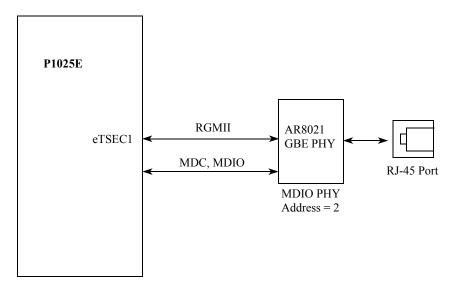

## **6.1 eTSEC1 10/100/1000 BaseT Interface**

eTSEC1 is set to operate in RGMII and is directly connected to the Atheros RGMII PHY (AR8021), as shown in Figure 7. This port can be used for WAN connectivity.

Figure 7. eTSEC1 Connection

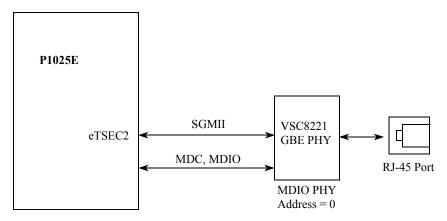

### **6.2** eTSEC2 10/100/1000 BaseT Interface

eTSEC2 is set to operate in SGMII and is directly connected to the Vitesse SGMII PHY (VSC8221), as shown in Figure 8. This port can be used for WAN connectivity.

Figure 8. eTSEC2 Connection

Freescale Semiconductor

P1025RDB-PA Specification, 2.0

Ethernet

14

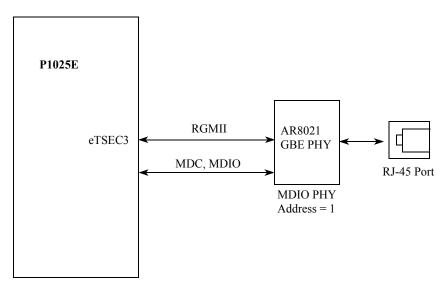

# **6.3 eTSEC3** 10/100/1000 BaseT Interface

eTSEC3 is set to operate in RGMII and is directly connected to the Atheros RGMII PHY (AR8021), as shown in Figure 9. This port can be used for WAN connectivity.

Figure 9. eTSEC3 Connection

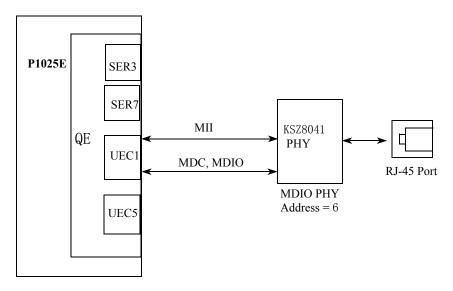

## 6.4 UEC1 10/100 BaseT Interface

UEC1 ,the 10/100M Ethernet controller is from QE and is connected to the Micrel PHY (KSZ8041), as shown in Figure 10.

Figure 10. UEC1 Connection

P1025RDB-PA Specification, 2.0

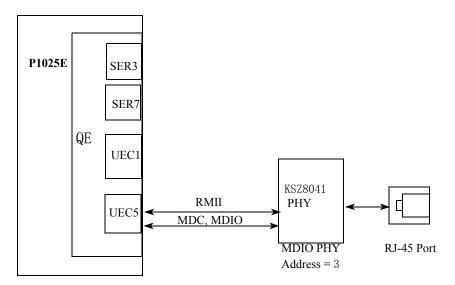

## 6.5 UEC5 10/100 BaseT Interface

UEC5 ,the 10/100M Ethernet controller is from QE and is connected to the Micrel PHY (KSZ8041), as shown in Figure 11.

Figure 11. UEC5 Connection

# **6.6** Ethernet Management

Table 7 give details of the MDC and MDIO connections on the RDB.

| Device     | PHY Address | Comment |

|------------|-------------|---------|

| eTSEC1 PHY | 00010       | AR8021  |

| eTSEC2 PHY | 00000       | VSC8221 |

| eTSEC3 PHY | 00001       | AR8021  |

| UEC1 PHY   | 00110       | KSZ8041 |

| UEC5 PHY   | 00011       | KSZ8041 |

Table 7. MDC/MDIO Connectivity

## **6.7** Ethernet Ports

Figure 12 shows how the ethernet ports are connected on the backside of the RDB chassis.

Figure 12. Ethernet Port Connectivity

## 7 eSPI

The eSPI is a full-duplex, synchronous, character-oriented channel that supports a four-wire interface (receive, transmit, clock, and slave select). The P1025E has the ability to boot from an SPI serial flash device. It also supports other peripheral devices conforming to the SPI standard. Some of the peripheral devices include real-time clocks and A/D converters devices.

On the RDB, a Spansion SPI flash memory is supported. Additionly, the SPI interface is also connected to 1588 test circuitry. Table 8 lists the eSPI connections.

eSPI Chip Select Manufacturer Part# Comment SPI CS0 N S25FL128P0XN Spansion 16MB Spansion SPI Flash SPI\_CS1\_N N/A N/A Not Used SPI\_CS2\_N N/A N/A Not Used SPI\_CS3\_N MCP4921 Microchip 12-bit DAC

**Table 8. eSPI Connectivity**

P1025RDB-PA Specification, 2.0

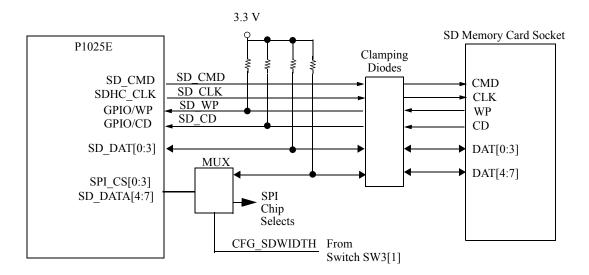

## 8 eSDHC Interface

The enhanced SD host controller (eSDHC) provides an interface between host system and SD/MMC cards. The secure digital (SD) card is specifically designed to meet the security, capacity, performance, and environmental requirements inherent in emerging audio and video consumer electronic devices. Booting from eSDHC interface is supported via the processor's on-chip ROM.

On the RDB, a single connector is used for both SD and MMC memory cards as shown in Figure 13.

Figure 13. SD Memory Card Connection

The SPI chip selects are multiplexed with the higher data nibble of SDHC interface signals. The selection between the two is controlled by the cfg\_sdwidth signal (switch3[1]). By default, cfg\_sdwidth = 0, thereby allowing SPI and a 4-bit SD/MMC interface to co-exist on the board.

When cfg\_sdwidth = 1, the on-board mux connects the upper data nibble to the SD/MMC connector. When doing this, the user must configure the processor in order to realize the increased bus width. Secondly, when used in this mode, SPI connectivity is not available.

Table 9 lists the multiplexed signals.

**Table 9. Multiplexed Signals**

| SPI Signal     | Alternative Signal |

|----------------|--------------------|

| SPI_CS0_B (IO) | SDHC_DAT4          |

| SPI_CS1_B (IO) | SDHC_DAT5          |

P1025RDB-PA Specification, 2.0

**GPIO**

**Table 9. Multiplexed Signals**

| SPI Signal     | Alternative Signal |

|----------------|--------------------|

| SPI_CS2_B (IO) | SDHC_DAT6          |

| SPI_CS3_B (IO) | SDHC_DAT7          |

# 9 GPIO

Table 10 lists the GPIO pin usage on the RDB platform.

Table 10. GPIO Pin Usage

| GPIO   | Input / Output | Signal Name    | Comment                                                                                      |

|--------|----------------|----------------|----------------------------------------------------------------------------------------------|

| GPIO07 | input          | LOAD_DEFAULT_N | Default configuration load request via pushing down Reset Switch SW1 for more than 6 seconds |

| GPIO11 | output         | WDI            | Periodic signal for Watchdog MAX6370 (U65) input                                             |

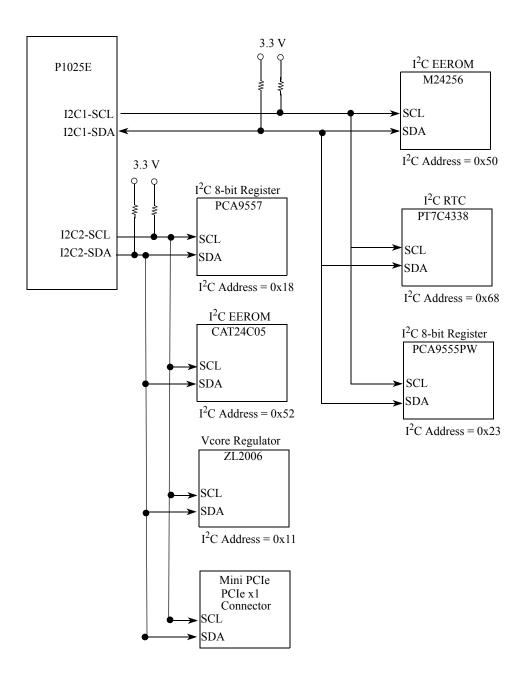

# $10 I^2C$

The P1025E device has two I<sup>2</sup>C controllers. On the RDB, the I2C buses are connected as shown in Figure 14. The M24256 serial EEPROM can be used to store configuration registers' values and/or user program if the P1025E boot sequencer is enabled. For details about the boot sequencer mode, refer to the P1025E reference manual. By default, the boot sequencer is not used and the boot code and initialization for the board is loaded from the local bus flash memory.

Figure 14. I<sup>2</sup>C Connection

**Table 11. I2C Bus Connections**

| I2C Bus | I2C Address | Manufacturer        | Device                            | Comment                         |

|---------|-------------|---------------------|-----------------------------------|---------------------------------|

| I2C1    | 50H         | ST Microelectronics | M24256                            | Boot sequencer eeprom 2 56Kbits |

| I2C1    | 68H         | Pericom             | PT7C4338                          | Real time clock                 |

| I2C2    | 11H         | Zilker              | ZL2006                            | Vcore Regulator                 |

| I2C2    | 18H         | NXP                 | PCA9557                           | 8-bit I2C register              |

| I2C2    | 52H         | ON-SEMICONDUCTOR    | CAT24C05                          | SPD EEPROM<br>4Kbits            |

| I2C2    |             |                     | Mini PCIe<br>PCIe x1<br>Connector |                                 |

| I2C2    | 23H         | NXP                 | PCA9555PW                         | QE switch Configure             |

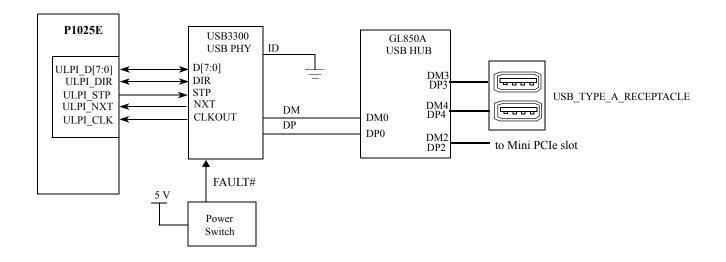

# 11 USB Interface

The USB interface is configured to operate as a standalone host. To complete the USB interface, an external PHY is employed and connected to the processor's ULPI signals. The SMSC USB3300 PHY is used on the RDB. Four downstream ports, and one upstream port USB Hub Genesys Logic GL850A is connected to the USB PHY to expand the USB ports.

#### The board features:

- High-speed (480 Mbps), full-speed (12 Mbps) and low-speed (1.5 Mbps) operation

- Host mode

- Dual stacked Type A connection

- One port connected to Mini PCIe connector

Figure 15 illustrates how the USB connectivity is implemented on the RDB.

Figure 15. USB Interface

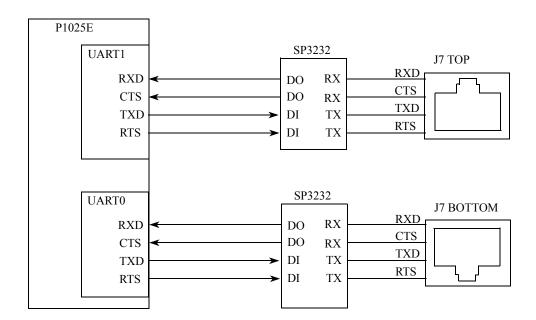

#### 12 **Dual RS-232 Ports**

The P1025E device has two UART controllers. The RS-232 interface provides an RS-232 standard interconnection between the card and an external host. The serial connection is typically configured to run at 115.2 Kbps.

Each UART supports:

- Full-duplex operation.

- Software-programmable baud generators:

- Divide the input clock by 1 to (216-1)

- Generate a 16x clock for the transmitter and receiver engines

- Clear-to-send (CTS) and ready-to-send (RTS) modem control functions.

- Software-selectable serial interface data format that includes:

- Data length

- Parity

- 1/1.5/2 STOP bit

- Baud rate

- Overrun, parity, and framing error detection.

The UART ports are routed to dual stacked RJ45 connectors J7 as shown in Figure 16. UART0 is used as default port.

P1025RDB-PA Specification, 2.0 Freescale Semiconductor 21

#### **Dual RS-232 Ports**

Figure 16. RS-232 Debug Ports Connection

Table 12 lists the connectivity for the UART RJ45 to DB9 female cable connections.

RJ45 Pin# RS-232 Signal **DB9 Female Pin#** RTS 8 1 2 NC TXD 2 3 4 **GND** 5 **GND** 5 6 3 **RXD** 7 NC 8 7 CTS

**Table 12. UART Connections**

## 13 Lattice PLD

The Lattice PLD (U56) is used for power up sequence control, system reset, POR configuration, multiplexed function select and LEDs control. For details, refer to *P1025RDB-PA CPLD Specification-V0*. 3.

# 14 POR Configuration

# 14.1 POR Configuration PLD

The POR configuration PLD drives the appropriate configuration signals to the processor based on the selected configuration switch setting. When hard reset (HRESET) is asserted, the POR config PLD begins to drive the POR config signals to the processor. The config signals remain asserted until the POR config signals have been properly latched by the processor. The POR configuration PLD does not drive all POR configuration pins, but just those that are needed for frequency selection and boot location.

# 14.2 POR Configuration Resistors

The POR settings that are not set by the POR configuration PLD are controlled via on-board resistors. For a list of POR configuration resistors, refer to page 16 of the schematic.

## 15 JTAG/COP

The JTAG connection is provided by a direct connection to the appropriate header connector.

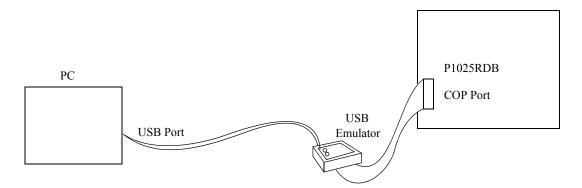

#### 15.1 COP/JTAG Port

The common on-chip processor (COP) is part of the P1025E's JTAG module and is implemented as a set of additional instructions and logic. This port can connect to a dedicated emulator for extensive system debugging. Several third-party emulators in the market can connect to the host computer through the E thernet port, USB port, parallel port, RS-232, and so on. A typical setup using a USB port emulator is shown in Figure 17.

Figure 17. Connecting P1025RDB-PA to a USB Emulator

P1025RDB-PA Specification, 2.0

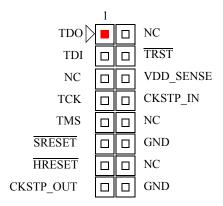

#### JTAG/COP

The 16-pin generic header connector carries the COP/JTAG signals and the additional signals for system debugging. The pinout of this connector is shown in Figure 18.

Figure 18. RDB COP Connector

Table 13 lists the connections made from the RDB COP Connector

Table 13. Connectivity from the COP Connector

|       | Pin Number  |                                                                             |  |  |  |

|-------|-------------|-----------------------------------------------------------------------------|--|--|--|

| Pin # | Signal Name | Connection                                                                  |  |  |  |

| 1     | TDO         | Connected directly between the processor and JT AG/COP connector.           |  |  |  |

| 2     | NC          | Not connected                                                               |  |  |  |

| 3     | TDI         | Connected directly between the processor and JT AG/COP connector.           |  |  |  |

| 4     | TRST        | Routed to the RESET PLD. TRST to the processor is generated from the PLD.   |  |  |  |

| 5     | NC          | Not connected                                                               |  |  |  |

| 6     | VDD_SENSE   | Pulled to 3.3V via a 10 Ohm resistor                                        |  |  |  |

| 7     | TCK         | Connected directly between the processor and JT AG/COP connector.           |  |  |  |

| 8     | CKSTP_IN    | Connected directly between the processor and JT AG/COP connector.           |  |  |  |

| 9     | TMS         | Connected directly between the processor and JT AG/COP connector.           |  |  |  |

| 10    | NC          | Not connected                                                               |  |  |  |

| 11    | SRESET      | Routed to the RESET PLD. SRESET to the processor is generated from the PLD. |  |  |  |

| 12    | GND         | Connected to ground                                                         |  |  |  |

| 13    | HRESET      | Routed to the RESET PLD. HRESET to the processor is generated from the PLD. |  |  |  |

#### P1025RDB-PA Specification, 2.0

| Pin Number |           |                                                                   |  |

|------------|-----------|-------------------------------------------------------------------|--|

| 14         | KEY       | Not connected                                                     |  |

| 15         | CKSTP_OUT | Connected directly between the processor and JT AG/COP connector. |  |

| 16         | GND       | Connected to ground                                               |  |

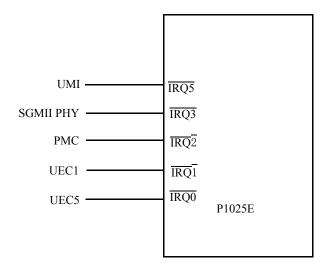

# 16 Interrupts

Figure 19 shows the external interrupts to the P1025E.

Figure 19. P1025E Interrupts

Table 14 lists how the interrupts are connected on the RDB platform.

**Table 14. Interrupts**

| Name | Connection           | Note             |

|------|----------------------|------------------|

| IRQ0 | UEC5 PHY KSZ8041     | On-board Pull-up |

| IRQ1 | UEC1 PHY KSZ8041     | On-board Pull-up |

| IRQ2 | PMC Card             | On-board Pull-up |

| IRQ3 | SGMII PHY<br>VSC8221 | On-board Pull-up |

| IRQ4 | Not used             | On-board Pull-up |

| IRQ5 | UMI(PLC)             | On-board Pull-up |

P1025RDB-PA Specification, 2.0

**Table 14. Interrupts (continued)**

| Name    | Connection | Note             |

|---------|------------|------------------|

| IRQ6    | not used   | On-board Pull-up |

| IRQ_OUT | not used   | On-board Pull-up |

## **17 DMA**

The DMA function itself is not utilized on the RDB platform. Unused input pins are pulled high. Since certain DMA pins have POR functionality, these pins are connected on the platform.

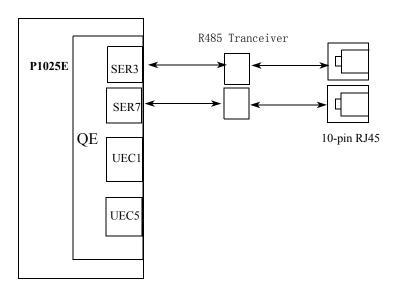

## 18 RS485

There are two full duplex RS485 interface with 10-pin RJ45 connectors. Within the QUICC Engine, UCC3 and UCC7 two universal controllers are configured as UART controllers. Besides, two transceivers on the board are used to convert UART signal to RS485 signal. Figure 20 shows how the RS485 is connected to the QE interface of P1025E device.

Figure 20. RS485 Connection

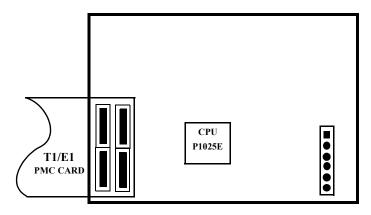

# **19 PMC**

The RDB provides QUICC Engine evaluation through 4x TDM ports. A set of PMC connectors (PMC0) have been added on the RDB boards themselves. TDM signals are terminated to PMC0. The T1/E1 card on PMC0 tests the TDMs of the QUICC Engine block. Table 15 lists QE TDM function pin map.

**Table 15. QUICC Engine Block Functions**

| Functional Pin | PQ Pin  | 4TDM Siganls |

|----------------|---------|--------------|

| LDP0           | CE_PA11 | TDMB_RXD1    |

| LDP1           | CE_PA12 | TDMB_RXD2    |

| LA28           | CE_PA13 | TDMB_RXD3    |

| LGPL5          | CE_PA14 | TDMB_TXD1    |

| GPIO11         | CE_PA15 | TDMB_TXD2    |

| LCLK1          | CE_PA16 | TDMB_TXD3    |

| LA24           | CE_PA18 | TDMD_TXD0    |

| LA25           | CE_PA19 | TDMD_RXD0    |

| LA26           | CE_PA20 | TDMD_TSYNC   |

| LA27           | CE_PA21 | TDMD_RSYNC   |

| LCS_B7         | CE_PA27 | TDMB_TXCLK   |

| CE_PB20        | CE_PB20 | TDMB_RXD[0]  |

| LA31           | CE_PA30 | TDMB_TSYNC   |

| GPIO6          | CE_PA31 | TDMB_RSYNC   |

| GPIO5          | CE_PB0  | TDMB_TXD[0]  |

| GPIO7          | CE_PB1  | TDMB_RXCLK   |

| GPIO0          | CE_PB4  | TDMC_TXD[0]  |

| GPIO4          | CE_PB5  | TDMC_RXD[0]  |

| GPIO1          | CE_PB6  | TDMC_TSYNC   |

| GPIO3          | CE_PB7  | TDMC_RSYNC   |

| LWE_B1         | CE_PB9  | TDMC_TXD1    |

| IRQ6           | CE_PB10 | TDMC_RXCLK   |

| GPIO2          | CE_PB11 | TDMC_TXCLK   |

| GPIO8          | CE_PB12 | TDMA_RXCLK   |

| GPIO9          | CE_PB13 | TDMA_TXCLK   |

| UART_CTS1#     | CE_PB14 | TDMC_RXD3    |

| UART_RTS1#     | CE_PB15 | TDMC_TXD2    |

| UART_SIN1      | CE_PB16 | TDMC_TXD3    |

| UART_SOUT1     | CE_PB17 | TDMC_RXD1    |

| CE_PB18        | CE_PB18 | TDMC_RXD2    |

| DMA2_DACK0#    | CE_PB19 | SPI1_MOSI    |

| LBCTL          | CE_PA29 | SPI1_SEL#    |

|                |         | •            |

| Functional Pin | PQ Pin  | 4TDM Siganls |

|----------------|---------|--------------|

| IIC2_SDA       | CE_PB21 | SPI1_CLK     |

| IIC2_SCL       | CE_PB22 | SPI1_MISO    |

| MSRCID0        | CE_PB23 | TDMA_TXD[0]  |

| MSRCID1        | CE_PB24 | TDMA_RXD[0]  |

| MSRCID2        | CE_PB25 | TDMA_TSYNC   |

| MSRCID3        | CE_PB26 | TDMA_RSYNC   |

| GPIO14         | CE_PB31 | TDMD_TXCLK   |

| GPIO15         | CE_PC0  | TDMD_RXCLK   |

**Table 15. QUICC Engine Block Functions**

The supported PMC card is Freescale PQ-MDS-T1. The supported SLIC module is Zarlink Le71HR8820G. Figure 21shows the connection when PMC card is inserted to P1025RDB. Refer to *P1025RDB-PA Quick Start Guide rev0.1* for details of the process to evaluate TDM function.

Figure 21. PMC Card inserted to P1025RDB-PA

# 20 Connectors, Headers, Push Buttons and LEDs

## 20.1 Headers

Table 16 lists the various headers on the RDB platform.

**Table 16. Headers**

| Reference Designators | Used for       | Note                                          |

|-----------------------|----------------|-----------------------------------------------|

| J21                   | Lattice Header | Used for programming the Lattice PLD devices. |

| J14                   | 1588           |                                               |

| J22                   | COP/JTAG       |                                               |

#### P1025RDB-PA Specification, 2.0

**Table 16. Headers**

| Reference Designators | Used for             | Note                                |

|-----------------------|----------------------|-------------------------------------|

| Ј20                   | PLC/DAC              | Jumper to select PLC or DAC of 1588 |

| J8                    | SER3 RS485           | Modem Line CD,CTS,RTS and CLK1      |

| J9                    | SER7 RS485           | Modem Line CD,CTS,RTS and CLK2      |

| J10                   | SER5 RS485           | TX and RX signal                    |

| J12                   | SER5 RS485           | Modem Line CD,CTS,RTS and CLK4      |

| J11                   | SER1 RS485           | TX and RX signal                    |

| J13                   | SER1 RS485           | Modem Line CD,CTS,RTS and CLK3      |

| J26                   | Reset remote control |                                     |

## 20.2 Connectors

Table 17 lists all the connectors on the RDB platform.

**Table 17. Connectors**

| Reference Designators | Used for         | Note                                                               |

|-----------------------|------------------|--------------------------------------------------------------------|

| J17                   | Open Frame Power |                                                                    |

| J25                   | SD/MMC Card      |                                                                    |

| U35                   | PCIe x1 cards    | Intended use is for PCIe cards that are 10W are less.              |

| P5                    | Mini-PCIe cards  |                                                                    |

| Ј6                    | Ethernet Port    | Bot port-eTSEC2 (SGMII); VSC8221<br>Top port-eTSEC3(RGMII); AR8021 |

| P1                    | Ethernet Port    | eTSEC1 (RGMII); AR8021                                             |

| J5                    | Ethernet Port    | Top -UEC1<br>Bot - UEC5                                            |

| J2                    | RS485 Ports      | SER3                                                               |

| J3                    | RS485 Ports      | SER7                                                               |

| J4                    | Dual Type A USB  |                                                                    |

| J7                    | UART             | Top-UART1<br>Bot -UART0                                            |

| BT1                   | Battery Holder   | CR-2032                                                            |

| J23                   | UMI(PLC)         |                                                                    |

| J15/J16/J18/J19       | PMC              |                                                                    |

Connectors, Headers, Push Buttons and LEDs

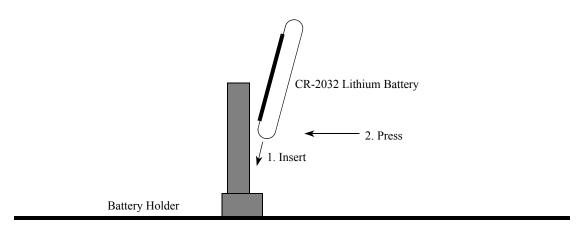

## 20.2.1 Battery Holder

The board contains an RTC that requires a battery in order to maintain the data inside the RTC. The battery holder (BT1) accommodates a CR-2032. Figure 22 shows how to insert a battery.

Figure 22. Installation of Battery

### 20.3 Push Buttons

Table 18 details how the push buttons are used on the RDB platform.

**Table 18. Push Buttons**

| Reference Designators | Used for |

|-----------------------|----------|

| SW1                   | Reset    |

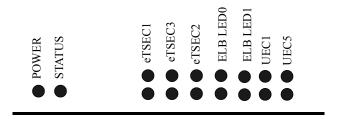

## **20.4** LEDs

Table 19 details all the LEDs on the RDB chassis.

Table 19. LEDs

| LEDs | Used for                   | Controlled by              |

|------|----------------------------|----------------------------|

| D26  | Power on                   | +3.3V rail                 |

| D27  | Status                     | Lattice PLD (U44)          |

| D19  | TOP: Link<br>BOT: Activity | eTSEC1 RGMII PHY<br>AR8021 |

| LEDs | Used for                   | Controlled by               |

|------|----------------------------|-----------------------------|

| D20  | TOP: Link<br>BOT: Activity | eTSEC3 RGMII PHY<br>AR8021  |

| D21  | TOP: Link<br>BOT: Activity | eTSEC2 SGMII PHY<br>VSC8221 |

| D22  | ELB LED0                   | CPLD                        |

| D23  | ELB LED1                   | CPLD                        |

| D24  | TOP: Link<br>BOT: Activity | UEC1 PHY KSZ8041            |

| D25  | TOP: Link<br>BOT: Activity | UEC5 PHY KSZ8041            |

Refer to *P1025RDB-PA CPLD Specification-V0.3* for details on controlling the LEDs by Lattice PLD. Figure 23 shows LEDs on the P1025RDB front side chassis.

Figure 23. LEDs on Chassis

# 21 Power Related

# 21.1 Open Frame Power Supply

Open Frame power supply PD45 supplies +12V and +5V for the RDB board. The rated power is 40W.

# 21.2 CPU\_VDD

The CPU core voltage CPU\_VDD rail is sourced from an Intersil switching regulator. The device used on the RDB is the ZL2006. CPU\_VDD=1.0V

# 21.3 AVDD Signals

All AVDD pins are sourced by the CPU\_VDD rail through the recommended filter circuit.

Power Related

### 21.4 DDR

The memory interface power rails (VTT, GVDD, and VREF) are sourced by a TI switching regulator.

The part used is the TPS51116 device. For DDR3, VTT=0.75V, GVDD=1.5V, and VREF = 0.75V.

#### 21.5 SerDes

The SerDes rails (SVDD, XVDD) are sourced from the on-board CPU VDD core voltage rail.

## 21.6 USB, SPI, eSDHC (CVDD)

Each of these rails are sourced from 3.3V rail, which is a dedicated power plane on the board. The 3.3V rail is from an MPS switching regulator MP2380.

## 21.7 Local Bus (BVDD)

This rail is sourced from 3.3V, which is a dedicated power plane on the board.

## 21.8 DUARTs, System Control, I2C, JTAG (OVDD)

This rail is sourced from 3.3V, which is a dedicated power plane on the board.

## 21.9 eTSECs (LVDD)

The LVDD rail is used for the TSEC I/Os and is configured for 2.5V operation. The rail is sourced from MPS switching regulator, part number MP2119DQ.

# 21.10 Mini-PCIe (+1.5V)

The +1.5V rail is used by the mini-PCIe slot and is sourced by an MPS switching regulator. The part used is the MP2105DJ device.

# 21.11 PCIe x1 slot (+3.3V and +12V)

The PCIe x1 slot +12V rail is directly derived from power supply. The 3.3V is sourced from MPS switching regulator MP2380.

# **21.12 Vitesse Devices (+1.2V)**

The +1.2V rail used by the Vitesse devices is sourced by an MPS Switching Regulator. The part used is the MP2365 device.

# 21.13 Micrel and Atheros Device(+3.3V)

The +3.3V rail used by the Micrel devices is sourced from MPS switching regulator MP2380.

## 21.14 Voltage Selection

The P1025E device supports multiple supply voltages on its I/O supplies. Table 20 shows the configuration of the voltage selection pins on the RDB platform.

| <b>Table 20. I/O</b> | Supply | Voltage S | Selection |

|----------------------|--------|-----------|-----------|

|----------------------|--------|-----------|-----------|

| Signal Name    | Connection               | Comment                                 |

|----------------|--------------------------|-----------------------------------------|

| LVDD_SEL       | Pulled high. LVDD = 2.5V | eTSEC1, 2, 3, Ethernet management, 1588 |

| BVDD_VSEL[0:1] | Pulled high. BVDD = 3.3V | Local Bus, GPIO[8:15]                   |

| CVDD_VSEL[0:1] | Pulled high. CVDD = 3.3V | USB, SD/MMC, SPI                        |

#### 22 1588

The 1588 signals are routed to a 1588 header on the board (J14). The 1588 clock input into the processor can be controlled over the SPI interface through a 12-bit digital-to-analog converter (U41). The output of the DAC feeds directly into a precision VCXO which in turn is used to drive the 1588 clock into the processor. The DAC and VCXO combination allows the 1588 clock to be varied as needed for testing.

#### 23 **Clocking**

The input system clock for the processor is a 66.66 MHz clock source. The DDR clock input is also driven by a 66.66 MHz clock source. All PCIe ports receive a dedicated 100 MHz clock. All Gigabit PHYs receive a dedicated 25 MHz oscillator clock UEC5 CLK for MAC and PHY is driven by a clock buffer which uses a 50MHz oscillator as clock source. UEC1 PHY receives a dedicated 25 MHz oscillator clock.

#### 24 Reset

All resets for the board are handled by the PLD (U56). Power-on reset is initiated by pressing the power switch if the board is in a chassis. Warm reset is initiated by pressing SW1 on the board. Software is also capable of initiating a warm reset by asserting the HRESET REQ line from the processor.

#### **Switch Settings** 25

The RDB has user selectable switches for evaluating different frequency and boot options for the P1025E device. Table 20 describes the available options.

#### 25.1 **P1025RDB Configuration (Switch Method)**

#### NOTE

All frequencies listed below assume that the input SYSCLK is set to 66.66 MHz for P1025RDB.

P1025RDB-PA Specification, 2.0 Freescale Semiconductor 33

**Switch Settings**

Table 21. P1025E Dure Core Configuration Options

| Switch<br>Settings<br>SW4[1:6] | Switch<br>Settings<br>SW3[2:3] | Core0 Freq<br>(MHz) | Core1 Freq<br>(MHz) | Platform<br>(MHz) | DDR Freq<br>(MHz) | Boot<br>Location | Boot<br>Hold-off           |

|--------------------------------|--------------------------------|---------------------|---------------------|-------------------|-------------------|------------------|----------------------------|

| 110000                         | 10                             | 533                 | 533                 | 267               | 667               | NOR              | Core0 boot; Core1 hold-off |

| 110001                         | 10                             | 533                 | 533                 | 267               | 667               | SD/MMC           | Core0 boot; Core1 hold-off |

| 110010                         | 10                             | 533                 | 533                 | 267               | 667               | SPI              | Core0 boot; Core1 hold-off |

| 110011                         | 10                             | 533                 | 533                 | 267               | 667               | NAND             | Core0 boot; Core1 hold-off |

| 110100                         | 10                             | 400                 | 400                 | 267               | 667               | NOR              | Core0 boot; Core1 hold-off |

| 110101                         | 10                             | 400                 | 400                 | 267               | 667               | SD/MMC           | Core0 boot; Core1 hold-off |

| 110110                         | 10                             | 400                 | 400                 | 267               | 667               | SPI              | Core0 boot; Core1 hold-off |

| 110111                         | 10                             | 400                 | 400                 | 267               | 667               | NAND             | Core0 boot; Core1 hold-off |

| Table 22. P1025E Single Core Config Options |                                |                     |                     |                   |                   |                  |                  |

|---------------------------------------------|--------------------------------|---------------------|---------------------|-------------------|-------------------|------------------|------------------|

| Switch<br>Settings<br>SW4[1:6]              | Switch<br>Settings<br>SW3[2:3] | Core0 Freq<br>(MHz) | Core1 Freq<br>(MHz) | Platform<br>(MHz) | DDR Freq<br>(MHz) | Boot<br>Location | Boot<br>Hold-off |

| 110000                                      | 01                             | 533                 | N/A                 | 267               | 667               | NOR              | Core0 boot       |

| 110001                                      | 01                             | 533                 | N/A                 | 267               | 667               | SD/MMC           | Core0 boot       |

| 110010                                      | 01                             | 533                 | N/A                 | 267               | 667               | SPI              | Core0 boot       |

| 110011                                      | 01                             | 533                 | N/A                 | 267               | 667               | NAND             | Core0 boot       |

| 110100                                      | 01                             | 400                 | N/A                 | 267               | 667               | NOR              | Core0 boot       |

| 110101                                      | 01                             | 400                 | N/A                 | 267               | 667               | SD/MMC           | Core0 boot       |

| 110110                                      | 01                             | 400                 | N/A                 | 267               | 667               | SPI              | Core0 boot       |

| 110111                                      | 01                             | 400                 | N/A                 | 267               | 667               | NAND             | Core0 boot       |

| 100000                                      | 01                             | 667                 | N/A                 | 333               | 667               | NOR              | Core0 boot       |

| 100001                                      | 01                             | 667                 | N/A                 | 333               | 667               | SD/MMC           | Core0 boot       |

| 100010                                      | 01                             | 667                 | N/A                 | 333               | 667               | SPI              | Core0 boot       |

| 100011                                      | 01                             | 667                 | N/A                 | 333               | 667               | NAND             | Core0 boot       |

Note:667MHz core frequency can only be supported at P1015/P1016 platform.SW3[2:3]=10,dual core;SW3[2:3]=01,single core

#### 25.2 Other configuration options

Table 23 describes the other configuration options available on the board.

**Table 23. Other Config Options**

| Switch | Signal Name                 | Signal Meaning                                                | Setting                                                                                                                                                        |

|--------|-----------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SW4[7] | LGPL5<br>(cfg_boot_seq[1])  | Selects whether the boot sequencer is enabled during boot-up. | OFF: boot sequencer enabled and configuration information loaded from I2C ROM. A valid ROM must be present. If not card will hang. ON: boot sequencer disabled |

| SW4[8] | FBANK_SELECT                | Selects which NOR flash bank is selected.                     | OFF: upper 4 sectors used for booting ON: middle 4 sectors used for booting                                                                                    |

| SW3[1] | CFG_SDWIDTH                 | Configs the width of the SD/MMC bus, 4-bit or 8-bit           | OFF: then width = 4bits, SPI interface active ON: then width = 8bits  Software can read the status of this bit by readin the I2C 8-bit register.               |

| SW3[2] | TEST_SEL                    | Personality Selection                                         | OFF: Single e500 Core Device (P1016)<br>ON: Dual e500 Core Device (P1025)                                                                                      |

| SW3[3] | DMA1_DACK_N                 | Freescale use only                                            | Set to OFF for P1025E<br>Set to ON for P1016E                                                                                                                  |

| SW3[4] | LA19<br>(cfg_host_agt[2])   | Controls the setting of the cfg_host_agt[2] pin               | ON: cfg_host_agt[2] = 1 OFF: cfg_host_agt[2] = 0  Refer to Section 25.4, Configuring Host/Agent Mode                                                           |

| SW3[5] | USB1_STP                    | Freescale use only                                            | Must be set to OFF for P1025E                                                                                                                                  |

| SW3[6] | SWITCH7                     | Reserved                                                      | Default ON                                                                                                                                                     |

| SW3[7] | LA18<br>cfg_host_agt[1]     | Controls the setting of the cfg_host_agt[1] pin               | ON: cfg_host_agt[1] = 1 OFF: cfg_host_agt[1] = 0  Refer to Section 25.4, Configuring Host/Agent Mode                                                           |

| SW3[8] | LWE1_N<br>(cfg_host_agt[0]) | Controls the setting of the cfg_host_agt[0] pin               | ON: cfg_host_agt[0] = 1 OFF: cfg_host_agt[0] = 0  Refer to Section 25.4, Configuring Host/Agent Mode                                                           |

# 25.3 Factory Settings of board switches

Table 24 shows default settings of all the switches on SW4 and SW3.

**Table 24. Default Settings of Board Switches**

| Switch | 1   | 2  | 3   | 4   | 5   | 6   | 7  | 8  |

|--------|-----|----|-----|-----|-----|-----|----|----|

| SW4    | ON  | ON | OFF | OFF | OFF | OFF | ON | ON |

| SW3    | OFF | ON | OFF | ON  | OFF | ON  | ON | ON |

# 25.4 Configuring Host/Agent Mode

Table 25 shows how the PCIe port can be configured in either Host or Agent mode.

P1025RDB-PA Specification, 2.0

**Switch Settings**

Table 25. Host/Agent Selection

| Device | Configuration                                                                  | cfg_host_agt[0]<br>controlled by SW3[8] | cfg_host_agt[1]<br>controlled by SW3[7] | cfg_host_agt[2]<br>controlled by SW3[4] |

|--------|--------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|

| P1025E | P1025E acts as the<br>host/root complex for<br>all PCIe interface<br>(default) | SW3[8] =ON<br>cfg_host_agt[0] = 1       | SW3[7] =ON<br>cfg_host_agt[1] = 1       | SW3[4] =ON<br>cfg_host_agt[2] = 1       |

| P1025E | P1025E acts as an host<br>on PCIe 1 and acts as an<br>agent on<br>PCIe 2       | SW3[8] =OFF<br>cfg_host_agt[0] = 0      | SW3[7] =ON<br>cfg_host_agt[1] = 1       | SW3[4] =OFF<br>cfg_host_agt[2] = 0      |

| P1025E | P1025E acts as an agent on PCIe 1 and acts as an host on PCIe 2                | SW3[8] =OFF<br>cfg_host_agt[0] = 0      | SW3[7] =OFF<br>cfg_host_agt[1] = 0      | SW3[4] =ON<br>cfg_host_agt[2] = 1       |

| P1025E | P1025E acts as an agent on all its PCI Express interfaces.                     | SW3[8] =OFF<br>cfg_host_agt[0] = 0      | SW3[7] =OFF<br>cfg_host_agt[1] = 0      | SW3[4] =OFF<br>cfg_host_agt[2] =0       |

## 25.5 Reading and Writing Certain Board Switches

An 8-bit I2C register allows software to override certain switches remotely without having to change the physical switch. In addition, the CFG\_SDWIDTH status can also be read via the I2C register. The I2C register is implemented by Philips PCA9557 device. The register definition is shown in Table 26. The mapping between the I2C register bits and the switches are shown Table 27. The I2C switch is located on I2C2 and is accessible at address 18H.

After being set, software must issue a reset command (asserting HRESET\_REQ\_B) for the new switch settings to take effect. Once the I2C registers are written and enabled, they override the board switches until either the I2C bits are disabled or a power cycle occurs.

Table 26. PCA9557 Register Definition

| Name       | Туре       | Function             |

|------------|------------|----------------------|

| Register 0 | Read       | Input port register  |

| Register1  | Read/Write | Output port register |

| Name       | Туре       | Function                                                                                                                                                                                                                                                                        |

|------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register 2 | Read/Write | Input pins polarity inversion register =1, the corresponding port pin's polarity is inverted =0, the corresponding port pin's original polarity is retained  Note that default value of this register is: Bit [7:4] = 1, polarity inverted Bit [3:0] = 0, polarity not inverted |

| Register 3 | Read/Write | Configuration register =1, the corresponding port pin is enabled as an input =0, the corresponding port pin is enabled as an output  Note that default value of this register is FF                                                                                             |

Table 27. Mapping between I2C register and POR switches

| I2C Register Bit | Comment                                             |

|------------------|-----------------------------------------------------|

| IO7              | overrides SW4[1], and thereby controls Switch1      |

| IO6              | overrides SW4[2], and thereby controls Switch2      |

| IO5              | overrides SW4[3], and thereby controls Switch3      |

| IO4              | overrides SW4[4], and thereby controls Switch4      |

| IO3              | overrides SW4[5], and thereby controls Switch5      |

| IO2              | overrides SW4[6], and thereby controls Switch6      |

| IO1              | overrides SW4[8]; and thereby controls FBANK_SELECT |

| IO0              | "read-only" of CFG_SDWIDTH switch SW3[1]            |

# 25.5.1 Uboot steps for overriding on-board switches to change frequency

- 1. First change to the correct I2C bus

- $\Rightarrow$  i2c dev 1

- Setting bus to 1

- 2. A read of the input register will return the current state of the on-board switches

- => i2c md 180

- Set you desired values for switches.

- =>  $i2c \text{ mw } 18 \ 1 \ 10$

- 3. Next, set appropriate pins as outputs.

- => i2c mw 18.3 ef

#### **Switch Settings**

=> i2c mw 18 1 10

- 4. A read will return the current over-written value that will be used for all subsequent resets.

- => i2c md 18.0

- This value will be used until either the power is turned off, until the pins from the I2C device are tri-stated

## 25.5.2 Example log file showing change of frequencies via software

U-Boot 2010.12-00063-g8669298-dirty (Jul 09 2011 - 14:37:56) CPU0: P1025E, Version: 1.1, (0x80ec0311) Core: E500, Version: 5.1, (0x80212051) Clock Configuration: CPU0:533.333 MHz, CPU1:533.333 MHz, CCB:266.667 MHz, DDR:333.333 MHz (666.667 MT/s data rate) (Asynchronous), LBC:16.667 MHz QE:266.667 MHz L1: D-cache 32 kB enabled I-cache 32 kB enabled Board: P1025RDB CPLD: V2.6 PCBA: V2.0 rom loc: nor lower bank SD/MMC: 4-bit Mode eSPI: Enabled I2C: ready SPI: ready DRAM: Detected UDIMM(s) DDR: 1 GiB (DDR3, 32-bit, CL=5, ECC off) FLASH: 16 MiB L2: 256 KB enabled NAND: 32 MiB MMC: FSL ESDHC: 0 Firmware 'Microcode version 0.0.1 for P1021 r1.0' for 1021 V1.0 QE: uploading microcode 'Microcode for P1021 r1.0' version 0.0.1 PCIe1: Root Complex of mini PCIe SLOT, no link, regs @ 0xffe0a000 PCIe1: Bus 00 - 00 PCIe2: Root Complex of PCIe SLOT, no link, regs @ 0xffe09000 PCIe2: Bus 01 - 01 Video: No radeon video card found! In: serial Out: serial Err: serial Net: eTSEC2 is in sgmii mode. eTSEC1, eTSEC2, eTSEC3 Hit any key to stop autoboot: 0 => i2c dev 1 Setting bus to 1 => i2c md 18 0

=> i2c mw 18 3 ef => i2c md 18 0

=> reset

U-Boot 2010.12-00063-g8669298-dirty (Jul 09 2011 - 14:37:56)

CPU0: P1025E, Version: 1.1, (0x80ec0311) Core: E500, Version: 5.1, (0x80212051)

Clock Configuration:

CPU0:400 MHz, CPU1:400 MHz,

CCB:266.667 MHz,

DDR:333.333 MHz (666.667 MT/s data rate) (Asynchronous), LBC:16.667 MHz

QE:266.667 MHz L1: D-cache 32 kB enabled I-cache 32 kB enabled

Board: P1025RDB CPLD: V2.6 PCBA: V2.0

rom\_loc: nor lower bank SD/MMC : 4-bit Mode eSPI : Enabled I2C: ready

SPI: ready

DRAM: Detected UDIMM(s)

DDR: 1 GiB (DDR3, 32-bit, CL=5, ECC off)

FLASH: 16 MiB L2: 256 KB enabled NAND: 32 MiB MMC: FSL ESDHC: 0

Firmware 'Microcode version 0.0.1 for P1021 r1.0' for 1021 V1.0 QE: uploading microcode 'Microcode for P1021 r1.0' version 0.0.1 PCIe1: Root Complex of mini PCIe SLOT, no link, regs @ 0xffe0a000

PCIe1: Bus 00 - 00

PCIe2: Root Complex of PCIe SLOT, no link, regs @ 0xffe09000

PCIe2: Bus 01 - 01

Video: No radeon video card found!

In: serial Out: serial Err: serial

Net: eTSEC2 is in sgmii mode. eTSEC1, eTSEC2, eTSEC3 Hit any key to stop autoboot: 0

=>

# 25.5.3 Uboot steps for overriding on-board switch to change NOR boot bank

- 1. First change to the correct I2C bus

- $\Rightarrow$  i2c dev 1

- Setting bus to 1

- 2. A read of the input register will return the current state of the on-board switches.

- => i2c md 18.0

#### **Getting Started**

The register value shows that FBANK\_SELECT on IO1 is one, thereby the switch SW4[8] is set to ON and the U-Boot is stored in the lower NOR boot bank now.

- Set you desired values for switches

- =>i2c md 1810

- 3. Next, set the IO ports as outputs.

- => i2c mw 18.3 fd

- Set the FBANK\_SELECT IO1 bit to zero, thereby selecting the upper bank upon reset.

- 4. A read will return the current over-written value that will be used for all subsequent resets.

- => i2c md 18.0

- 5. Use U-Boot command to reset the system.

- reset

- if there is no uboot in the other bank of nor flash, system will not boot up.

#### NOTE

This value will be used until either the power is turned off, or the pins from the I2C device are tri-stated

# **26** Getting Started

This section describes how to boot the P1025RDB. The on-board flash memory is preloaded with a flash image from the factory. The on-board switches and jumpers are set to the factory defaults.

#### **CAUTION**

Avoid touching areas of integrated circuitry and connectors; static discharge can damage circuits.

#### **WARNING**

Turn OFF power during insertion and removal of any PCIe card.

### **26.1** External Cable Connections

Connect the serial port of the P1025RDB system and a host computer using an RS-232 cable. Also, connect the AC cable to the backside of the chassis.

# 26.2 Serial Port Configuration (PC)

Before powering up the P1025RDB, configure the serial port of the attached computer with the following values:

Data rate: 115200 bpsNumber of data bits: 8

• Parity: None

• Number of Stop bits: 1

• Flow Control: Hardware/None

# 26.3 Power Up

Do not turn power on until all the cables are connected and the serial port is configured as described previously. Once done, power up the unit by pressing the power button on the backside of the chassis. A few seconds after power up, the U-Boot prompt should be received by the serial terminal program are illustrated in the example below:

U-Boot 2010.12-00063-g8669298-dirty (Jul 09 2011 - 14:37:56)

CPU0: P1025E, Version: 1.1, (0x80ec0311) Core: E500, Version: 5.1, (0x80212051)

Clock Configuration:

CPU0:533.333 MHz, CPU1:533.333 MHz,

CCB:266.667 MHz,

DDR:333.333 MHz (666.667 MT/s data rate) (Asynchronous), LBC:16.667 MHz

QE:266.667 MHz L1: D-cache 32 kB enabled I-cache 32 kB enabled

Board: P1025RDB CPLD: V2.6 PCBA: V2.0

rom\_loc: nor lower bank SD/MMC : 4-bit Mode eSPI : Enabled I2C: ready SPI: ready

DRAM: Detected UDIMM(s)

DDR: 1 GiB (DDR3, 32-bit, CL=5, ECC off)

FLASH: 16 MiB L2: 256 KB enabled NAND: 32 MiB MMC: FSL\_ESDHC: 0

Firmware 'Microcode version 0.0.1 for P1021 r1.0' for 1021 V1.0 QE: uploading microcode 'Microcode for P1021 r1.0' version 0.0.1 PCIe1: Root Complex of mini PCIe SLOT, no link, regs @ 0xffe0a000

PCIe1: Bus 00 - 00

PCIe2: Root Complex of PCIe SLOT, no link, regs @ 0xffe09000

PCIe2: Bus 01 - 01

#### **Getting Started**

Video: No radeon video card found!

In: serial Out: serial Err: serial

Net: eTSEC2 is in sgmii mode. eTSEC1, eTSEC2, eTSEC3 Hit any key to stop autoboot: 0

=`

# 27 Revision History

Table 28 provides a revision history for this document.

**Table 28. Document Revision History**

| Rev.<br>Number | Date   | Description                                                                                                                                                            |

|----------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.0            | 3/2011 | First draft                                                                                                                                                            |

| 0.1            | 3/2011 | UEC1 PHY address changed from 4 to 6, refer to figure10, page15 Connect LA18 to SW3, so P1024E acts as an on PCIe 1, refer to table24,page35                           |

| 2.0            | 8/2011 | PCA9555 I2C connection changed from I2C2 to I2C1,refer to figure14,page19 Added J26 in table15,refer to page27, Added Table21for single core frequency switch settings |

#### How to Reach Us:

#### Home Page:

www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc.

Technical Information Center, EL516

2100 East Elliot Road

Tempe, Arizona 85284

1-800-521-6274 or

+1-480-768-2130

www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor

Literature Distribution Center

P.O. Box 5405

Denver, Colorado 80217

1-800 441-2447 or

+1-303-675-2140

Fax: +1-303-675-2150

LDCForFreescaleSemiconductor

@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale are trademarks or registered trademarks of Freescale Semiconductor, Inc. in the U.S. and other countries. All other product or service names are the property of their respective owners. The PowerPC name is a trademark of IBM Corp. and is used under license. RapidIO is a registered trademark of the RapidIO Trade Association. IEEE 1588 is a registered trademark of the Institute of Electrical and Electronics Engineers, Inc. (IEEE). This product is not endorsed or approved by the IEEE.

© Freescale Semiconductor, Inc., 2004-2011. All rights reserved.

Document Number: P1025RDB-PA Agile # UMS-26826 2.0 08/2011