**ADS Board Specification**

MPC8560/ADS8540/D Rev. 0.5.1, 6/2004

MPC8560/MPC8540 ADS Specification

# MPC8560/MPC8540 Power QUICC III<sup>TM</sup> Integrated Communications Processor ADS Board Specification

# **Documentation History**

| Date       | Author        | Version | Comments                                                          |

|------------|---------------|---------|-------------------------------------------------------------------|

| 7/1/2002   | V. Yukht      | 1.0     | Initial Draft in Word (Chapters 1 - 10)                           |

| 7/1/2002   | H. Amir       | 1.0     | Initial Draft in Word (Chapters 11 - 13)                          |

| 10/14/2002 | D. I. Forsyth | 0.2     | Edited in Framemaker for customer release                         |

| 10/16/2003 | H. Amir       | 1.3     | Updated Version in Word                                           |

| 10/27/2003 | D.I. Forsyth  | 0.3     | Edited in Framemaker for customer release includes Pilot updates. |

| 11/10/03   | D.I. Forsyth  | 0.4     | Edited changes in tables of contents.                             |

| 2/5/04     | D.I. Forsyth  | 0.5     | Incorporate update from V. Yukht.                                 |

| 4/5/2004   | RG            | 0.5.1   | Updated Fig. 12-4, 12-5; updated text in Section 12.6             |

| 6/4/2004   | RG            | 0.6     | Updated Fig. 10-1, 11-2, Table 11-1, 12-1; added Table 11-4, 11-5 |

#### **Table of Contents**

| Topic                                                | Page |

|------------------------------------------------------|------|

| Document History                                     | 2    |

| Part I, "Introduction"                               | 5    |

| Section 1.1, "Document Objective"                    | 5    |

| Section 1.2, "The Role of ADS"                       | 5    |

| Section 1.3, "Reference Documents"                   | 5    |

| Part II, "MPC8560 and MPC8540 Features Overview"     | 6    |

| Section 2.1, "MPC8560 Block Diagram"                 | 7    |

| Section 2.2, "MPC8540 Block Diagram"                 | 8    |

| Section 2.3, "MPC8560/MPC8540 ADS Block Diagram"     | 8    |

| Section 2.4, "Reference HIP Expansion Card"          | 9    |

| Section 2.5, "Reference ADS Component Placement"     | 9    |

| Part III, "DDR SDRAM Interface"                      | 10   |

| Section 3.1, "DDR Interface Overview"                | 10   |

| Section 3.2, "Power for DDR"                         | 11   |

| Section 3.3, "Synchronization"                       | 11   |

| Section 3.4, "Serial Presence Detect (SPD) Function" | 11   |

| Section 3.5, "Debug Function"                        | 11   |

| Part IV, "RapidIO Interface"                         | 12   |

| Section 4.1, "RapidIO Interface Overview"            | 12   |

| Section 4.2, "Power for RapidIO"                     | 13   |

| Section 4.3, "Placement of RapidIO Connectors"       | 13   |

| Part V, "Power Supply"                               | 15   |

| Section 5.1, "Primary Power Supply"                  | 16   |

| Section 5.2, "ADS Power Supply Structure"            | 16   |

| Section 5.3, "Power Supply Operation"                | 17   |

| Part VI, "PCI/PCI-X Interface"                       | 20   |

| Section 6.1, "PCI/PCI-X Overview"                    | 21   |

| Section 6.2, "Auto Identification"                   | 21   |

| Section 6.3, "PCI/PCI-X Clocking"                    | 21   |

| Section 6.4, "PCI/PCI-X Reset"                       | 21   |

| Section 6.5, "Optional JTAG Connectivity"            | 21   |

| Section 6.6, "PCI/PCI-X Power"                       | 21   |

| Section 6.7, "PCI/PCI-X Interrupts"                  | 21   |

| Section 6.8, "PCI/PCI-X Control"                     | 22   |

| Section 6.9, "PCI Slot Connector Pinouts"            | 22   |

| Section 7.1, "Clocking Architecture"                                 | 25 |

|----------------------------------------------------------------------|----|

| Section 7.2, "Clock Control"                                         | 25 |

| Section 7.3, "Clock Out Parameters"                                  | 26 |

| Part VIII, "JTAG Test Access Port (TAP)"                             | 27 |

| Section 8.1, "JTAG TAP Connection"                                   | 27 |

| Part IX, "System Control and Debug Signals"                          | 30 |

| Section 9.1, "System Control"                                        | 31 |

| Section 9.2, "Reset Configuration"                                   | 31 |

| Section 9.3, "Debug Signals"                                         | 32 |

| Part X, "ADS Reset unit"                                             | 33 |

| Section 10.1, "Reset Overview"                                       | 33 |

| Section 10.2, "Power-On and Hard Reset"                              | 33 |

| Section 10.3, "Soft Reset"                                           | 33 |

| Section Part XI, "Triple Speed Ethernet Controller (TSEC) Interface" | 34 |

| Section 11.1, "TSEC Overview"                                        | 34 |

| Section 11.2, "Physical Media Interfaces"                            | 35 |

| Section 11.3, "TSEC Host Interfaces"                                 | 35 |

| Section 11.4, "Hardware Configuration"                               | 38 |

| Part XII, "CPM Interface"                                            | 40 |

| Section 12.1, "Communication Ports"                                  | 40 |

| Section 12.2, "ATM Ports"                                            | 41 |

| Section 12.3, "Mode Selection"                                       | 42 |

| Section 12.4, "Fast Ethernet (10/100 Base-T)"                        | 49 |

| Section 12.5, "Fast Ethernet Mode Selection"                         | 50 |

| Section 12.6, "RS-232 Ports"                                         | 50 |

| Section 12.7, "Expansion Connectors"                                 | 51 |

| Section 12.8, "TCOM/ECOM Add-in Board Connection"                    | 61 |

| Section 12.9, "ADS Communication Control Registers"                  | 61 |

| Section 12.10, "Debug LED's"                                         | 62 |

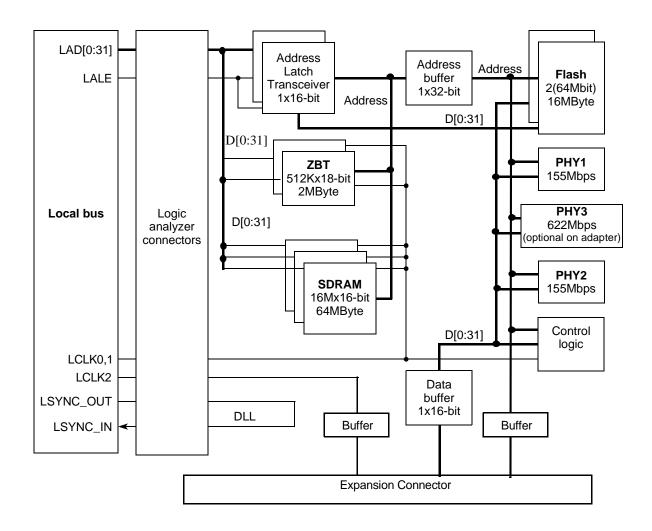

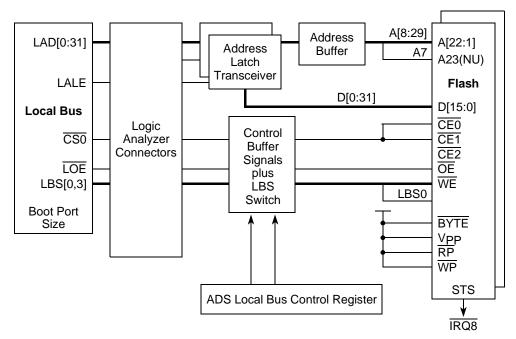

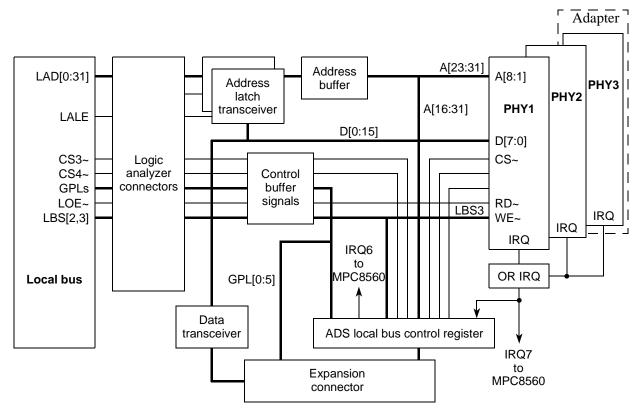

| Part XIII, "Local Bus Interface"                                     | 69 |

| Section 13.1, "Local Bus Features"                                   | 69 |

| Section 13.2, "Address Latch/ Data Transceiver"                      | 70 |

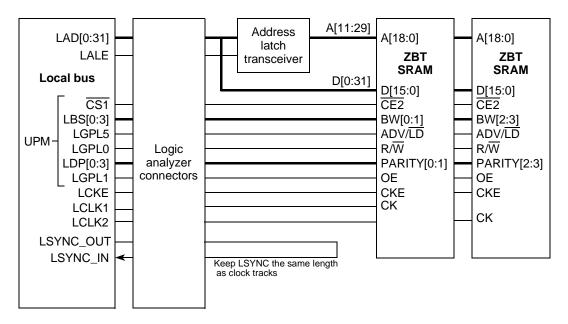

| Section 13.3, "Zero Bus Turnaround (ZBT) SRAM"                       | 70 |

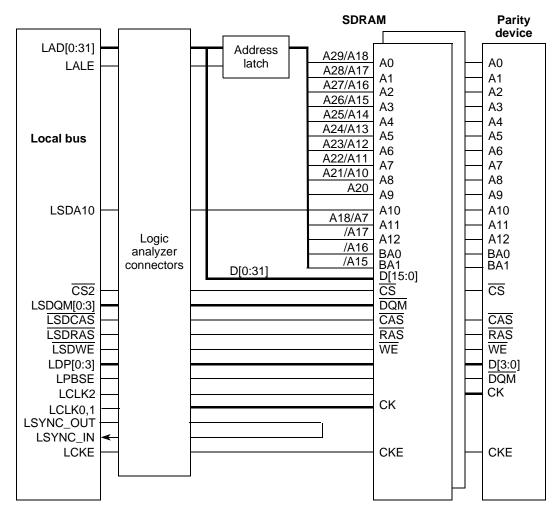

| Section 13.4, "SDRAM"                                                | 71 |

| Section 13.5, "Local Bus and Flash"                                  | 73 |

| Section 13.6, "Local Bus ATM PHYs and Control Logic"                 | 74 |

| Section 13.7, "Expansion Connector"                                  | 75 |

| Section 13.8, "MPC8560/MPC8540 Clock Driver"                         | 80 |

# Part I Introduction

# 1.1 Document Objective

This document defines a technical specification for the MPC8560/MPC8540 ADS; this development board will be used to verify the operation of the MPC8560 and MPC8540 integrated communications processors.

#### 1.2 The Role of ADS

The ADS helps to fill the void between the traditional design-focused, electrical, circuit, and logical testing and actual customer applications. While the ADS cannot practically mimic every possible customer design, it does provide exposure to issues associated with the simultaneous operation of various interfaces and protocols that are most likely to be found in specific market applications.

In addition to verifying the simultaneous operation of interfaces and protocols, the ADS provides a level of systems performance characterization that will prove useful to users.

To assist in system debugging, on board PCB compression land pattern connectors to the Tektronix TLA7Axx Series Logic Analyzer Probes P6860/P6880 are provided.

#### 1.3 Reference Documents

- MPC8560 User's Manual

- MPC8560 Hardware Specification

- MPC8540 User's Manual

- MPC8540 Hardware Specification

- Elysium specification

- 8260 User's Manual

- 8260 Web site

- 824x Web site

# Part II MPC8560 and MPC8540 Features Overview

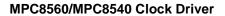

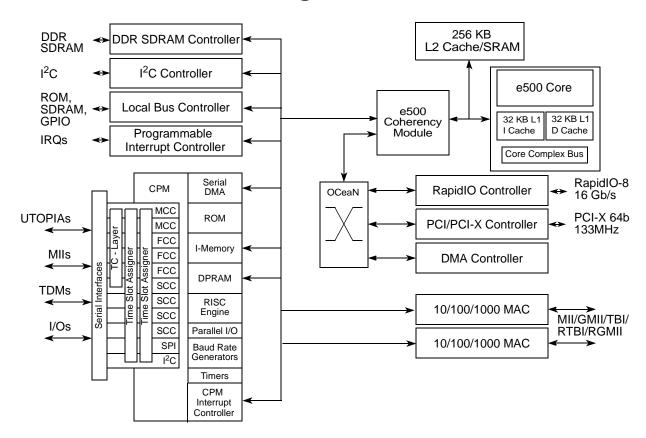

The MPC8560 PowerQUICC III<sup>TM</sup>, is the next generation integrated communications processor. The MPC8560 comprises a communications processor module (CPM) that integrates many high-speed communications interfaces and related protocols. In addition to the CPM, the MPC8560 also includes the e500 high performance embedded core processor with 256 Kbytes of level-2 cache/SRAM. Coupled with the CPM and the e500 are two triple speed Ethernet controllers (TSEC), a 64 bit PCI/PCI-X controller, a RapidIO interface, and a DDR SDRAM memory controller.

The MPC8540 processor can be viewed as a subset of the MPC8560 device. The MPC8540 processor has the same features as the MPC8560 processor except that in place of the CPM functionality, the MPC8540 has a DUART interface and a 10/100 Ethernet port for debugging.

The following list is an overview of the MPC8560/MPC8540 feature set.

#### MPC8560 and MPC8540:

- Embedded e500 Book E compatible core running at 600–800 MHz

- 32 Kbyte data and 32 Kbyte instruction L1 caches

- 256 Kbytes of on-chip memory/L2 cache

- One I<sup>2</sup>C controller

- Two TSEC (Triple-Speed Ethernet Controller) supporting 10/100/1000 Mbps, MII, GMII, RGMII, and TBI interfaces

- DDR SDRAM memory controller

- RapidIO interconnect supporting 8 bit mode, 2.5V LVDS at 500 MHz

- PCI/PCI-X controller supporting PCI 2.2 and PCI-X 1.0 specifications

- Local bus controller with 32-bit address and data at 167 MHz, three UPMs (user programmable machines), SDRAM controller, GPCM (general purpose chip select machine), and eight chip-selects

- DMA controller

- Programmable Interrupt Controller (PIC)

- Boot sequencer for I<sup>2</sup>C interface to serial ROM

- JTAG boundary scan interface

#### MPC8560-only:

- RISC CPM running up to 333 MHz (1 Gbps aggregate bandwidth)

- 32 Kbytes of dual port RAM

- 128 Kbytes of ROM and 32 Kbytes of instruction RAM

- Two Utopia Level II multi-phy, master/slave ports (one at 16 bit)

- Three MIIs (media independent interfaces)

- Eight TDM (time division multiplexed) interfaces, supporting T1/E1, T3/E3, ISDN, IDL, CEPT, GCI, PCM.

- Three FCCs (fast communications controllers) supporting up to 155 Mbps ATM, 10/100 Mbps Ethernet, 45 Mbps HDLC.

- Two MCCs (multi-channel controllers) supporting 128 serial, full-duplex 64Kbps channels

- Four SCCs (serial communications controllers) supporting HDLC, UART, BISYNC.

- One SPI (Serial Peripheral Interface)

# 2.1 MPC8560 Block Diagram

Figure 2-1. MPC8560 Block Diagram

# 2.2 MPC8540 Block Diagram

Figure 2-2. Block Diagram of the MPC8540

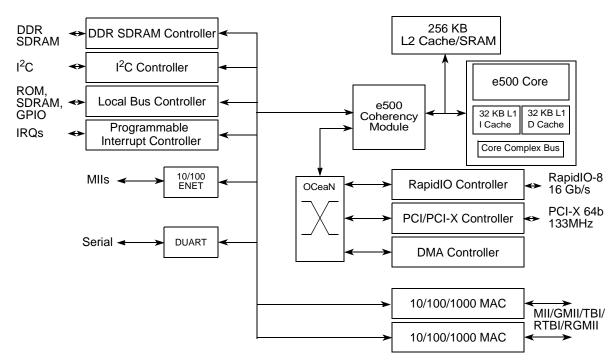

# 2.3 MPC8560/MPC8540 ADS Block Diagram

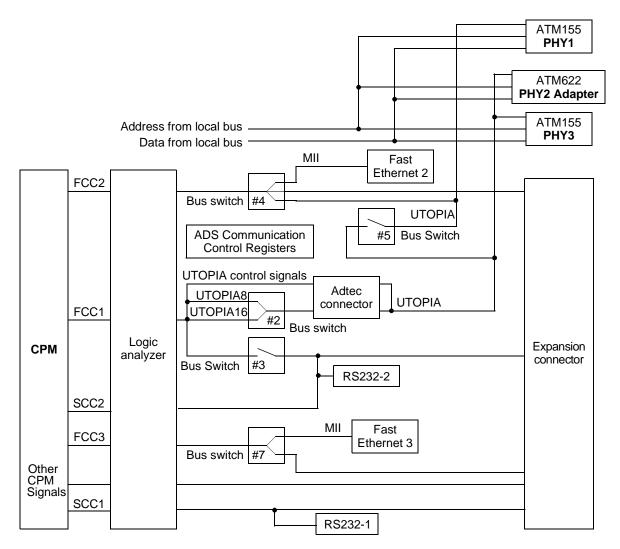

The MPC8560/MPC8540 ADS is represented in Figure 2-3.

Figure 2-3. MPC8560/MPC8540 ADS Block Diagram

Each interface module shown in the picture is described and detailed below.

# 2.4 Reference HIP Expansion Card

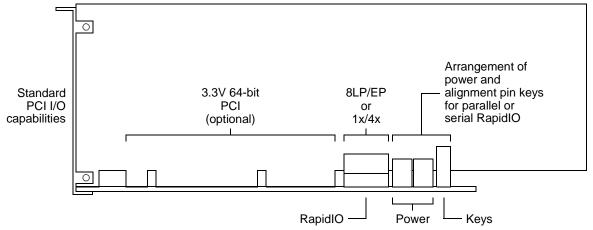

Figure 2-4. HIP Expansion Card Format

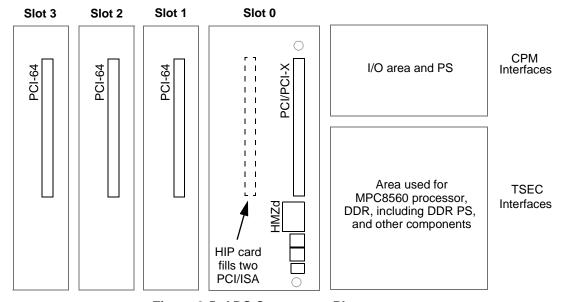

# 2.5 Reference ADS Component Placement

Figure 2-5. ADS Component Placement

# Part III DDR SDRAM Interface

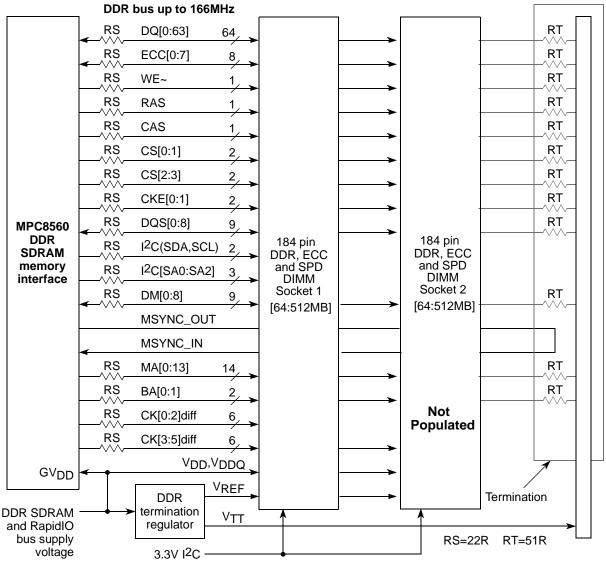

A detailed block diagram of the DDR SDRAM interface is represented in Figure 3-1.

Figure 3-1. DDR Bus

#### 3.1 DDR Interface Overview

The DDR SDRAM interface is implemented with a standard 184-pin DIMM sockets ready for operation with one unbuffered DDR DIMM module inserted into them. This interface ensures ECC and SPD functions of the DDR DIMM modules. The interface provides correct operation with DDR DIMM modules with a clock rate up to 166MHz (333MHz—PC2100 DDR data rate). In order to guarantee this performance, an appropriate layout should be used.

#### 3.2 Power for DDR

Each DDR socket (DIMM module) and MPC8560 devices are powered by appropriate VCC and reference voltages from the separated power supply (See Section 5.2, "ADS Power Supply Structure"). A corresponding termination voltage is also provided. Each interface line is terminated through the recommended resistor Rt = 51 Ohms. Optional serial termination resistors, Rs = 22 Ohms, are also provided. Serial presence detect (SPD) Serial  $I^2C$  EEPROM mounted in the DDR DIMM are powered from the system 3.3V power source.

# 3.3 Synchronization

To ensure correct timing of the bus, the MSYNC\_IN and MSYNC\_OUT pins of the MPC8560 device are connected to each other through a special conductor to provide the same propagation delay to all other interface signals.

# 3.4 Serial Presence Detect (SPD) Function

The serial presence detect (SPD) function is implemented by connecting the DIMM  $I^2C$  signals to the CPM  $I^2C$  interface of the device or (optionally) to the host PC through the appropriate parallel port.

The ADS is equipped with one unbuffered 128MByte PC2100 ECC SPD DIMM such as the MT5VDDT1672AG-335C3 from Micron Co.

# 3.5 Debug Function

The optional debug function on the DDR SDRAM interface is provided by connecting ECC[0-4] signals from MPC8560/MPC8540 device to the corresponding on-board logic analyzer connector through an auxiliary switch. In this mode DDR SDRAM should operate without ECC functionality.

# Part IV RapidIO Interface

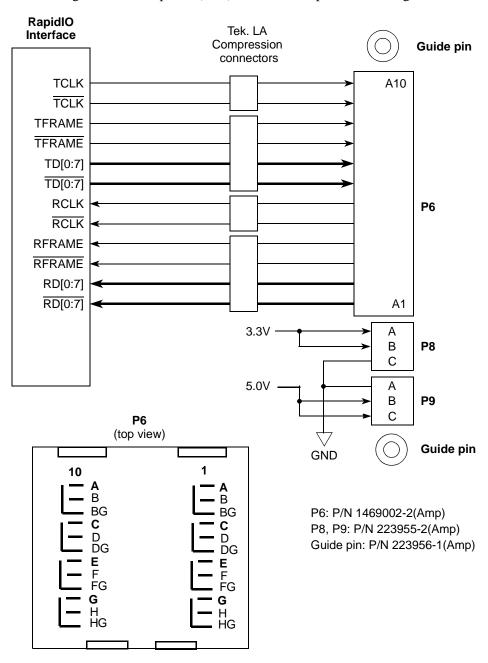

# 4.1 RapidIO Interface Overview

The RapidIO interface is implemented as a dual unidirectional 8-bit parallel bus connecting corresponding MPC8560 device pins with the recommended HMZd RapidIO connector from AMP Co.

A detailed block diagram of the RapidIO (RIO) interface is represented in Figure 4-1.

Figure 4-1. RapidIO Interface

# 4.2 Power for RapidIO

The RapidIO bus power is supplied through a pair of recommended connectors from AMP Co. All RapidIO interface lines link up to logic analyzer probe heads with a compatible footprint to provide correct signal measuring up to 500MHz.

# 4.3 Placement of RapidIO Connectors

RapidIO connectors are placed with PCI/PCI-X slot #0 to provide recommended HIP card insertion as shown in Figure 4-2 and Figure 2-5.

The JN2 connector pin assignments are defined in Table 4-1.

**Table 4-1. RapidIO Connector Assignments**

| Col | Α      | В      | BG   | С    | D    | DG   | E    | F    | FG   | G      | Н      | HG   |

|-----|--------|--------|------|------|------|------|------|------|------|--------|--------|------|

| 1   | TD0    | TD0    |      |      |      |      |      |      |      | RFRAME | RFRAME |      |

| 2   | TD1    | TD1    |      |      |      |      |      |      |      | RD7    | RD7    |      |

| 3   | TD2    | TD2    |      |      |      |      |      |      |      | TD6    | RD6    |      |

| 4   | TD3    | TD3    |      |      |      |      |      |      |      | TD5    | RD5    |      |

| 5   | TCLK0  | TCLK0  | GND  | Not  | Not  | GND  | Not  | Not  | GND  | TD4    | RD4    | GND  |

| 6   | TD4    | TD4    | GIND | Used | Used | GIND | Used | Used | GIND | RCLK0  | RCLK0  | GIND |

| 7   | TD5    | TD5    |      |      |      |      |      |      |      | RD3    | RD3    |      |

| 8   | TD6    | TD6    |      |      |      |      |      |      |      | RD2    | RD2    |      |

| 9   | TD7    | TD7    |      |      |      |      |      |      |      | RD1    | RD1    |      |

| 10  | TFRAME | TFRAME |      |      |      |      |      |      |      | RD0    | RD0    |      |

A HIP card dummy connection with mounted RapidIO and PCI/PCI-X connectors is shown in Figure 4-2.

#### Placement of RapidIO Connectors

Figure 4-2. HIP Mechanical Sample

# **Part V Power Supply**

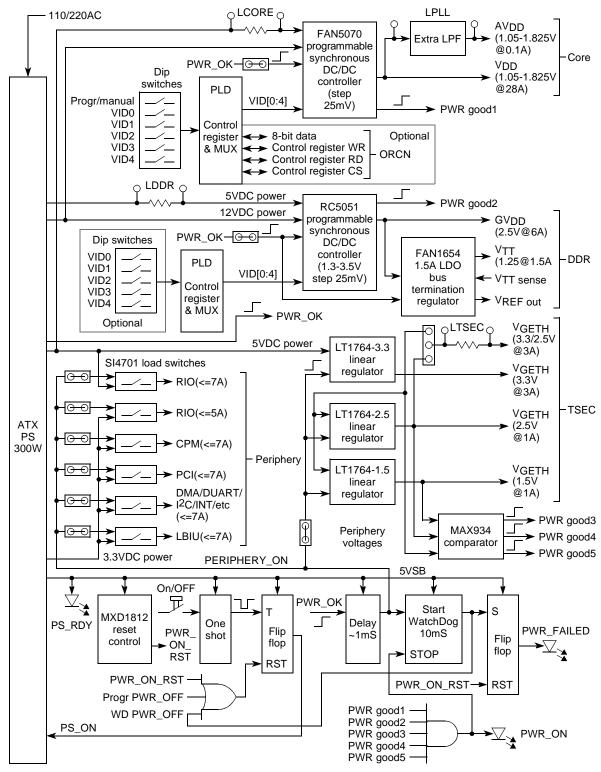

A detailed block diagram of the power supply distribution is shown in Figure 5-1.

Figure 5-1. Power Supply Block Diagram

The ADS power supply provides all necessary voltages for correct operation of the MPC8560 device and all on-board periphery.

# 5.1 Primary Power Supply

A standard CE/UL-approved PC ATX 400W power supply is used as the primary power supply. The ATX power supply produces all power required by the MPC8560 device and other ADS components through the following parameters:

- Vin = 90-265V AC

- Nin freq. = 47-63 Hz

- Iin < 7A

- Combined Power 220W max

- 3.3V DCout±5% @ 0.3–28A

- 5V DCout±5% @ 30A

- 12V DCout±5% @ 15A

- -12V DCout±10% @ 0.8A

- -5V DC @±10% @ 0.3A

- 5V DCsb±5% @ 0.72A

# 5.2 ADS Power Supply Structure

The ADS power supply consists of the following:

- Programmable synchronous DC/DC converter

- Based on FAN5070 controller from Fairchild Co. to produce MPC8560 device core/PLL voltages

- (V<sub>DD</sub> 1.05-1.825V with step 25mV, Rated Voltage 1.2V, Iout <=28A)

- Programmable synchronous DC/DC converter

- Based on RC5051 controller from Fairchild Co. to produce DDR SDRAM voltages

- $(GV_{DD} 1.3-3.5V)$  with step 25mV, Rated Voltage 2.5V, Iout <=6A)

- LDO regulator (FAN1654 Fairchild Co.)

- Produces DDR bus required termination and reference voltages

- (V<sub>TT</sub>, = 1.25V @ 1.5A, V<sub>REF</sub> = 1.25V)

- Set linear regulators (LT1764-3.3, LT1764-2.5, LT1764-1.5 from Linear Tech.)

- Provides all necessary TSEC PHY's and corresponding MPC8560 device voltages

- (3.3V DC @3A, 2.5V DC @1A, 1.5V DC @1A)

- Multi-channel voltage comparator (MAX934 from Dallas-Maxim Co.)

- Determines power good status of the TSEC supply voltages

- Set power load switches

- Realizes 5V and 3.3V on/off function on the ADS.

- (Si4701 from Vishay Co. Icomm <= 7A)

- Control circuits

- Provides necessary power on/off, visual indication, and power sequence functions.

# 5.3 Power Supply Operation

#### 5.3.1 Power-On

The ATX power supply provides 5VSB (5V Standby) voltage immediately after connection to an AC power outlet. This voltage powers the control circuits of the on-board power supply as follows:

- After the 5VSB appears, the auxiliary reset controller (MXD1812 from Dallas-Maxim Co.) produces a reset signal to reset the Power-On/Off flip-flop and the Power Failed flip-flop. The yellow LED "PS Ready" indicates the ready status of the PS to operate. No other voltages are present on the board.

- When the operator pushes the "On/Off" button, the Power-On/Off flip-flop sends PS\_ON signal to the ATX PS. The ATX PS produces all above-mentioned voltages and after finishing all transients, produces the PWR OK signal to inform the ADS that all output voltages are in good condition.

- The PWR\_OK signal is driven to the core and DDR DC/DC converters and the delay line.

- Core and DDR voltages are produced with the same profile after about 1mS and the delay line output Periphery\_ON signal, switches on the TSEC regulators (Ton<10uS) and load switches (Ton<50uS) to supply voltages to all other on-board periphery such as RapidIO, PCI etc.

- Concurrently the WatchDog circuits start (T~10mS) to monitor the power-on condition.

- In case of no failure, the Power Good signals from each supply stop the WatchDog and illuminate the green "PWR\_ON" LED. Otherwise, the WatchDog sets the Power Failed flip-flop indicated by illumination of the red "PWR\_Failed" LED, and resets the Power On/Off flip-flop. In effect, this cancels the PS\_ON signal to the ATX PS so the ATX PS is switched off. In this case, recurring switching on is only possible after reconnection of the ATX PS to the AC outlet.

#### 5.3.2 Power Off

• If the ADS is in Power-On status ("PWR\_ON" LED is illuminated) and the operator pushes the On/Off button, the Power-On/Off flip-flop cancels the PS\_ON signal to the ATX power supply (i.e. switches it off).

# 5.3.3 Over-Current, Voltage, and Temperature Protection

Each of the regulators used in the on-board power supply (along with the ATX power supply) have embedded over-current, voltage, and temperature protection. Power load switches are protected with fast over current protection circuits.

#### 5.3.4 Current Measurement

The ability to measure the amount of current consumed by each module (for example, the core, the DDR block, etc.) is provided by measuring the voltage drop on the fixed series resistors in the corresponding circuits.

### 5.3.5 Auxiliary Function

To provide the capability for various device testing and analysis, there are options to switch off Core and/or DDR on board voltages by disconnecting hard-wired control jumpers in the corresponding circuit.

#### 5.3.6 Voltage Regulation

#### 5.3.6.1 Core and PLL voltages

There are two ways to adjust  $V_{DD}$  and  $AV_{DD}$  voltages (simultaneously) within the stated-above limits:

- Manually, by setting corresponding DIP switches (Progr./Manual switch in Manual position)

- Remotely, by the Optional Remote Control Network (ORCN) through the Host PC parallel port interface (Progr./Manual switch in Progr. position).

After power-on, these voltages are set to default values.

#### 5.3.6.2 DDR Voltages

The DDR SDRAM  $GV_{DD}$  and termination  $(V_{TT})$  and reference  $(V_{REF})$  voltages can be adjusted automatically within the limits stated previously by manually setting corresponding DIP switches to desired values. Note that the  $V_{OUT}$  of the RC5051 goes to the  $GV_{DD}$  of the DDR SDRAM.

After power-on, these voltages are set to default values.

#### 5.3.6.3 TSEC Voltages

The voltage for the MPC8560 device TSEC interface pins can be switched to 3.3V or 2.5V, selected with a jumper.

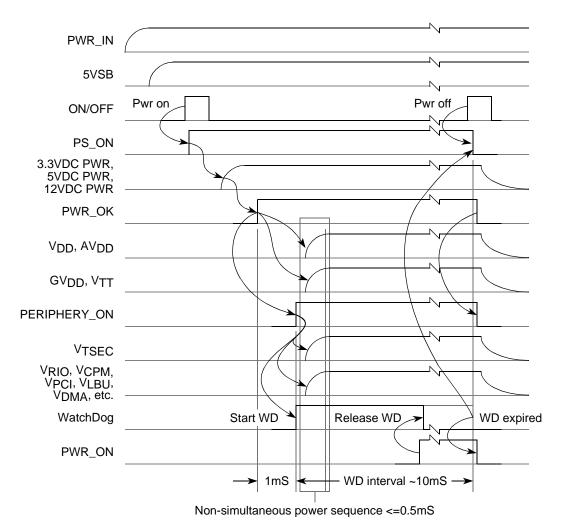

#### 5.3.6.4 Power Sequence

Figure 5-2 summarizes the power sequence of the power supply.

Figure 5-2. Power Supply Sequence

# Part VI PCI/PCI-X Interface

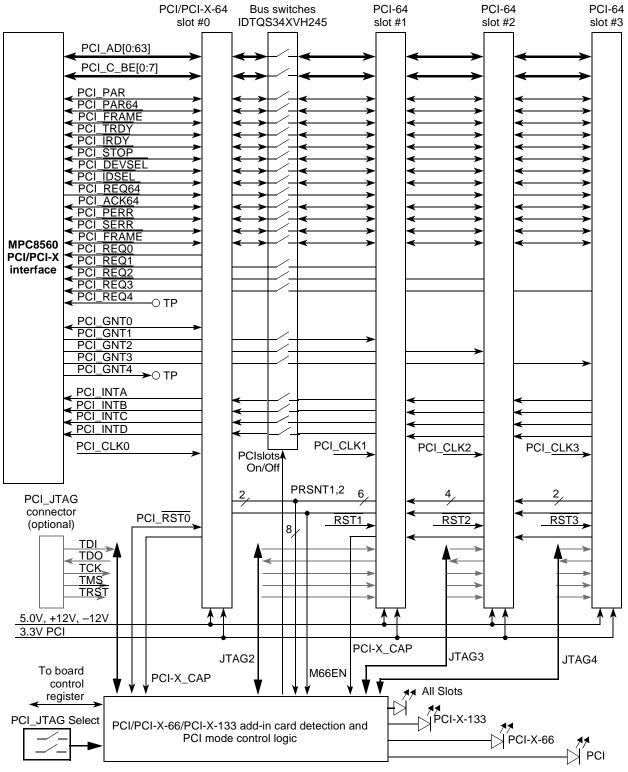

Figure 6-1 represents a detailed PCI/PCI-X interface block diagram.

Figure 6-1. PCI/PCI-X Interface Block Diagram

#### 6.1 PCI/PCI-X Overview

The combined PCI/PCI-X interface provides a standard interface to the MPC8560 device for PCI32/64 add-in cards operating at up to 66 MHz as well as PCI-X32/64 add-in cards operating at up to 133 MHz.

As shown in the block diagram, the interface consists of four standard 1.27 mm 184-pin 3V edge card connectors (for example the 891779230 from Molex).

The nearest slot to the MPC8560 device (slot #0) is specified to operate in PCI/PCI-X modes while slots #1–3 are for PCI cards only.

Bus switches, IDTQS34XVH245; 32 bit, Tpd = 250ps, Ron = 4R, from IDT Co. causes the PCI slots to be disconnected from the bus in the case where the a PCI-X card is inserted into slot #0. This guarantees optimal parameters of transmission on the high-frequency bus.

#### 6.2 Auto Identification

Static auto identification mechanism provides recognition of the type of card inserted into a slot (conventional PCI, PCI-X 66 MHz or PCI-X 133 MHz). Therefore, the bus switches mentioned above should be turned either on or off. A three-level comparator are used for this detection. The signals to be analyzed are PCIX\_CAP from slot #0 and PCIX\_CAP signals from slots #1–3. The signal from slot #0 has the highest priority, so if a PCI-X card is inserted into slot #0, the conventional PCI slots #1–3 will be disconnected from the bus.

# 6.3 PCI/PCI-X Clocking

Each slot is clocked with individual clock signals from the system clock distribution buffer, as recommended by the PCI/PCI-X standard, to provide the same clock timing parameters.

### 6.4 PCI/PCI-X Reset

Each slot receives a common PCI\_Reset signal as recommended by the PCI/PCI-X standard.

# 6.5 Optional JTAG Connectivity

All PCI/PCI-X slots are connected to the optional JTAG connector, as specified in the standard, to provide appropriate add-in card service (if required).

# 6.6 PCI/PCI-X Power

All PCI/PCI-X slots are powered with appropriate voltages from the on-board power supply as specified by the PCI/PCI-X standard.

# 6.7 PCI/PCI-X Interrupts

The PCI/PCI-X interrupt signals are connected to the suitable MPC8560 device EPIC inputs in compliance with a standard provided order.

The PCI/PCI-X interrupt routing is represented in Table 6-1.

Table 6-1. PCI/PCI-X Interrupts

| MPC8560 | PCI/PCI-X Slot #0 |          |          | PCI Slot #1 |          |          | PCI Slot #2 |          |          |          | PCI Slot #3 |          |          |          |          |          |

|---------|-------------------|----------|----------|-------------|----------|----------|-------------|----------|----------|----------|-------------|----------|----------|----------|----------|----------|

| INT#    | Int<br>A          | Int<br>B | Int<br>C | Int<br>D    | Int<br>A | Int<br>B | Int<br>C    | Int<br>D | Int<br>A | Int<br>B | Int<br>C    | Int<br>D | Int<br>A | Int<br>B | Int<br>C | Int<br>D |

| 1       | *                 |          |          |             |          |          |             | *        |          |          | *           |          |          | *        |          |          |

| 2       |                   | *        |          |             | *        |          |             |          |          |          |             | *        |          |          | *        |          |

| 3       |                   |          | *        |             |          | *        |             |          | *        |          |             |          |          |          |          | *        |

| 4       |                   |          |          | *           |          |          | *           |          |          | *        |             |          | *        |          |          |          |

Note: \* - means "connection"

#### 6.8 PCI/PCI-X Control

To facilitate and simplify operation with the PCI/PCI-X interface, additional control logic provides visual inserted add-in card type indication and read/write capability (status) of the inserted add-in cards through the Board Control Register (Local Bus mapped) as follows:

- Identification of the inserted add-in card is reflected with two PCIXCAP signals (4 bits—Input)

- Power Management Enable (PME) signal (1 bit—I/O)

- 66 MHz Enable M66EN signal (1 bit—Input)

- Present—Prsnt1, 2 signals (8 bit—Input)

- Bus switches (connection Slots#1-3 to the PCI bus) status—On/Off (1 bit—I/O)

A bit map of the corresponding control register is shown in Table 6-2.

Table 6-2. PCI/PCI-X Control Register Map

| MSB          |   | Bit Numbers |   |                                       |   |   |   |                                |   |    |                                           |    | LSB    |    |    |

|--------------|---|-------------|---|---------------------------------------|---|---|---|--------------------------------|---|----|-------------------------------------------|----|--------|----|----|

| 0            | 1 | 2           | 3 | 4                                     | 5 | 6 | 7 | 8                              | 9 | 10 | 11                                        | 12 | 13     | 14 | 15 |

| Slot<br>PCIX |   | Slots       |   | , , , , , , , , , , , , , , , , , , , |   |   |   | Slot#2, Slot#3,<br>Prsnt Prsnt |   |    | Slot#3, M66 Bus NU Prsnt EN switch On/Off |    |        | NU | NU |

|              |   |             |   | 1                                     | 2 | 1 | 2 | 1                              | 2 | 1  | 2                                         |    | On/Off |    |    |

See Part XIII, "Local Bus Interface", for detailed descriptions of the corresponding Board Control Register bits.

#### 6.9 PCI Slot Connector Pinouts

The PCI/PCI-X 64bit connector pinout for 3.3V system environment is shown in Table 6-3.

Table 6-3. PCI/PCI-X Connector Pinout

| PIN | Side B     | Side A     | Comments | PIN | Side B     | Side A     | Comments      |

|-----|------------|------------|----------|-----|------------|------------|---------------|

| 1   | -12V       | TRST       |          | 49  | M66EN (PU) | AD9        |               |

| 2   | TCK        | +12V       |          | 50  | GND        | GND        |               |

| 3   | GND        | TMS        |          | 51  | GND        | GND        |               |

| 4   | TDO        | TDI        |          | 52  | AD8        | C_BE0      |               |

| 5   | +5V        | +5V        |          | 53  | AD7        | +3.3V      |               |

| 6   | +5V        | ĪNT A      |          | 54  | +3.3V      | AD6        |               |

| 7   | INT B      | INT C      |          | 55  | AD5        | AD4        |               |

| 8   | INT D      | +5V        |          | 56  | AD3        | GND        |               |

| 9   | PRSNT1     | Reserved   |          | 57  | GND        | AD2        |               |

| 10  | Reserved   | +3.3V(I/O) |          | 58  | AD1        | AD0        |               |

| 11  | PRSNT2     | Reserved   |          | 59  | +3.3V(I/O) | +3.3V(I/O) |               |

| 12  | Conn       | ector key  | 3.3V Key | 60  | ACK64      | REQ64      |               |

| 13  |            |            |          | 61  | +5V        | +5V        |               |

| 14  | Reserved   | 3.3V Aux   |          | 62  | +5V        | +5V        |               |

| 15  | GND        | RST-       |          |     | Connecto   | or key     | 64-Bit Spacer |

| 16  | CLK        | +3.3V(I/O) |          |     |            |            |               |

| 17  | GND        | GNT        |          | 63  | Reserved   | GND        |               |

| 18  | REQ        | GND        |          | 64  | GND        | C_BE7      |               |

| 19  | +3.3V(I/O) | PME- (PU)  |          | 65  | C_BE6      | C_BE5      |               |

| 20  | AD31       | AD30       |          | 66  | C_BE4      | +3.3V(I/O) |               |

| 21  | AD29       | +3.3V      |          | 67  | GND        | PAR64      |               |

| 22  | GND        | AD28       |          | 68  | AD63       | AD62       |               |

| 23  | AD27       | AD26       |          | 69  | AD61       | GND        |               |

| 24  | AD25       | GND        |          | 70  | +3.3V(I/O) | AD60       |               |

| 25  | +3.3V      | AD24       |          | 71  | AD59       | AD58       |               |

| 26  | C_BE3      | IDSEL      |          | 72  | AD57       | GND        |               |

| 27  | AD23       | +3.3V      |          | 73  | GND        | AD56       |               |

| 28  | GND        | AD22       |          | 74  | AD55       | AD54       |               |

| 29  | AD21       | AD20       |          | 75  | AD53       | +3.3V(I/O) |               |

| 30  | AD19       | GND        |          | 76  | GND        | AD52       |               |

| 31  | +3.3V      | AD18       |          | 77  | AD51       | AD50       |               |

| 32  | AD17       | AD16       |          | 78  | AD49       | GND        |               |

| 33  | C_BE2      | +3.3V      |          | 79  | +3.3V(I/O) | AD48       |               |

| 34  | GND        | FRAME      |          | 80  | AD47       | AD46       |               |

| 35  | ĪRDY       | GND        |          | 81  | AD45       | GND        |               |

#### **POLISION Connector Pinouts**

Table 6-3. PCI/PCI-X Connector Pinout (continued)

| PIN | Side B  | Side A      | Comments | PIN | Side B     | Side A     | Comments |

|-----|---------|-------------|----------|-----|------------|------------|----------|

| 36  | +3.3V   | TRDY        |          | 82  | GND        | AD44       |          |

| 37  | DEVSEL  | GND         |          | 83  | AD43       | AD42       |          |

| 38  | PCIXCAP | STOP        |          | 84  | AD41       | +3.3V(I/O) |          |

| 39  | LOCK    | +3.3V       |          | 85  | GND        | AD40       |          |

| 40  | PERR    | SMBCLK (PU) | Not used | 86  | AD39       | AD38       |          |

| 41  | +3.3V   | SMBDAT (PU) | Not used | 87  | AD37       | GND        |          |

| 42  | SERR    | GND         |          | 88  | +3.3V(I/O) | AD36       |          |

| 43  | +3.3V   | PAR         |          | 89  | AD35       | AD34       |          |

| 44  | C_BE1   | AD15        |          | 90  | AD33       | GND        |          |

| 45  | AD14    | +3.3V       |          | 91  | GND        | AD32       |          |

| 46  | GND     | AD13        |          | 92  | Reserved   | Reserved   |          |

| 47  | AD12    | AD11        |          | 93  | Reserved   | GND        | Not used |

| 48  | AD10    | Gnd         |          | 94  | GND        | Reserved   |          |

# Part VII Clocking

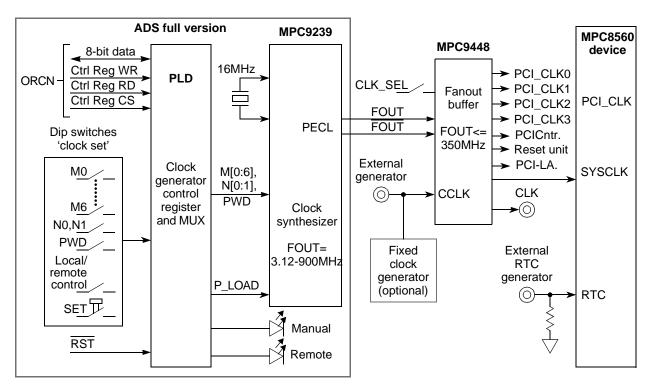

Figure 7-1 shows a detailed block diagram of the ADS clocking system.

Figure 7-1. ADS Clocking System Block Diagram

# 7.1 Clocking Architecture

The clocking system must supply the required clock signals to the MPC8560 device and PCI/PCI-X add-in cards.

To provide flexibility, the MPC9239 clock synthesizer device from Motorola is used. It supplies the ADS with clock signals in the 3.125–900MHz range. The output clock from the synthesizer (differential PECL) comes to the MPC9448 fanout buffer from Motorola, which converts it to CMOS, and distributes it to the MPC8560 device itself and to each PCI/PCI-X slot individually. Note the Fanout buffer has a maximum frequency of 350MHz. It is possible to use an external clock generator instead, if the CLK SEL switch is set to the appropriate position ("1"). To measure the clock, the clock signal test point should be used. A separate external generator connector should be used to drive the RTC auxiliary input of the MPC8560 device.

#### 7.2 Clock Control

The clock synthesizer has the capacity to program its output through an 10-bit parallel interface. The ADS provides this function by either setting the DIP switches to the desired value or optionally, through the Optional Remote Control Network (ORCN) [Part VIII of this document].

The default clock output value is defined by the DIP switches.

#### 7.3 Clock Out Parameters

Clock synthesizer produces the clock signals with a period jitter  $\leq \pm 25$  pS as follows:

| Output Frequency Range, MHz | Frequency Step, MHz |

|-----------------------------|---------------------|

| 3.125-56.25                 | <1                  |

| 50–112.5                    | 2.0                 |

| 100–225                     | 4.0                 |

| 200–450                     | 8.0                 |

The clock fan-out buffer supplies the clock signal to the MPC8560 device with following parameters:

- Output clock frequency range 0–350 MHz

- Clock skew  $\leq 150 \text{ pS}$

- Each output drives one 50 Ohm parallel terminated transmission line or alternatively, a 50 Ohm series terminated transmission line

- Output rise/fall time 0.1–1 nS

# Part VIII JTAG Test Access Port (TAP)

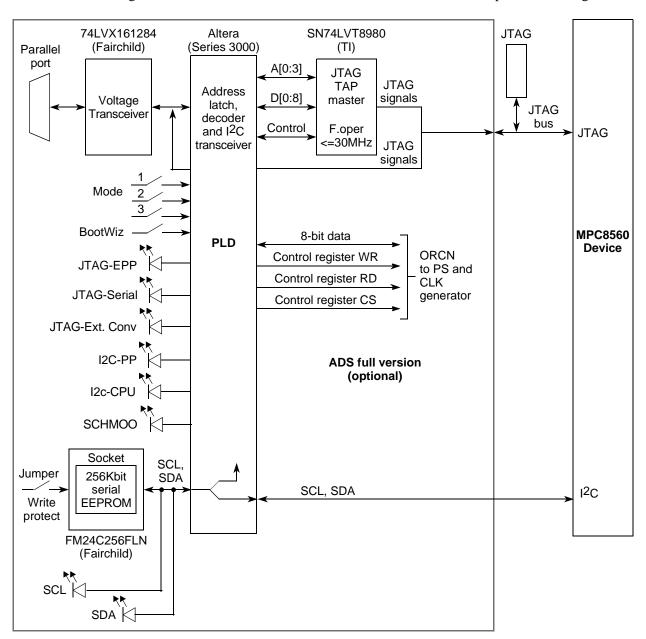

#### Including Connection, Optional Remote Control Network (ORCN), and I<sup>2</sup>C Boot EEPROM

A detailed block diagram of the ADS JTAG connection, ORCN, and I<sup>2</sup>C Boot is represented in Figure 8-1.

Figure 8-1. DC JTAG TAP, ORCN and I<sup>2</sup>C Boot Block Diagram

# 8.1 JTAG TAP Connection

The MPC8560 device JTAG connection capability is provide in the following two ways:

• Direct connection to the appropriate header connector

• Optional Host PC Parallel Port connection

#### 8.1.1 JTAG Header

The JTAG header provides connection between the MPC8560 device and any external compatible JTAG converter such as a Wiggler or probes for example, AMC WireTAP.

The JTAG dual-in-row header pin-out is represented in Table 8-1.

**Table 8-1. JTAG Header Pinout**

|     | Pin Number                             |     |           |                |                                        |     |                |     |    |           |    |           |     |                 |     |

|-----|----------------------------------------|-----|-----------|----------------|----------------------------------------|-----|----------------|-----|----|-----------|----|-----------|-----|-----------------|-----|

| 1   | 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 |     |           |                |                                        |     |                |     |    |           |    |           |     |                 |     |

| TDO | Not<br>used                            | TDI | TRST<br># | PU-10k<br>0Vdd | VDD_<br>SENSE<br>connected<br>to 3V3DC | TCK | CHKSTP<br>_IN# | TMS | NC | SRST<br># | NC | HRST<br># | Key | CHKSTP<br>_OUT# | GND |

#### 8.1.2 Parallel Port Connection

The optional JTAG parallel port connection can provide two alternative functions:

- 1. The on-board JTAG converter (substitutes the external converter)— needs no host program adaptation; it operates as if external JTAG converter is connected to the Host PC Parallel Port

- 2. Fast download mode. In this mode, the JTAG connection between the MPC8560 device and the host PC operates with the on-board JTAG TAP Master Controller (SN74LVT8980 from TI), to exchange data through the Host PC Parallel Port. Extra logic such as address latches, decoders, etc., is implemented in a PLD from Altera. This option loads data to the MPC8560 device approximately 10 times faster than with the conventional JTAG converter (TCK up to 30 MHz). However, this option requires adaptation of the Host PC drivers. HOST MODE switch block possible position represented in the following table:

**Table 8-2. Host Mode Switch Options**

| HOS | T MODE Swit | ch |                                         |

|-----|-------------|----|-----------------------------------------|

| 0   | 1           | 2  | MODE                                    |

| 0   | 0           | 0  | I2C-EPP                                 |

| 1   | 0           | 0  | JTAG-PP (Serial)                        |

| 0   | 1           | 0  | JTAG-External Converter                 |

| 1   | 1           | 0  | JTAG-EPP (Parallel)                     |

| 0   | 0           | 1  | SHMOO (JTAG-Ext. Converter, Control-EPP |

| Х   | X           | 1  | Reserved                                |

6 LEDs indicate the current JTAG mode connection:

- JTAG-EPP Parallel mode (Green)

- JTAG-Serial mode (Red)

- JTAG External Converter (Yellow)

#### **JTAG TAP Connection**

- I2C-PP (Programming serial Boot ROM through Host Parallel Port) (Red)

- I2C-CPU (Normal mode serial Boot ROM connected to the CPU) (Green)

- SHMOO (JTAG-External Converter, System Clock and Core voltage control through ORCN)

#### 8.1.3 ORCN

The optional remote control network (ORCN) is used for the following functions:

- MPC8560 core/PLL voltage program remote control

- System clock synthesizer program remote control

To implement this control, an appropriate Host PC application program and drivers must be developed. On the ADS, necessary hardware that constitutes the address decoder, set registers, etc. is developed in the same PLD.

# 8.1.4 I<sup>2</sup>C Boot EEPROM

- The MPC8560 device needs to be booted from external ROM through the serial I<sup>2</sup>C interface. As recommended, a serial EEPROM FM24C256FLN from Fairchild Co. is used. This standard 256 Kbit device is organized as 32K x 8. It has write protection capability of its memory map. This part fits into the socket to provide its reprogramming capability to an external programmer.

- Visual status of the SCL and SDA lines is provided with corresponding Red and Green LED's.

- Optional connection to the Host PC through the same PLD provides the capability to reprogram the on-board boot EEPROM.

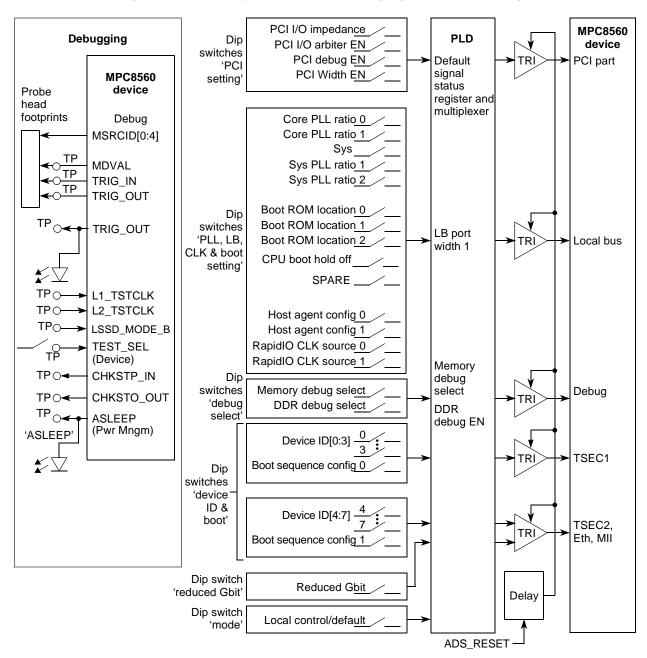

# Part IX System Control and Debug Signals

A detailed block diagram of the ADS system control and debug signals is shown in Figure 9-1.

Figure 9-1. ADS System Control and Debug Signals Block Diagram

# 9.1 System Control

The MPC8560 device must be configured at power-on. During this time, the system parameters of the various interfaces such as PCI configuration, PLL setting, etc. must be defined. Therefore, the MPC8560 device reads the status of the corresponding reset configuration pins during reset.

# 9.2 Reset Configuration

Each reset configuration pin of the MPC8560 device must be connected to a corresponding TRI-state buffer, supplying the appropriate setting during ADS\_RESET (after a short delay) as well as to the basic periphery. Each signal has the capacity to be set by a corresponding DIP switch (CONFIG switch in MANUAL position) or to be sampled by default values from a pre-programmed PLD register (CONFIG switch in Default position). Default configuration signals set are currently not implemented.

The alternative Mode setting functions of the MPC8560 device pins are shown in Table 9-1 through Table 9-5.

Table 9-1. PCI, Ethernet, and Debug Blocks

PCI Fth MI

| Main                    |                  |               | PCI         | Eth MI          | Del         | bug             |                        |                     |

|-------------------------|------------------|---------------|-------------|-----------------|-------------|-----------------|------------------------|---------------------|

| Function                | GNT_B1           | GNT_B2        | GNT_B3      | GNT_B4          | REQ_64B     | EC_MDC          | MSRCID0                | MSRCID1             |

| Reset Config<br>Setting | I/O<br>Impedance | Arbiter<br>En | Debug<br>En | PCIX<br>Capable | PCI64<br>En | Reduced<br>Gbit | Memory<br>Debug Select | DDR<br>Debug Select |

Table 9-2. TSEC1 Block

| Main                    | TSEC1      |            |            |            |                           |               |  |  |  |

|-------------------------|------------|------------|------------|------------|---------------------------|---------------|--|--|--|

| Function                | TXD4       | TXD5       | TXD6       | TXD7       | LGPL3 (Local Bus)         | GTX_CLK       |  |  |  |

| Reset Config<br>Setting | Device ID3 | Device ID2 | Device ID1 | Device ID0 | Boot sequence<br>Config 0 | Configuration |  |  |  |

Table 9-3. TSEC2 Block

| Main function           | TSEC2         |               |               |               |                           |               |  |  |

|-------------------------|---------------|---------------|---------------|---------------|---------------------------|---------------|--|--|

| Main ranotion           | TXD4          | TXD5          | TXD6          | TXD7          | LGPL5 (Local Bus)         | GTX_CLK       |  |  |

| Reset Config<br>Setting | Device<br>ID7 | Device<br>ID6 | Device<br>ID5 | Device<br>ID4 | Boot sequence<br>Config 1 | Configuration |  |  |

Table 9-4. Local Bus Part 1

| Main                    | LB                        |        |        |                        |        |                     |  |  |

|-------------------------|---------------------------|--------|--------|------------------------|--------|---------------------|--|--|

| Function                | LA27                      | LCS_B0 | LCS_B1 | LCS_B2                 | LCS_B3 | LCSB4               |  |  |

| Reset Config<br>Setting | CPU Boot<br>Configuration |        |        | Boot ROM<br>Location 2 |        | LB Hold<br>Enable 1 |  |  |

Table 9-5. Local Bus Part 2

| Main                       | LB                             |        |        |                 |                        |      |                |                |                     |  |

|----------------------------|--------------------------------|--------|--------|-----------------|------------------------|------|----------------|----------------|---------------------|--|

| Function                   | LWE_B0                         | LWE_B1 | LWE_B2 | LWE_B3          | LBCTL                  | LALE | LGPL0          | LGPL1          | LGPL2               |  |

| Reset<br>Config<br>Setting | PCI Hold<br>Configuration<br>0 |        | •      | Host Agent<br>1 | Reserved<br>(Not used) |      | RIO<br>clock 0 | RIO<br>clock 1 | Core PLL<br>ratio 1 |  |

# 9.3 Debug Signals

To provide various ADS testing, dedicated pins of the MPC8560 device are connected to appropriate logic analyzer on-board connector(s). Suitable test points are defined as shown in Figure 9-1.

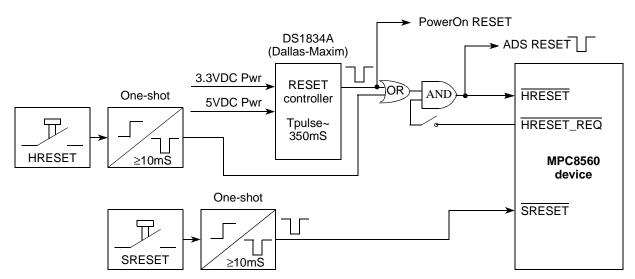

# Part X ADS Reset unit

A detailed block diagram of the ADS reset unit is shown in Figure 10-1.

Figure 10-1. ADS Reset Unit Block Diagram

#### 10.1 Reset Overview

The ADS reset unit resets the MPC8560 device itself as well as all periphery on-board components that require reset. The reset unit provides power-on, hard-reset and soft-reset signals in compliance with the MPC8560 hardware specification.

# 10.2 Power-On and Hard Reset

After the 5V DC and 3.3V DC input voltages are both stable, the DS1834A Dallas Semiconductor-Maxim reset controller drives its  $3.3V \overline{RST}$  and  $5V \overline{RST}$  output signals low for approximately 350ms. Since the system clock is running at 100KHz and the internal counter will wait 16,384 clock cycles to allow the PLL to lock. The HRESET push button also provides manual reset control.

The HRESET push button starts a one-shot circuit with a debounce flip-flop, which produces a pulse to the reset controller.

The output of the reset controller is AND'd with the HRESET\_REQ output of the MPC8560 and routed to the HRESET MPC8560 input. It provides a reset 'start' from Power-On or the HRESET push button and 'stops' it when the MPC8560 is ready to operate (auto canceling).

The soft reset signal is asserted at the same time as hard reset.

#### 10.3 Soft Reset

The soft reset unit implements a one-shot circuit with a debounce flip-flop, which produce a pulse to the  $\overline{\text{SRESET}}$  input of the MPC8560. Tsrst  $\geq$  10mS, which is enough even if the system clock is 100kHz. (Tsrst should be keep asserted for at least 1,024 clks).

# Part XI Triple Speed Ethernet Controller (TSEC) Interface

#### 11.1 TSEC Overview

Two Ethernet IEEE 802.3 ports with (10/100/1000-Base-TX) interface are provided on the ADS. Both of the two ports have the ability (optionally) to connect to a fiber optic interface. Each one of the ports is able to work with MII for 10/100-BaseT or GMII and TBI for 1000Base-T.

The 88E1011S transceiver device from Marvell is used for each of the MPC8560 10/100/1000 Ethernet ports. The device configuration modes will be controlled via MDC MDIO signals.

The 88E1011S reset input is driven by the same HRESET signal which drives the MPC8560. This resets the transceiver whenever a hard-reset sequence is taken. The 88E1011S may also be reset by asserting the appropriate Reset G-Eth bit in the on-board Control Register (TSEC1 Register 2[0], TSEC2 Register 2[1]) Or by writing a one to bit 15 (MSB) of the 88E10011S control register (register 0), via the MDC and MDIO (MII management) signals, which causes the PHY state machines to be reset. When the reset operation is done, this bit is cleared to zero automatically. The reset occurs immediately.

The GMII pins pass through the logic analyzer connector to the 88E1011S PHY and a GMII connector. This connector is defined later.

The 88E1011S is controlled via the MII management port, which is a two-wire interface consisting of a clock (MDC) and a bi-directional data line (MDIO). This is in fact a bus, where up to 32 devices may reside over it. This protocol defines a five-bit slave address field, which is compared against the slave address set to each device by hardware during device reset, including the status of the appropriate five 88E1011S pins. On the ADS, the slave addresses are hard-wired to b00000 for TSEC1 and b00001 for TSEC2. The MPC8560 MDC MDIO pins are used also for the two 10/100Base-T, CPM and maintenance port.

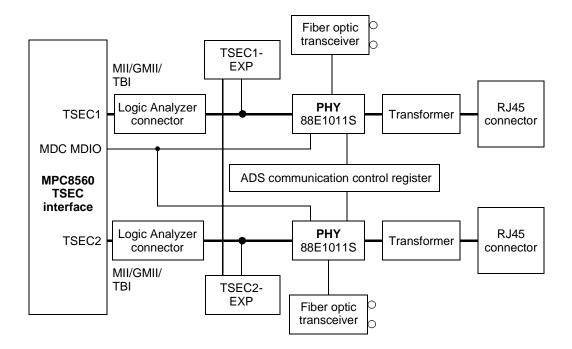

The ADS TSEC interface is shown in Figure 11-1.

Figure 11-1. TSEC Block Diagram

The following shows the MAC interfaces between the MPC8560 and the 88E1011S.

# 11.2 Physical Media Interfaces

# 11.2.1 Copper Interface

The copper interface uses the 88E1011S MDI[3:0] +/- PHY pins that connects to the physical media for 1000Base-T, 100Base-T and 10Base-T modes of operation. These pins are connected through the transformer to the UTP5 RJ45 connector.

#### 11.2.2 Fiber

The fiber cable connects to the fiber optic transceiver. The fiber optic transceiver is connected via the serial interface pins to the PHY device. The PHY device is then connected to the MPC8560 through the MII, GMII, and TBI interfaces.

#### 11.3 TSEC Host Interfaces

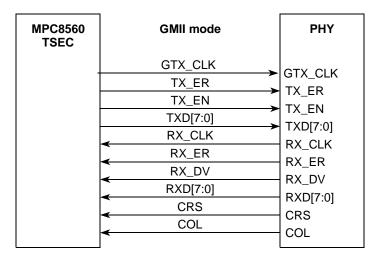

## 11.3.1 Gigabit Media Independent Interface (GMII/MII)

Table 11-1 indicates the signal mapping of the 88E1011S device to GMII/MII interface. The MII supports 100Base-T and 10Base-T modes by sharing pins of the GMII interface. This interface supports GMII to

#### **ISEC Host Interfaces**

copper connections in all three speeds. The GMII-to-copper interface is selected by setting the 88E1011 HWCFG\_MODE [3:0] to 0b1111. MDC MDIO will select the interface connection between MII, GMII and TBI.

In 1000Base-T mode, the GMII interface is selected. A 125Mhz is supplied by one of the 88E1011 to the MPC8540/60 from this clock the MPC8540/60 drives the 125Mhz clock to the second PHY's GTX\_CLK pin. The T/RXDATA are 8 bits. In 100Base-T and 10Base-T modes, the selected interface is MII; in this mode the TX\_CLK is supplied by the PHY. In MII the T/RXDATA are 4 bits.

| GMII / MII PHY and Connector Pins |          |          |           |  |  |  |  |

|-----------------------------------|----------|----------|-----------|--|--|--|--|

| GMII/MII Signal Name              | GMII     | MII      | Connector |  |  |  |  |

| GTX_CLK                           | GTX_CLK  | _        | GTX_CLK   |  |  |  |  |

| TX_CLK                            | _        | TX_CLK   | TX_CLK    |  |  |  |  |

| TX_ER                             | TX_ER    | TX_ER    | TX_ER     |  |  |  |  |

| TX_EN                             | TX_EN    | TX_EN    | TX_EN     |  |  |  |  |

| TXD[7:0]                          | TXD[7:0] | TXD[3:0] | TXD[7:0]  |  |  |  |  |

| RX_CLK                            | RX_CLK   | RX_CLK   | RX_CLK    |  |  |  |  |

| RX_ER                             | RX_ER    | RX_ER    | RX_ER     |  |  |  |  |

| RX_DV                             | RX_DV    | RX_DV    | RX_DV     |  |  |  |  |

| RXD[7:0]                          | RXD[7:0] | RXD[3:0] | RXD[7:0]  |  |  |  |  |

| CRS                               | CRS      | CRS      | CRS       |  |  |  |  |

| COL                               | COL      | COL      | COL       |  |  |  |  |

Table 11-1. Signal Mapping

The GMII signal interconnections are represented in Figure 11-2.

Figure 11-2. GMII Interconnections

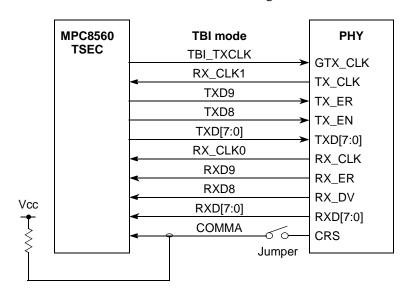

# 11.3.2 Ten Bit Interface (TBI)

The TBI interface pin mapping is shown in Table 11-2. The TBI interface supports only 1000Base-T mode of operation. The TBI-to-copper interface is selected by software through the MDC and MDIO pins.

| Table | 11-2. | TBI: | Signals |

|-------|-------|------|---------|

|-------|-------|------|---------|

| TBI Signal Names |                 |  |  |

|------------------|-----------------|--|--|

| TBI Signal Name  | PHY Signal Name |  |  |

| TBI_TXCLK        | GTX_CLK         |  |  |

| RXCLK1           | TX_CLK          |  |  |

| TXD9             | TX_ER           |  |  |

| TXD8             | TX_EN           |  |  |

| TXD[7:0]         | TXD[7:0]        |  |  |

| RX_CLK0          | RX_CLK          |  |  |

| RXD9             | RX_ER           |  |  |

| RXD8             | RX_DV           |  |  |

| RXD[7:0]         | RXD[7:0]        |  |  |

| COMMA (see note) | CRS             |  |  |

Note: This pin should be connected to PU if used in TBI, in the PMC8540/60 side. In the ADS there is a jumper that is unconnected in TBI MODE, by unconnecting it, it is automatically connected to VCC by PU.

For TSEC1 it is J50

For TSEC2 it is J51.

As shown in Figure 11-3 below, the TBI uses the same GMII signals.

Figure 11-3. TBI Signal Diagram

### **11.3.3** Summary

Table 11-3 shows the MPC8560 device TSEC pins used for each of the above-mentioned interface modes.

Table 11-3. TSEC Pin Use

| MAC Interface Pins |           |           |                     |  |

|--------------------|-----------|-----------|---------------------|--|

| TSEC Pin Name      | GMII      | MII       | ТВІ                 |  |

| GT_CLK             | GT_CLK    | _         | TBI_TXCLK           |  |

| TX_CLK             | _         | TX_CLK    | RCLK1               |  |

| TX_ER              | TX_ER     | TX_ER     | TXD9                |  |

| TX_EN              | TX_EN     | TX_EN     | TXD8                |  |

| TXD [7:0]          | TXD [7:0] | TXD [3:0] | TXD [7:0]           |  |

| RX_CLK             | RX_CLK    | RX_CLK    | RXCLK0              |  |

| RX_ER              | RX_ER     | RX_ER     | RXD9                |  |

| RX_DV              | RX_DV     | RX_DV     | RXD8                |  |

| RXD [7:0]          | RXD [7:0] | RXD [3:0] | RXD [7:0]           |  |

| CRS                | CRS       | CRS       | COMMA<br>(see note) |  |

| COL                | COL       | COL       | _                   |  |

Note: In TBI remove the jumper. J50 for TSEC1 J51 for TSEC2

# 11.4 Hardware Configuration

Configuration options like physical address, PHY operation mode, Auto-Negotiation, MDI crossover (ENA\_XC) and physical connection type are configured by the CONFIG [6:0] pins.

For G-Ethernet the TSEC PHYs get PHY addresses 0b00000 (TSEC1), and 0b00001 (TSEC2).

Note that the two 10/100Base-T already have the 0b00010, 0b00011 and (for the MPC8540 maintenance port) 0b00011 (the same as for FCC3 Ethernet) addresses.

The default configurations of the TSEC1 PHY through J56 is shown in Table 11-4

Table 11-4. TSEC1 PHY Default Configuration

| J56 Pin | Signal Name | Connected to<br>J56 Pin | J56 Pin | Signal Name  | Connected to<br>J56 Pin |

|---------|-------------|-------------------------|---------|--------------|-------------------------|

| 1       | TSEC1_CFG0  | 16                      | 2       | 3V3          | 9,11                    |

| 3       | TSEC1_CFG1  | 16                      | 4       | LED_TX       | n/a                     |

| 5       | TSEC1_CFG2  | 6                       | 6       | LED_LINK10   | 5                       |

| 7       | TSEC1_CFG3  | 10                      | 8       | LED_LINK1000 | n/a                     |

| 9       | TSEC1_CFG4  | 2                       | 10      | LED_RX       | 7                       |

| 11      | TSEC1_CFG5  | 2                       | 12      | LED_DPLX     | n/a                     |

| 13      | TSEC1_CFG6  | 16                      | 14      | LED_LINK100  | n/a                     |

| 15      | NC          | n/a                     | 16      | GND          | 1,3,13                  |

#### **Hardware Configuration**

The default configurations of the TSEC2 PHY through J47 is shown in Table 11-5

#### Table 11-5. TSEC2 PHY Default Configuration

| J47 Pin | Signal Name | Connected to<br>J47 Pin | J47 Pin | Signal Name  | Connected to<br>J47 Pin |

|---------|-------------|-------------------------|---------|--------------|-------------------------|

| 1       | TSEC1_CFG0  | 4                       | 2       | 3V3          | 5,9,11                  |

| 3       | TSEC1_CFG1  | 13,16                   | 4       | LED_TX       | 1                       |

| 5       | TSEC1_CFG2  | 2,9,11                  | 6       | LED_LINK10   | n/a                     |

| 7       | TSEC1_CFG3  | 10                      | 8       | LED_LINK1000 | n/a                     |

| 9       | TSEC1_CFG4  | 2,5,11                  | 10      | LED_RX       | 7                       |

| 11      | TSEC1_CFG5  | 2,5,9                   | 12      | LED_DPLX     | n/a                     |

| 13      | TSEC1_CFG6  | 3,16                    | 14      | LED_LINK100  | n/a                     |

| 15      | NC          | n/a                     | 16      | GND          | 3,13                    |

All the other options except the PHY address can change after reset using the MDC and MDIO signals.

The following are the PHY-selected modes of operation:

- PHY address as mention above

- Media Interface copper

- Auto Negotiation, advertise all capability force Master for TESEC1 and prefer Master for TSEC2

- Full duplex

- Enable Crossover

- Enable 125CL

- GMII to copper

- Disable fiber/ copper auto selection

- Select MDC and MDIO interface

- Interrupt polarity is active low

- Termination resistance default to 50 ohm impedance for fiber

### 11.4.1 Mode Indication LEDs

Each TSEC PHY has 6 pins targeted for mode indication LEDs as follows:

- LINK10Base-T

- LINK100Base-T

- LINK1000Base-T

- DUPLEX

- RXD

- TXD

Each one of the LEDs can be turned on, off, or blinked by writing an appropriate bit into register 25, which is the Manual LED override register of the corresponding PHY e.g. Marvell 88E1011S.

### 11.4.2 Fiber Optic and Magnetic

The transformer used is the PE5007 from Pulse Engineering. The transformer is connected to the RJ45 connector. The RJ45 connectors uses its 8 pins in 1000Base-T mode.

For the fiber optic interface, the HP HFBR-5710L device is used. The fiber optic transceiver is connected directly to the gigabit Ethernet PHY.

Note that the fiber optic interface is not the default mode.

### 11.4.3 TSEC PHY Powering

The PHY devices require three power supplies: 3.3V DC, 2.5V DC, and 1.5V DC. Three corresponding regulators on the board provide common power sources for both TSEC PHY#1 and PHY#2 (see Part V, "Power Supply").

# Part XII CPM Interface

### 12.1 Communication Ports

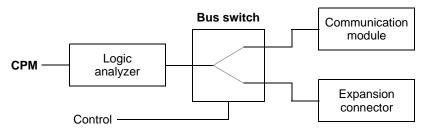

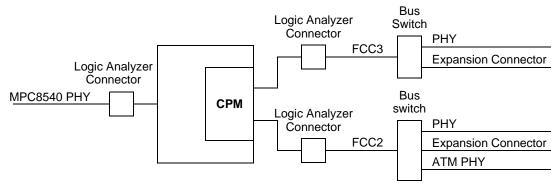

The ADS includes several communication ports to allow convenient CPM evaluation. Obviously, it is not possible to provide all types of communication interfaces supported by the CPM, but the ADS provides a convenient connection to communication interface devices for the MPC8560 via the CPM expansion connectors. These connectors reside at the edge of the board. In order to prevent long layout traces between the CPM pins and their connection to the expansion connector, each CPM pin used on the board is automatically disconnected from the expansion connector. All the CPM pins are connected to the logic analyzer connectors. Figure 12-1 below shows the CPM pins connected through the logic analyzer connector to the communication module and the expansion connector via the bus switch.

Figure 12-1. CPM Connection

The communication port interfaces provided on the ADS are listed below:

- FCC1 ATM 155 MHz 16/8 bits Single or Multi-PHY/or an optional 622 MHz with 16 bits Single PHY. ATM622 is via an adapter board it should be connected to the board for ATM622 uses.

- FCC2 ATM 155 MHz with Utopia 8 bits or Ethernet 10/100Base-T.

- FCC3 Ethernet 10/100Base-T, used also as a MPC8540 F-Ethernet maintenance port.

Two RS-232 ports residing on SCC1 and SCC2. SCC2 is also for MPC8540 internal DUART.

### 12.2 ATM Ports

To support the CPM ATM controller, there are two ATM ports on this board: two 155Mbps and connectors for the 622Mbps add-in card. The 155Mbps ATM port can work either through Utopia 16 or 8 bits, and in Multi or Single PHY Mode. The 622Mbps can operate Utopia 16 bit Single PHY Mode from the adapter.

PHY1 at 155Mbps ATM with Utopia interface is switched between FCC1 and FCC2. When it operates through FCC1, it joins onto the Utopia Bus to PHY2 and PHY3 (622 Mbps and 155 Mbps).

PHY2 & PHY1 can be connected together for multiphy operation by SW4[4] or control register 0 [3] and operate through FCC1 or FCC2. In this case, the Utopia bus connected from FCC2 is only 8 bits, or 8/16 bits when it is connected through FCC1. In any case, 622 Mbps is operating with Utopia 16 bits.

The 155 Mbps PHYs that are used are the PM5384 from PMC-SIERRA and the 622 Mbps PHY is the PM5357 also from PMC -SIERRA. The physical interface for the ATM is optical, and from OCP, part number TRP-03B. for the 622 Mbps and the HFBR-5805 for the 155 Mbps from Agilent are used. Two 40-pin connectors are used to fit the Adtech Utopia Pods. The connectors are connected as slaves. There are several bus-switches to select between FCC1, FCC2, FCC3, SCC1 and SCC2 modes as follows:

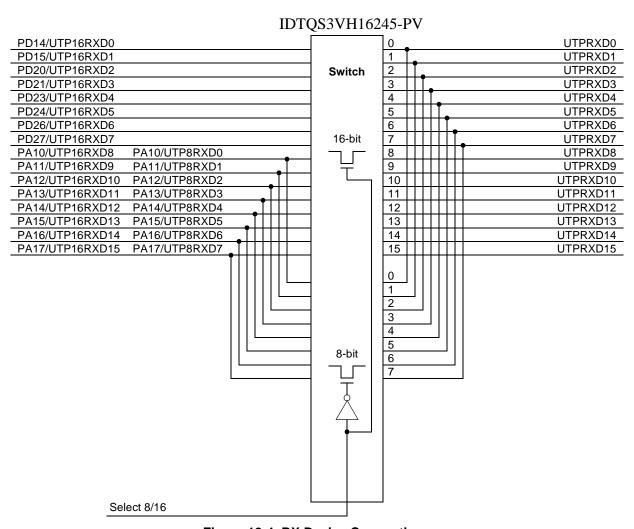

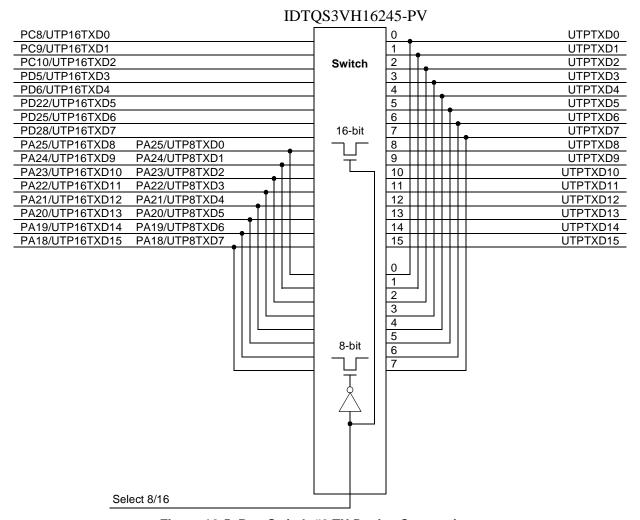

- Switch-2—Utopia 16 or 8 data bus (FCC1)

- Switch-3—FCC1 connect or disconnect to RS232 and expansion connector

- Switch-4—select FCC2 to Fast Ethernet 2 or PHY 1.

- Switch-5—PHY1 join to PHY2 and PHY3 (FCC1)

- Switch-7—select fast Ethernet 3 from CPM to the PHY or to the expansion connector. In MPC8540 mode it is automatically connected to Fast Ethernet which is connected to FCC3.

There are seven control registers called the ADS Communication Control Register 0-6 and jumpers that select the destination for FCC1 and/or FCC2 and/or FCC3 connections.

Note: One jumper defines if the configuration will be through the programmable registers or by the external switches.

The ATM PHY devices are controlled via the local bus (GPCM). The PHYs have address and data signals that are connected through buffers. One chip select ( $\overline{CS3}$  and Addresses 20, 21, 22) signal with address decoding selects one of the three ATM PHYs.

The three ATM PHYs receive their reset through reset bits [4:6] on the ADS Communication Control Register #2 or from Hard Reset.

Also the three IRQ signals are connected together to the MPC8560 IRQ7 signal.

Figure 12-2 shows the CPM module block diagram. Note this is a representation of the logic and there are some other switches detailed in Table 12-1 which are not detailed in the diagram.

Figure 12-2. CPM Connection Block Diagram

### 12.3 Mode Selection

The following tables and figures show each one of the bus switches represented in Figure 12-2. The inputs of each one have CPM names and the outputs are the function names. Again please note that Figure 12-2 is only a representation of the following signals. Specifically there are some switches in this table not detailed in the Figure 12-2.

| pin name | Function Name           | Switch # | Additional function |

|----------|-------------------------|----------|---------------------|

| PA10     | FCC1: RxD[0] UTOPIA 8 / | 2 + 5 +3 |                     |

| PA10     | FCC1: RxD[8] UTOPIA 16  | 2 +3     |                     |

| PA11     | FCC1: RxD[1] UTOPIA 8 / | 2 + 5 +3 |                     |

| PA11     | FCC1: RxD[9] UTOPIA 16  | 2 +3     |                     |

Table 12-1.

| pin name | Function Name                | Switch # | Additional function   |

|----------|------------------------------|----------|-----------------------|

| PA12     | FCC1: RxD[10] UTOPIA 16      | 2+3      |                       |

| PA12     | FCC1: RxD[2] UTOPIA 8 /      | 2 + 5 +3 |                       |

| PA13     | FCC1: RxD[11] UTOPIA 16      | 2+3      |                       |

| PA13     | FCC1: RxD[3] UTOPIA 8 /      | 2 + 5 +3 |                       |

| PA14     | FCC1: RxD[12] UTOPIA 16 /    | 2+3      |                       |

| PA14     | FCC1: RxD[4] UTOPIA 8 /      | 2 + 5 +3 |                       |

| PA15     | FCC1: RxD[13] UTOPIA 16 /    | 2+3      |                       |

| PA15     | FCC1: RxD[5] UTOPIA 8 /      | 2 + 5 +3 |                       |

| PA16     | FCC1: RxD[14] UTOPIA 16 /    | 2+3      |                       |

| PA16     | FCC1: RxD[6] UTOPIA 8 /      | 2 + 5 +3 |                       |

| PA17     | FCC1: RxD[15] UTOPIA 16 /    | 2+3      |                       |

| PA17     | FCC1: RxD[7] UTOPIA 8 /      | 2 + 5 +3 |                       |

| PA18     | FCC1: TxD[15] UTOPIA 16 /    | 2+3      |                       |

| PA18     | FCC1: TxD[7] UTOPIA 8 /      | 2 + 5 +3 |                       |

| PA19     | FCC1: TxD[14] UTOPIA 16 /    | 2+3      |                       |

| PA19     | FCC1: TxD[6] UTOPIA 8 /      | 2 + 5 +3 |                       |

| PA20     | FCC1: TxD[13] UTOPIA 16 /    | 2+3      |                       |

| PA20     | FCC1: TxD[5] UTOPIA 8 /      | 2 + 5 +3 |                       |

| PA21     | FCC1: TxD[12] UTOPIA 16 /    | 2+3      |                       |

| PA21     | FCC1: TxD[4] UTOPIA 8 /      | 2 + 5 +3 |                       |

| PA22     | FCC1: TxD[11] UTOPIA 16      | 2+3      |                       |

| PA22     | FCC1: TxD[3] UTOPIA 8 /      | 2 + 5 +3 |                       |

| PA23     | FCC1: TxD[10] UTOPIA 16      | 2+3      |                       |

| PA23     | FCC1: TxD[2] UTOPIA 8 /      | 2 + 5 +3 |                       |

| PA24     | FCC1: TxD[1] UTOPIA 8 /      | 2 + 5 +3 |                       |

| PA24     | FCC1: TxD[9] UTOPIA 16       | 2 +3     |                       |

| PA25     | FCC1: TxD[0] UTOPIA 8 /      | 2 + 5 +3 |                       |

| PA25     | FCC1: TxD[8] UTOPIA 16       | 2+3      |                       |

| PA26     | FCC1: RxClav UTOPIA master / | 3 + 5    |                       |

| PA27     | FCC1: RxSOC UTOPIA           | 3 + 5    |                       |

| PA28     | FCC1: RxEnb UTOPIA master    | 3 + 5    |                       |

| PA29     | FCC1: TxSOC UTOPIA           | 3 + 5    |                       |

| PA30     | FCC1: TxClav UTOPIA master / | 3 + 5    |                       |

| PA31     | FCC1: TxEnb UTOPIA master    | 3 + 5    |                       |

| PC10     | FCC1: TxD[2] UTOPIA 16       | 2 + 3    | FCC2: RxD[3] UTOPIA 8 |

| pin name | Function Name                                     | Switch # | Additional function          |

|----------|---------------------------------------------------|----------|------------------------------|

| PC12     | FCC1: RxAddr[1] MPHY, master                      | 3        | SCC2: CD /                   |

| PC13     | FCC1: TxAddr[1] MPHY, master                      | 3        | SCC2: CTS /                  |

| PC14     | FCC1: RxAddr[0] MPHY, master                      | 3        | SCC1: CD /                   |

| PC15     | FCC1: TxAddr[0] MPHY, master                      | 3        | SCC1: CTS /                  |

| PC6      | FCC1: RxAddr[2] MPHY, master, multiplexed polling | 3        |                              |

| PC7      | FCC1: TxAddr[2] MPHY master, multiplexed: polling | 3        |                              |

| PC8      | FCC1: TxD[0] UTOPIA 16                            | 2        |                              |

| PC9      | FCC1: TxD[1] UTOPIA 16                            | 2        |                              |

| PD14     | FCC1: RxD[0] UTOPIA 16                            | 2+3      |                              |

| PD15     | FCC1: RxD[1] UTOPIA 16                            | 2+3      |                              |

| PD16     | FCC1: TxPrty UTOPIA                               | 3 + 5    |                              |

| PD17     | FCC1: RxPrty UTOPIA                               | 3 + 5    |                              |

| PD20     | FCC1: RxD[2] UTOPIA 16                            | 2        |                              |

| PD21     | FCC1: RxD[3] UTOPIA 16                            | 2+3      |                              |

| PD22     | FCC1: TxD[5] UTOPIA 16                            | 2+3      |                              |

| PD23     | FCC1: RxD[4] UTOPIA 16                            | 2+3      |                              |

| PD24     | FCC1: RxD[5] UTOPIA 16                            | 2+3      |                              |

| PD25     | FCC1: TxD[6] UTOPIA 16                            | 2+3      |                              |

| PD26     | FCC1: RxD[6] UTOPIA 16                            | 2+3      | SCC2: RTS /                  |

| PD27     | FCC1: RxD[7] UTOPIA 16                            | 2+3      | SCC2: TXD                    |

| PD28     | FCC1: TxD[7] UTOPIA 16 bit                        | 2+3      | SCC2: RXD (secondary option) |

| PD29     | RTS1 signal for RS232-1 channel only              |          |                              |

| PD5      | FCC1: TxD[3] UTOPIA 16                            | 2+3      |                              |

| PD6      | FCC1: TxD[4] UTOPIA 16                            | 2+3      |                              |

| PC21     | FCC1: USED for RXCLK & TXCLK Utopia               |          |                              |

| PB18     | FCC2 RXD3 MII                                     | 4 + 5    | FCC2: RxD[4] UTOPIA 8        |

| PB19     | FCC2 RXD2 MII                                     | 4 + 5    | FCC2: RxD[5] UTOPIA 8        |

| PB20     | FCC2 RXD1 MII                                     | 4 + 5    | FCC2: RxD[6] UTOPIA 8        |

| PB21     | FCC2 RXD0 MII                                     | 4 + 5    | FCC2: RxD[7] UTOPIA 8        |

| PB22     | FCC2 TXD0 MII                                     | 4 + 5    | FCC2: TxD[7] UTOPIA 8        |

| PB23     | FCC2 TXD1 MII                                     | 4 + 5    | FCC2: TxD[6] UTOPIA 8        |

| PB24     | FCC2 TXD2 MII                                     | 4 + 5    | FCC2: TxD[5] UTOPIA 8        |

| pin name | Function Name                            | Switch #                   | Additional function                                                                                                                                                                                                                                                                                                                                                   |

|----------|------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PB25     | FCC2 TXD3 MII                            | 4 + 5                      | FCC2: TxD[4] UTOPIA 8                                                                                                                                                                                                                                                                                                                                                 |

| PB26     | FCC2 CRS MII                             | 4 + 5                      | FCC2: TxD[1] UTOPIA 8                                                                                                                                                                                                                                                                                                                                                 |

| PB27     | FCC2 COL MII                             | 4 + 5                      | FCC2: TxD[0] UTOPIA 8                                                                                                                                                                                                                                                                                                                                                 |

| PB28     | FCC2 RX-ER MII                           | RS232 switch               | SCC1: TXD Note: PB28 is used for FCC2 RXER in MII Mode & SCC1 TXD. PD30 used for FCC2 TXEN in Utopia Mode & SCC1 TXD. in order to use SCC1 in case for FCC2 Utopia or MII the user should change the configuration of the comming pin for SCC1 TXD. If FCC2 ATM is used the SCC1 TXD should be come from PB28. If FCC2 MII is used SCC1 TXD should be come from PD30. |

| PB29     | FCC2 TX-EN MII                           | 4 + 5                      | FCC2: RxClav UTOPIA master                                                                                                                                                                                                                                                                                                                                            |

| PB30     | FCC2 RX-DV MII                           | 4 + 5                      | FCC2: TxSOC UTOPIA                                                                                                                                                                                                                                                                                                                                                    |

| PB31     | FCC2 TX-ER MII                           | 4 + 5                      | FCC2: RxSOC UTOPIA                                                                                                                                                                                                                                                                                                                                                    |

| PC18     | FCC2 MII-TXCLK MII                       | 4                          |                                                                                                                                                                                                                                                                                                                                                                       |

| PC19     | FCC2 MII-RXCLK MII                       | 4                          | FCC2: RXCLK & TXCLK UTOPIA                                                                                                                                                                                                                                                                                                                                            |

| PA0      | FCC2: TxAddr[2] MPHY master              | n/a                        |                                                                                                                                                                                                                                                                                                                                                                       |

| PA1      | FCC2: TxAddr[1] MPHY master              | n/a                        |                                                                                                                                                                                                                                                                                                                                                                       |

| PA2      | FCC2: TxAddr[0] MPHY master              | n/a                        |                                                                                                                                                                                                                                                                                                                                                                       |

| PA3      | FCC2: RxAddr[0] MPHY master              | n/a                        |                                                                                                                                                                                                                                                                                                                                                                       |

| PA4      | FCC2: RxAddr[1] MPHY master              | n/a                        |                                                                                                                                                                                                                                                                                                                                                                       |

| PA5      | FCC2: RxAddr[2] MPHY master              | n/a                        |                                                                                                                                                                                                                                                                                                                                                                       |