Rev. 0.5

# **Peripheral Bus Control CPLD**

# **Wireless Solutions Division**

Eyal Liser Version 0.5 May 3, 2005

# **Revision Table**

| Notes                                                                                          | Author     | Date           | Version      |

|------------------------------------------------------------------------------------------------|------------|----------------|--------------|

| Initial version. Applied appropriate changes to ZAS PBC document to fit Tortola ADS            | Eyal Liser | March 25, 2005 | Revision 0.0 |

| Interrupt controller added to the document.                                                    | Eyal Liser | April 14, 2005 | Revision 0.1 |

| Interrupt description revised                                                                  | Eyal Liser | April 18, 2005 | Revision 0.2 |

| Some power up defaults changed, formatting revised,                                            | Eyal Liser | May 2, 2005    | Revision 0.3 |

| Revised interrupt section per OS teams requests                                                | Eyal Liser | May 3, 2005    | Revision 0.4 |

| UART selects Default changed. Vibrator default value changed. PCMCIA_EN bit added on BCTRL4(5) | Eyal Liser | May 24, 2005   | Revision 0.5 |

|                                                                                                |            |                |              |

Rev. 0.5

Peripheral Bus Control

# **1.1 Introduction**

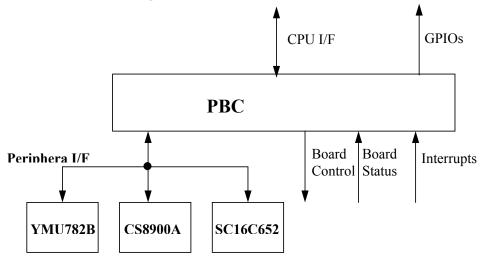

The Tortola EVB main board requires some glue logic for peripheral bus address decoding, board control and status signals, board revision registers, and other miscellaneous functions. This glue logic is implemented with a Complex Programmable Logic Device (CPLD). This document describes the functionality and requirements for the Peripheral Bus Control CPLD (PBC).

# **1.2 Features**

The key features provided by the PBC include:

- Provide a 16-bit slave interface to the CPU data bus

- Provide address decode and control for Ethernet controller

- Provide address decode and control for external UART controller

- Provide address decode for Audio Synthesizer.

- Provide control and status registers for various board functions.

- Provide control and muxing for interrupt sources from various sources.

Peripheral Bus Control

# 1.3 Block Diagram

# 1.4 CPU Interface

The Tortola CPU WEIM interface, referred in this document as the CPU Interface, has the capability to connect low to mid-range memories and peripherals with asynchronous and synchronous protocols. Several chip select signals are provided by the CPU, which can be configured for different memory types. The PBC uses the chip select signal CS4, with the following requirements:

- CS4 occupies a 32Mbyte window in the address space

- CS4 must be configured for 16-bit bus width, asynchronous transfers.

- CS4 assertion window must be at least 150nsec.

- Byte enables must be asserted at CS4 assertion time.

- Byte enables must be negated at least 1/2 clock before CS4 negation during write cycles.

- Multiplexed transfers and synchronous transfers are not supported.

| Signal  | DIR    | Description                                   |

|---------|--------|-----------------------------------------------|

| A[25:0] | In     | Address bus (not all address lines are used)  |

| D[15:0] | In/Out | Data bus                                      |

| CS4_B   | In     | Chip select 4 used for peripheral access      |

| BE0_B   | In     | Byte Enable 0, which corresponds with D[7:0]  |

| BE1_B   | In     | Byte Enable 1, which corresponds with D[15:8] |

| OE_B    | In     | Output Enable                                 |

| RW_B    | In     | Read/write signal                             |

| RSTIN_B | In     | Reset signal                                  |

| DMAREQ  | Out    | DMA Request to CPU                            |

# Table 1 CPU Signal Interface

# **1.5 Peripheral Interface**

The peripheral interface provides address decode and control for the CS8900A Ethernet controller the SC16C652 dual UART (DUART) controller and the YMU782B Audio Synthesizer.

### Table 2 Peripheral Interface

| Signal       | DIR   | Description                                                                    |

|--------------|-------|--------------------------------------------------------------------------------|

| PBA[2:0]     | Out   | Peripheral Bus Address                                                         |

| PBD[7:0]     | InOut | Peripheral Bus Data, used for DUART, board version, switches                   |

| IOR_B        | Out   | IO Read is asserted during I/O read transfers and DMA transfers                |

| IOW_B        | Out   | IO Write is asserted during I/O write transfers                                |

| MEMR_B       | Out   | Memory read to Ethernet controller is asserted during memory read transfers.   |

| MEMW_B       | Out   | Memory write to Ethernet controller is asserted during memory write transfers. |

| AEN          | Out   | DMA Address enable, asserted during Ethernet controller DMA transfers          |

| ENET_DMAREQ  | In    | DMA request from Ethernet controller                                           |

| ENET_DMACK_B | Out   | DMA acknowledge to Ethernet controller                                         |

| ENET_CS_B    | Out   | Ethernet chip select                                                           |

| UA_CS_B      | Out   | UART A chip select                                                             |

| UB_CS_B      | Out   | UART B chip select                                                             |

| SYNTH_CS     | Out   | Synthesizer chip select                                                        |

# 1.5.1 Peripheral Bus Cycles

The following peripheral bus cycles are implemented.

### Table 3 Bus Cycles

| Cycle    | Transfer size | Description                                                                                                              |

|----------|---------------|--------------------------------------------------------------------------------------------------------------------------|

| IOREAD   | Byte, Word    | Used to read 8/16-bit data from peripheral registers with IOR_B signal.                                                  |

| IOWRITE  | Byte, Word    | Used to write 8/16-bit data to peripheral registers with IOW_B signal.                                                   |

| MEMREAD  | Byte, Word    | Used to read 8/16-bit data from peripheral memory using MEMR_B signal.                                                   |

| MEMWRITE | Byte, Word    | Used to write 8/16-bit data to peripheral memory using MEMW_B signal.                                                    |

| DMAREAD  | Word          | Used during Ethernet DMA transfers to read 16-bit data from Ethernet controller memory buffer using ENET_DMACK_B signal. |

### 1.5.2 DMA operation

The CS8900A supports DMA slave transfers for received data frames. The PBC supports these DMA transfers using a single DMAREQ signal to the processor and a special DMA address space in the memory map. The ENET\_DMAREQ signal from the CS8900A is forwarded to the CPU I/F and used as a qualifier for DMA transfers. Qualified read transfer to the DMA address space will generate the ENET\_DMACK\_B signal to the CS8900A.

### 1.5.3 SC16C652C UART Decode

The PBC provides address decodes and data path control for the SC16C652C dual UART controller. Data is transferred through the PBC to and from the SC16C652C. The PBC hardware provides byte steering logic to transfer the correct byte to the SC16C652C during data transfers. The following points must be followed for accessing the SC16C652C

### 1.5.4 SCS8900A Ethernet Decode

The PBC provides address decode and control for the CS8900A Ethernet controller. Both 16-bit I/O mode and memory mode are supported. Memory mode operation allows direct access to the CS8900A internal registers and frame buffer. A single DMA request line is provided for DMA transfers from the CS8900A buffer to system memory for increased performance.

The following points must be followed for accessing the CS8900A:

• Provide a transition of the SBHE input after reset. This is done with a dummy byte read to an odd location, as for example a byte read to \$B400 0007.

• All reads and writes to the CS8900A must be 16-bits.

• For memory mode operation, the MEMORY BASE ADDRESS REGISTER (Offset \$002C) must be set to \$1000. Note that this is a 20 bit register, and the upper 4 bits must be 0.

### 1.5.5 YMU782B Audio Synthesizer Decode

The PBC provides address decode and data path control for the YMU782B Audio Synthesizer. Data is transferred through the PBC to and from the YMU782B. The PBC hardware provides byte steering logic to transfer the correct byte to the YMU782B during data transfers. The following points must be followed for accessing the YMU782B:

• All reads and writes to the YMU782B must be 8-bits.

# **1.6 UART Muxing**

UARTC has one DTR line coming from the UART transceiver. This line is muxed to either UART1 or UART2 of the CPU. The muxing is made according to UARTC\_SEL (BCTRL2.2).

# 1.7 Memory Map

#### Table 4 PBC Memory Map

| Name                  | Description                             | Address   |

|-----------------------|-----------------------------------------|-----------|

| VERSION               | Version register                        | B400_0000 |

| BSTAT2                | Board status register 2                 | B400_0002 |

|                       | Board control register 1 set address    | B400_0004 |

| BCTRL1                | Board control register 1 clear address  | B400_0006 |

|                       | Board control register 2 set address    | B400_0008 |

| BCTRL2                | Board control register 2 clear address  | B400_000A |

|                       | Board control register 3 set address    | B400_000C |

| BCTRL3                | Board control register 3 clear address  | B400_000E |

|                       | Board control register 4 set address    | B400_0010 |

| BCTRL4                | Board control register 4 clear address  | B400_0012 |

| BSTAT1                | Board status register 1                 | B400_0014 |

| INT STATUS            | Interrupt status register address       | B400_0016 |

| INT CURRENT<br>STATUS | Interrupt CURRENT STATUS register       | B400_0018 |

| INT MASK              | Interrupt mask register set address     | B400_001A |

| INT MASK              | Interrupt mask register clear address   | B400_001C |

| 00100050              | External UART port A                    | B401_0000 |

| SC16C652              | External UART port B                    | B401_0010 |

| 000000                | Ethernet Controller I/O base address    | B402_0000 |

| CS8900A               | Ethernet Controller Memory base address | B402_1000 |

|                       | Ethernet Controller DMA base address    | B402_2000 |

| YMU782B               | Audio synthesizer port                  | B403_0000 |

| CODE_B                | Code test debug enable                  | B407_0000 |

Peripheral Bus Control

# **1.8 Register descriptions**

#### 1.8.1 Version register

The version register contains three fields with the version of the PBC, CPU board, and BASE board. The PBC version is an 8-bit hardwired field that will be changed with design changes to the PBC. The CPU and BASE fields are implemented as two 4-bit fields and configured with external input signals connected to pull up and pull down resistors. The CPU and BASE fields are muxed on the Peripheral Data bus.

#### **Table 5 Version Register**

| NAME  | VERSION |                                                                                                                                                     |  |    |    |  |  |  |          |   |   |  |  |   |    |  |

|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|----|----|--|--|--|----------|---|---|--|--|---|----|--|

| BIT   | 15      | 15         14         13         12         11         10         9         8         7         6         5         4         3         2         1 |  |    |    |  |  |  |          |   |   |  |  | 0 |    |  |

| FIELD |         |                                                                                                                                                     |  | PE | BC |  |  |  | CPU BASI |   |   |  |  |   | SE |  |

| OPER  |         |                                                                                                                                                     |  | F  | ٢  |  |  |  |          | I | ۲ |  |  | I | ٢  |  |

# **1.9 Board status registers**

### 1.9.1 Board Status Register 1

BSTAT1 contains several bits that represent the board status from different places on the board. These registers are read only.

#### Table 6 Board Status Register 1

| NAME   |     |     |     |              |     |                 |                 | BST        | AT1        |             |              |               |                |                 |           |            |

|--------|-----|-----|-----|--------------|-----|-----------------|-----------------|------------|------------|-------------|--------------|---------------|----------------|-----------------|-----------|------------|

| BIT    | 15  | 14  | 13  | 12           | 11  | 10              | 9               | 8          | 7          | 6           | 5            | 4             | 3              | 2               | 1         | 0          |

| FIELD  | RSV | RSV | RSV | ATLAS_<br>IN | PTT | FLIP_<br>SENSE2 | FLIP_<br>SENSE1 | SD2_<br>WP | SD1_<br>WP | PWR_<br>RDY | ATA_<br>DASP | ATA_<br>CBLID | ATA_<br>IOCS16 | LIGHT_<br>SENSE | KP_<br>ON | NF_<br>DET |

| OPER   | R   | R   | R   | R            | R   | R               | R               | R          | R          | R           | R            | R             | R              | R               | R         | R          |

| RESET  | 0   | 0   | 0   | -            | -   | -               | -               | -          | -          | -           | -            | -             | -              | -               | -         | -          |

| IN/OUT | -   | -   | -   | IN           | IN  | IN              | IN              | IN         | IN         | IN          | IN           | IN            | IN             | IN              | IN        | IN         |

#### Table 7 Board Status Register 1 Bit Definitions

| Name        | Description                                                | Settings                            |

|-------------|------------------------------------------------------------|-------------------------------------|

| NF_DET      | Nand Flash Detect— indicates Nand Flash card insertion.    | 0 = Nand Flash card is inserted     |

| Bit 0       |                                                            | 1 = Nand Flash card is not inserted |

| KP_ON       | Keypad On/Off— indicates if keypad is on/off               | 0 = Keypad is ON                    |

| Bit 1       |                                                            | 1 = Keypad is OFF                   |

| LIGHT_SENSE | Light sense— This signal reflects the light sense output   | 0 = Light sense is $0$              |

| Bit 2       | from the keypad                                            | 1 = Light sense is  1               |

| ATA_IOCS16  | ATA IOCS16 – This bit reflects the status of pin IOCS16 on | 0 – IOCS16 state is 0               |

| Bit 3       | the ATA connector                                          | 1 – IOCS16 state is 1               |

| ATA_CBLID   | ATA CBLID – This bit reflects the status of pin CBLID on   | 0 – CBLID state is 0                |

| Bit 4       | the ATA connector                                          | 1 – CBLID state is 1                |

| ATA_DASP    | ATA DASP – This bit reflects the status of pin DASP on     | 0 – DASP state is 0                 |

| Bit 5       | the ATA connector                                          | 1 – DASP state is 1                 |

| PWR_RDY     | Power Ready— Power ready indication from Atlas board.      | 0 = Atlas power is not ready        |

| Bit 6       |                                                            | 1 = Atlas power is ready            |

| SD1_WP      | SD1 Write Protect — This bit reflects the Write Protect on | 0 = SD1 card is Write Protected     |

| Bit 7       | SD1 card.                                                  | 1 = SD1 card is not Write Protected |

| SD2_WP      | SD2 Write Protect — This bit reflects the Write Protect on | 0 = SD2 card is Write Protected     |

| Name        | Description                                                    | Settings                            |

|-------------|----------------------------------------------------------------|-------------------------------------|

| Bit 8       | SD2 card.                                                      | 1 = SD2 card is not Write Protected |

| FLIP_SENSE1 | Flip Sense 1 – This bit reflects the status of pin             | 0 = Flip Sense 1 on keypad is 0.    |

| Bit 9       | Flip_Sense1 on the keypad connector                            | 1 = Flip Sense 1 on keypad is 1.    |

| FLIP_SENSE2 | Flip Sense 2 – This bit reflects the status of pin             | 0 = Flip Sense 2 on keypad is 0.    |

| Bit 10      | Flip_Sense2 on the keypad connector                            | 1 = Flip Sense 2 on keypad is 1.    |

| РТТ         | <b>PTT button</b> – This bit reflects the status of pin PTT on | 0 = PTT signal on keypad is 0.      |

| Bit 11      | the keypad connector                                           | 1 = PTT signal on keypad is 1.      |

| ATLAS_IN    | ATLAS IN – This bit indicates if the power management board    | 0 = Atlas board is placed           |

| Bit 12      | (Atlas) is placed on the board.                                | 1 = Atlas board is not placed       |

| RSV         | Reserved- For future use                                       | Always reads 0                      |

| Bits 13:15  |                                                                |                                     |

Rev. 0.5

# 1.9.2 Board Status Register 2

BSTAT2 contains several bits that represent the board status from different places on the board. These registers are read only.

#### Table 8 Board Status Register

| NAME  |     |     |     |     |     |     | BSTAT  | 2       |   |     |   |   |   |   |   |   |

|-------|-----|-----|-----|-----|-----|-----|--------|---------|---|-----|---|---|---|---|---|---|

| BIT   | 15  | 14  | 13  | 12  | 11  | 10  | 10 9 8 |         | 7 | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

| FIELD | RSV    | DMA_REQ |   | DSW |   |   |   |   |   |   |

| OPER  | R   | R   | R   | R   | R   | R   | R      | R       | R |     |   |   |   |   |   |   |

#### Table 9 Board Status Register 1 Bit Definitions

| Name      | Description                                                     | Settings                        |

|-----------|-----------------------------------------------------------------|---------------------------------|

| DSW       | Debug switch—This 8-bit field contains the value of the         | 0 (each bit) = switch is closed |

| Bits 7:0  | debug DIP switch.                                               | 1(each bit) = switch is open    |

| DMA_REQ   | DMA Request – this bit reflects the DMA request to CPU from the | 0 = DMA Request is low          |

| Bit 8     | Ethernet controller                                             | 1 = DMA Request is high         |

| RSV       | Reserved—These bits are reserved for future use.                | Always read as 0                |

| Bits 9:15 |                                                                 |                                 |

Peripheral Bus Control

### 1.9.3 Board Control Register 1

BCTRL1 contains several fields to control various board functions. This register is implemented as a set register and a clear register. To set a bit, the set address is used, writing a 1 to the desired bit. To clear a bit, the clear address is used, writing a 1 to the desired bit.

| NAME   |        |      |        |        |        |        | BCTRL1 |        |            |            |               |              |             |             |               |              |  |  |  |  |  |

|--------|--------|------|--------|--------|--------|--------|--------|--------|------------|------------|---------------|--------------|-------------|-------------|---------------|--------------|--|--|--|--|--|

| BIT    | 15     | 14   | 13     | 12     | 11     | 10     | 9      | 8      | 7          | 6          | 5             | 4            | 3           | 2           | 1             | 0            |  |  |  |  |  |

| FIELD  | LCDON  | BEND |        | CCTL2  |        |        | CCTL1  |        | LED1_<br>B | LED0_<br>B | IRDA_<br>EN_B | UCE_<br>EN_B | UB_<br>EN_B | UA_<br>EN_B | XUART_<br>RST | ENET_<br>RST |  |  |  |  |  |

| OPER   | R/W    | R/W  | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W        | R/W        | R/W           | R/W          | R/W         | R/W         | R/W           | R/W          |  |  |  |  |  |

| RESET  | 0      | 0    | 0      | 0      | 0      | 0      | 0      | 0      | 0          | 1          | 1             | 1            | 1           | 1           | 0             | 0            |  |  |  |  |  |

| IN/OUT | OUT/OD | -    | OUT/OD | OUT/OD | OUT/OD | OUT/OD | OUT/OD | OUT/OD | OUT        | OUT        | OUT/OD        | OUT/OD       | OUT/OD      | OUT/OD      | OUT           | OUT          |  |  |  |  |  |

#### Table 10 Board Control Register 1

#### Table 11 Board Control Register 1 Bit Definitions

| Name      | Description                                                    | Settings                                       |

|-----------|----------------------------------------------------------------|------------------------------------------------|

| ENET_RST  | Ethernet Reset—Reset the Ethernet controller. This bit         | 0 = Ethernet controller reset signal negated.  |

| Bit 0     | must be set for the desired duration of the reset signal, then | 1 = Ethernet controller reset signal asserted. |

|           | cleared to remove the reset signal.                            |                                                |

| XUART_RST | External UART Reset—Reset external UART controller.            | 0 = UART controller reset signal negated.      |

| Bit 1     | This bit must be set for the desired duration of the reset     | 1 = UART controller reset signal asserted.     |

|           | signal, then cleared to remove the reset signal.               |                                                |

| UA_EN_B   | UART A Enable—Enable UART A transceiver.                       | 0 = UART A transceiver enabled.                |

| Bit 2     |                                                                | 1 = UART A transceiver disabled                |

| UB_EN_B   | UART B Enable—Enable UART B transceiver                        | 0 = UART B transceiver enabled.                |

| Bit 3     |                                                                | 1 = UART B transceiver disabled                |

| UCE_EN_B  | UART C Enable—Enable UART C transceiver.                       | 0 = UART C transceiver enabled.                |

| Bit 4     |                                                                | 1 = UART C transceiver disabled                |

| IRDA_EN_B | IRDA Enable—Used to enable the IRDA transmitter.               | 0 = IRDA transmitter enabled                   |

| Bit 5     |                                                                | 1 = IRDA transmitter disabled                  |

| LED0_B    | LED 0 on—Used to turn LED 0 on. This is used as                | 0 = LED 0 is off                               |

| Bit 6     | a general purpose status indicator.                            | 1 = LED  0 is on.                              |

| Name                     | Description                                                                                                             | Settings                              |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| <b>LED1_B</b><br>Bit 7   | <b>LED 1 on</b> —Used to turn LED 1 on. This is used as a general purpose status indicator.                             | 0 = LED 1 is off.<br>1 = LED 1 is on. |

| CCTL1[2:0]<br>Bits 8-10  | <b>CSI1 Control</b> —CSI1 control provides a three bit field for control of user defined functions on the CSI connector | xxx = User defined function.          |

| CCTL2[2:0]<br>Bits 11-13 | <b>CSI2</b> Control —CSI2 control provides a three bit field for control of user defined functions on the CSI connector | xxx = User defined function.          |

| BEND                     | Internal register used as endian indicator                                                                              |                                       |

| LCDON                    | LCD ON—Used to turn the QVGA dumb LCD display on.                                                                       | 0 = LCD is off                        |

| Bit 15                   |                                                                                                                         | 1 = LCD on                            |

### 1.9.4 Board Control Register 2

BCTRL2 contains several bits to control various board functions. This register is implemented as a set register and a clear register. To set a bit, the set address is used, writing a 1 to the desired bit. To clear a bit, the clear address is used, writing a 1 to the desired bit.

#### Table 12 Board Control Register 2

| NAME   |            |            |       |              |              |              |              | BCT          | 'RL2        |            |            |             |             |        |        |        |

|--------|------------|------------|-------|--------------|--------------|--------------|--------------|--------------|-------------|------------|------------|-------------|-------------|--------|--------|--------|

| BIT    | 15         | 14         | 13    | 12           | 11           | 10           | 9            | 8            | 7           | 6          | 5          | 4           | 3           | 2      | 1      | 0      |

| FIELD  | VCC_<br>EN | VPP_<br>EN | CT_CS | LCDIO<br>_EN | LCD_<br>RST2 | LCD_<br>RST1 | LCD_<br>RST0 | IRDA_<br>MOD | ATA_<br>SEL | ATA_<br>EN | CSI_<br>EN | UMOD<br>ENC | UMOD<br>ENA | USELC  | USELB  | USELA  |

| OPER   | R/W        | R/W        | R/W   | R/W          | R/W          | R/W          | R/W          | R/W          | R/W         | R/W        | R/W        | R/W         | R/W         | R/W    | R/W    | R/W    |

| RESET  | 0          | 0          | 1     | 1            | 1            | 1            | 1            | 0            | 0           | 1          | 1          | 1           | 1           | 1      | 0      | 1      |

| IN/OUT | OUT        | OUT        | OUT   | OUT/OD       | OUT/OD       | OUT/OD       | OUT/OD       | OUT          | OUT         | OUT        | OUT        | OUT         | OUT         | OUT/OD | OUT/OD | OUT/OD |

#### Table 13 Board Control Register 2 Bit Definitions

| Name  | Description                                    | Settings                         |

|-------|------------------------------------------------|----------------------------------|

| USELA | UART A SELECT—Select UART A source on the CPU. | 0 = the source is UART1 signals. |

| Bit 0 |                                                | 1 = the source is UART5 signals  |

| USELB | UART B SELECT—Select UART B source on the CPU. | 0 = the source is UART3 signals. |

| Bit 1 |                                                | 1 = the source is UART4 signals  |

| USELC | UART C SELECT—Select UART C source on the CPU. | 0 = the source is UART2 signals. |

| Name              | Description                                                   | Settings                                                                                                |  |  |  |  |  |  |  |

|-------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Bit 2             |                                                               | 1 = the source is UART1 signals                                                                         |  |  |  |  |  |  |  |

| UMODENA           | UART A MODEM Enable—Enables UART A MODEM                      | 0 = UART C MODEM signals enabled                                                                        |  |  |  |  |  |  |  |

| Bit 3             | signals.                                                      | 1 = UART C MODEM signals disabled                                                                       |  |  |  |  |  |  |  |

| UMODENC           | UART C MODEM Enable—Enables UART C MODEM                      | 0 = UART C MODEM signals enabled                                                                        |  |  |  |  |  |  |  |

| Bit 4             | signals                                                       | 1 = UART C MODEM signals disabled                                                                       |  |  |  |  |  |  |  |

| CSI_EN            | CSI Enable—Used to enable the CSI Interface.                  | 0 = CSI enabled                                                                                         |  |  |  |  |  |  |  |

| Bit 5             |                                                               | 1 = CSI disabled                                                                                        |  |  |  |  |  |  |  |

| ATA_EN            | ATA_Enable—Enables ATA interface.                             | 0 = ATA enabled                                                                                         |  |  |  |  |  |  |  |

| Bit 6             |                                                               | 1 = ATA disabled                                                                                        |  |  |  |  |  |  |  |

| ATA_SEL           | ATA Select— Selects the signals of the cpu that will          | 0 = group A is connected to ATA interface                                                               |  |  |  |  |  |  |  |

| Bit 7             | connect to the ATA interface.                                 | 1 = group B is connected to ATA interface                                                               |  |  |  |  |  |  |  |

| IRDA_MOD          | IRDA Mode —this bit selects the bandwidth of the IRDA         | A transition from high to low while<br>IRDA_TXD is low – SIR/MIR bandwidth                              |  |  |  |  |  |  |  |

| Bit 8             | Transceiver.                                                  | A transition from high to low while<br>IRDA_TXD is high – FIR bandwidth                                 |  |  |  |  |  |  |  |

| LCDRST0           | <b>LCD 0 Reset</b> —This bit resets the smart parallel LCD #1 | 0 = smart parallel LCD #1 reset signal<br>negated<br>1 = smart parallel LCD #1 reset signal             |  |  |  |  |  |  |  |

| Bit 9             |                                                               | asserted                                                                                                |  |  |  |  |  |  |  |

| LCDRST1<br>Bit 10 | LCD 1 Reset —This bit resets the smart parallel LCD #2        | 0 = smart parallel LCD #2 reset signal<br>negated<br>1 = smart parallel LCD #2 reset signal<br>asserted |  |  |  |  |  |  |  |

| LCDRST2           | LCD 2 Reset —This bit resets the smart serial LCD             | 0 = smart serial LCD reset signal negated                                                               |  |  |  |  |  |  |  |

| Bit 11            |                                                               | 1 = smart serial LCD reset signal asserted                                                              |  |  |  |  |  |  |  |

| LCDIO_EN          | LCD GPIO Enable – Enables GPIO1 and GPIO2                     | 0= connection with GPIO1 and GPIO2 is<br>enabled                                                        |  |  |  |  |  |  |  |

| Bit 12            | interface with the LCD connectors for general purpose use.    | 1= connection with GPIO1 and GPIO2 is disabled                                                          |  |  |  |  |  |  |  |

| RSV               | Reserved- For future use                                      | Always reads 0                                                                                          |  |  |  |  |  |  |  |

| Bit 13            |                                                               |                                                                                                         |  |  |  |  |  |  |  |

| VPPEN             | VPP Enable – enables VPP power towards the PCMCIA.            | 0= PCMCIA VPP power is off                                                                              |  |  |  |  |  |  |  |

| Bit 14            |                                                               | 1= PCMCIA VPP power is VCC power<br>(3.3V)                                                              |  |  |  |  |  |  |  |

| VCCEN             | VCC Enable - enables VCC power towards the PCMCIA.            | 0= PCMCIA VCC power is off                                                                              |  |  |  |  |  |  |  |

| Bit 15            |                                                               | 1= PCMCIA VCC power is 3.3V                                                                             |  |  |  |  |  |  |  |

OPER

RESET

IN/OUT

R/W

1

OUT

R/W

0

OUT/OD OUT/OD

R/W

0

R/W

1

OUT

R/W

0

OUT

R/W

0

OUT

### 1.9.5 Board Control Register 3

BCTRL3 contains several bits to control various board functions. This register is implemented as a set register and a clear register. To set a bit, the set address is used, writing a 1 to the desired bit. To clear a bit, the clear address is used, writing a 1 to the desired bit.

| NAME  |                |              |             |               |               |               |                     | BCT                 | TRL3          |             |            |             |            |             |   |

|-------|----------------|--------------|-------------|---------------|---------------|---------------|---------------------|---------------------|---------------|-------------|------------|-------------|------------|-------------|---|

| BIT   | 15             | 14           | 13          | 12            | 11            | 10            | 9                   | 8                   | 7             | 6           | 5          | 4           | 3          | 2           |   |

| FIELD | SPI3_<br>RESET | VESIM<br>_EN | VSIM_<br>EN | SYNTH_<br>RST | CARD2_<br>SEL | CARD1_<br>SEL | FSH_<br>VBUS_<br>EN | OTG_<br>VBUS_<br>EN | OTG_<br>HS_EN | FSH_<br>MOD | HSH_<br>EN | HSH_<br>SEL | FSH_<br>EN | FSH_<br>SEL | 1 |

R/W

1

#### **Table 14 Board Control Register 3**

R/W

1

OUT/OD OUT/OD OUT/OD

R/W

1

R/W

0

OUT

R/W

1

OUT

R/W

0

OUT

R/W

1

OUT

R/W

0

OUT

#### **Table 15 Board Control Register 3 Bit Definitions**

| Name        | Description                                              | Settings                               |

|-------------|----------------------------------------------------------|----------------------------------------|

| OTG_FS_SEL  | USB OTG Full Speed Select—Select The source of the USB   | 0 = the source is the ATLAS board.     |

| Bit 0       | OTG Full speed interface.                                | 1 = the source is the CPU.             |

| OTG_FS_EN   | USB OTG Full Speed Enable — Enables the USB OTG Full     | 0 = OTG Full Speed Interface enabled   |

| Bit 1       | speed interface on the CPU.                              | 1 = OTG Full Speed Interface disabled  |

| FSH_SEL     | USB Full Speed Host Select— Select The source of the USB | 0 = Group A on the CPU                 |

| Bit 2       | Full speed Host interface.                               | 1 = Group B on the CPU                 |

| FSH_EN      | USB Full Speed Host Enable— Enables the USB Full speed   | 0 = Full Speed Host Interface enabled  |

| Bit 3       | Host interface.                                          | 1 = Full Speed Host Interface disabled |

| HSH_SEL     | USB High Speed Host Select— Select The source of the USB | 0 = Group A on the CPU                 |

| Bit 4       | High speed Host interface.                               | 1 = Group B on the CPU                 |

| HSH_EN      | USB High Speed Host Enable— Enables the USB High speed   | 0 = High Speed Host Interface enabled  |

| Bit 5       | Host interface.                                          | 1 = High Speed Host Interface disabled |

| FSH_MODE    | USB Full Speed Host Mode— Selects Single ended/          | 0 = Single ended mode                  |

| Bit 6       | differential mode on USB Host Full Speed interface.      | 1 = Differential mode                  |

| OTG_HS_EN   | USB OTG High Speed Enable — Enables the USB OTG          | 0 = OTG High Speed Interface enabled   |

| Bit 7       | High speed interface on the CPU.                         | 1 = OTG High Speed Interface disabled  |

| OTG_VBUS_EN | USB OTG VBUS Enable — Enables VBUS regulator on          | 0 = OTG VBUS regulator is enabled      |

0

OTG\_

R/W

1

OUT

Ē

F S S E

1

OTG

FS\_EN

R/W

1

OUT

| Name        | Description                                               | Settings                                            |

|-------------|-----------------------------------------------------------|-----------------------------------------------------|

| Bit 8       | USB OTG interface PHY.                                    | 1 = OTG VBUS regulator is disabled                  |

| FSH_VBUS_EN | USB Full Speed Host VBUS Enable — Enables VBUS            | 0 = Full Speed Host VBUS regulator is enabled       |

| Bit 9       | regulator on USB Full speed Host interface PHY.           | 1 = Full Speed Host VBUS regulator is disabled      |

| CARD1_SEL   | Card1 Select Mux select pin for SD1 / MS1 lines           | 0 = lines are dedicated to SD1 interface            |

| Bit 10      |                                                           | 1 = lines are dedicated to MS1 interface            |

| CARD2_SEL   | Card2 Select— Mux select pin for PCMCIA & SD2 / MS2 lines | 0 = lines are dedicated to PCMCIA &SD2<br>interface |

| Bit 11      |                                                           | 1 = lines are dedicated to MS2 interface            |

| SYNTH_RST   | Audio Synthesizer Reset – Reset signal towards Audio      | 0= Reset audio Synthesizer                          |

| Bit 12      | Synthesizer                                               | l=Normal operation                                  |

| VSIM_EN     | VSIM Enable— Enables VSIM regulator on the ATLAS          | 0 = VSIM regulator is disabled                      |

| Bit 13      | board.                                                    | 1 = VSIM regulator is enabled                       |

| VESIM_EN    | VESIM Enable— Enables VESIM regulator on the ATLAS        | 0 = VESIM regulator is disabled                     |

| Bit 14      | board.                                                    | 1 = VESIM regulator is enabled                      |

| SPI3_RESET  | CSPI3 Connector Reset — Reset signal towards CSPI3        | 0 = CSPI3 is reset                                  |

| Bit 15      | connector                                                 | 1 = Normal operation                                |

# 1.9.6 Board Control Register 4

BCTRL4 contains several bits to control various board functions. This register is implemented as a set register and a clear register. To set a bit, the set address is used, writing a 1 to the desired bit. To clear a bit, the clear address is used, writing a 1 to the desired bit.

| NAME   |     | BCTRL4 |     |     |     |     |     |     |     |     |             |               |            |              |               |                |

|--------|-----|--------|-----|-----|-----|-----|-----|-----|-----|-----|-------------|---------------|------------|--------------|---------------|----------------|

| BIT    | 15  | 14     | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5           | 4             | 3          | 2            | 1             | 0              |

| FIELD  | RSV | RSV    | RSV | RSV | RSV | RSV | RSV | RSV | RSV | RSV | CLR_<br>POE | PCMCIA_<br>EN | VIB_<br>EN | USER_<br>OFF | REGEN_<br>SEL | CSI_<br>MSB_EN |

| OPER   | R   | R      | R   | R   | R   | R   | R   | R   | R   | R   | R/W         | R/W           | R/W        | R/W          | R/W           | R/W            |

| RESET  | 0   | 0      | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1           | 1             | 0          | 0            | 1             | 1              |

| IN/OUT | -   | -      | -   | -   | -   | -   | -   | -   | -   | -   | OUT         | OUT           | OUT/OD     | OUT/OD       | OUT/OD        | OUT/OD         |

#### Table 16 Board Control Register 4

#### Table 17 Board Control Register 4 Bit Definitions

| Name               | Description                                                                                    | Settings                                               |

|--------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| CSI_MSB_EN         | CSI MSB Enable - Enables bits CSI_Data[3:0] from                                               | $0 = CSI_Data[3:0]$ enabled                            |

| Bit 0              | CSI interface.                                                                                 | $1 = CSI_Data[3:0]$ disabled                           |

| REGEN_SEL<br>Bit 1 | <b>Regulator Enable Select</b> — This bit selects predefined programming for Atlas regulators. | 0 = REGEN_SEL is active<br>1 = REGEN_SEL is not active |

| USER_OFF           | User Off Indication — This signal is sent to the Atlas                                         | 0 = normal operation                                   |

| Bit 2              | board to confirm user off mode after a power fail.                                             | 1 = user off confirmation                              |

| VIB_EN             | Vibrator Enable — Enables the Vibrator regulator on the                                        | 0 = Vibrator regulator is disabled                     |

| Bit 3              | Atlas board.                                                                                   | 1 = Vibrator regulator is enabled                      |

| PCMCIA_EN          | PCMCIA Enable — Enables the PCMCIA buffer                                                      | 0 = PCMCIA buffer enabled                              |

| Bit 4              |                                                                                                | 1 = PCMCIA buffer disabled                             |

| CLR_POE            | PCMCIA Output Enable Clear — Clears the PCMCIA<br>Output                                       | 0 = PCMCIA OE                                          |

| Bit 5              | enable                                                                                         | 1 = PCMCIA buffer disabled                             |

| USB_HS_PHY_EN      | USB High Speed PHY Enable — Enables the PHY of the                                             | 0 = USB High Speed PHY enabled                         |

| Bit 6              | USB High Speed                                                                                 | 1 = USB High Speed PHY disabled                        |

| RSV                | Reserved- For future use                                                                       | Always reads 0                                         |

Bits 7:15

# 1.10Interrupts

The Tortola ADS has several interrupt sources that the CPU must handle. The number of interrupt sources is larger than the number of GPIO pin available on the CPU. Therefore all interrupt sources are routed through the CPLD where some of them are grouped. An Interrupt Mask Register can disable each interrupt source.

#### 1.10.1 Interrupt Status/Clear Register

The Interrupt Status Register reflects the status of each interrupt source on the ADS. There are two interrupt types, level and edge triggered. Edge triggered interrupts generate an interrupt whenever the source signal changes from high to low, or low to high. The user may reset these by writing a one (high) to the associated bit. Writing a zero (low) will leave the status bit unaffected. Level interrupts are generated when the chosen active level (high or low) is detected. These require a software service routine to reset the interrupt signal back to the inactive state at the source. Writing to level sensitive interrupt status of all level sensitive interrupts will be inactive.

The register may be read at any time.

#### Table 18 Interrupt Status/Clear Register

| NAME  |     | Interrupt Status Register |             |               |                |                |                    |              |     |     |     |     |             |                    |            |             |

|-------|-----|---------------------------|-------------|---------------|----------------|----------------|--------------------|--------------|-----|-----|-----|-----|-------------|--------------------|------------|-------------|

| BIT   | 15  | 14                        | 13          | 12            | 11             | 10             | 9                  | 8            | 7   | 6   | 5   | 4   | 3           | 2                  | 1          | 0           |

| FIELD | RES | CE_<br>INT2               | CE_<br>INT1 | SYNTH_<br>IRQ | XUART_<br>INTB | XUART_<br>INTA | OTG_<br>FS_<br>INT | ENET_<br>INT | RES | RES | RES | RES | FSH_<br>OVR | OTG_<br>FS_<br>OVR | PB_<br>IRQ | LOW_<br>BAT |

| OPER  | -   | R                         | R           | R             | R              | R              | R                  | R            | -   | -   | -   | -   | R/W1C       | R/W1C              | R/W1C      | R/W1C       |

| RESET | 0   | 0                         | 0           | 0             | 0              | 0              | 0                  | 0            | 0   | 0   | 0   | 0   | 0           | 0                  | 0          | 0           |

#### Table 19 Interrupt Status/Clear Register Bit Definitions

| Name    | Description                                                   | Settings                                  |

|---------|---------------------------------------------------------------|-------------------------------------------|

| LOW_BAT | Low Battery— Low Battery signal from Atlas has changed state. | 0 – No interrupt pending                  |

| Bit 0   |                                                               | 1- Interrupt active, write a one to clear |

| Name               | Description                                                                   | Settings                                                  |  |  |  |  |  |

|--------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------|--|--|--|--|--|

| PB_IRQ             | <b>Push Button IRQ</b> — Push button switch circuit output has changed state. | 0 – No interrupt pending                                  |  |  |  |  |  |

| Bit 1              |                                                                               | 1- Interrupt active, write a one to clear                 |  |  |  |  |  |

| OTG_FS_OVR         | USB OTG Full Speed Over Current — The USB OTG Full                            | 0 – No interrupt pending                                  |  |  |  |  |  |

| Bit 2              | Speed Over Current bit has changed state.                                     | 1- Interrupt active, write a one to clear                 |  |  |  |  |  |

| FSH_OVR            | USB Full Speed Host Over Current — The USB Full Speed                         | 0 - No interrupt pending                                  |  |  |  |  |  |

| Bit 3              | Host interface. Overcurrent bit has changed state.                            | 1- Interrupt active, write a one to clear                 |  |  |  |  |  |

| RES                |                                                                               |                                                           |  |  |  |  |  |

| Bits 4,5,6,7, & 15 | Reserved for future use                                                       | N/A                                                       |  |  |  |  |  |

| ENET_INT           | Ethernet Interrupt - interrupt signal from Ethernet                           | 0= no interrupt from Ethernet controller                  |  |  |  |  |  |

| Bit 8              | controller                                                                    | 1= Interrupt received from Ethernet controller            |  |  |  |  |  |

| OTG_FS_INT         | USB Host Full Speed Interrupt — This bit is the interrupt                     | 0= no interrupt from USB Host full speed interface.       |  |  |  |  |  |

| Bit 9              | indication from USB Host full speed interface.                                | 1= Interrupt received from USB Host full speed interface. |  |  |  |  |  |

| XUART_INTA         | External UART A interrupt – interrupt signal from External                    | 0= no interrupt from External UART A                      |  |  |  |  |  |

| Bit 10             | UART A.                                                                       | 1= Interrupt received from External UART A                |  |  |  |  |  |

| XUART_INTB         | External UART B interrupt – interrupt signal from External                    | 0= no interrupt from External UART B                      |  |  |  |  |  |

| Bit 11             | UART B.                                                                       | 1= Interrupt received from External UART B                |  |  |  |  |  |

| SYNTH_IRQ          | Audio Synthesizer IRQ – interrupt signal from Audio                           | 0= no interrupt from Audio Synthesizer                    |  |  |  |  |  |

| Bit 12             | Synthesizer                                                                   | 1= Interrupt received from Audio Synthesizer              |  |  |  |  |  |

| CE_INT1            | Communication Engine Interrupt 1—                                             | 0 = No interrupt from CE_INT1                             |  |  |  |  |  |

| Bit 13             |                                                                               | 1 = Interrupt received from CE_INT1                       |  |  |  |  |  |

| CE_INT2            | Communication Engine Interrupt 2—                                             | 0 = No interrupt from CE_INT2                             |  |  |  |  |  |

| Bit 14             |                                                                               | 1 = Interrupt received from CE_INT2                       |  |  |  |  |  |

# 1.10.2 Interrupt Signal Current State Status Register

This register represents the current state of each edge triggered interrupt source. This register is a read only register.

#### Table 20 Interrupt Signal Current State Status Register

| NAME  |     | Interrupt Current State Status Register |     |     |     |     |     |     |     |     |     |     |             |                    |            |             |

|-------|-----|-----------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------------|--------------------|------------|-------------|

| BIT   | 15  | 14                                      | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3           | 2                  | 1          | 0           |

| FIELD | RES | RES                                     | RES | RES | RES | RES | RES | RES | RES | RES | RES | RES | FSH_<br>OVR | OTG_<br>FS_<br>OVR | PB_<br>IRQ | LOW_B<br>AT |

#### Table 21 Interrupt Current Status Register Bit Definitions

| Name       | Description                                           | Settings                      |

|------------|-------------------------------------------------------|-------------------------------|

| LOW_BAT    | Low Battery— Low Battery Indicator signal from Atlas  | 0 - Low Battery indication    |

| Bit 4      | Board.                                                | 1- Normal operation           |

| PB_IRQ     | Push Button IRQ — Push button switch circuit.         | 0 – Push button is pressed    |

| Bit 5      |                                                       | 1- Push button is not pressed |

| OTG_FS_OVR | USB OTG Full Speed Over Current — USB OTG Full        | 0 – Over Current indication   |

| Bit 6      | Speed Over Current indication.                        | 1- No Over Current indication |

| FSH_OVR    | USB Full Speed Host Over Current — The USB Full Speed | 0 – Over Current indication   |

| Bit 7      | Host interface. Over current indication.              | 1- No Over Current indication |

Peripheral Bus Control

### 1.10.3 Interrupt Mask Register

The Interrupt Mask Register enables/disables the corresponding interrupt source. A high (one) will enable the associated interrupt source. A low (zero) will mask (disable) the associated interrupt source. Even if the interrupt is masked the associated status register bit will still indicate whether or not an interrupt is pending from each source. However a masked interrupt will not cause an interrupt signal to be generated to the GPIO pin it is associated with. Modifying the Mask Register to enable an interrupt that is pending will immediately cause an interrupt to be generated.

This register is implemented as a set register and a clear register. To set a bit, the set address is used, writing a 1 to the desired bit. To clear a bit, the clear address is used, writing a 1 to the desired bit.

| NAME                         |     | Interrupt Mask Register |             |               |                |               |                    |              |     |     |     |     |             |                    |            |             |

|------------------------------|-----|-------------------------|-------------|---------------|----------------|---------------|--------------------|--------------|-----|-----|-----|-----|-------------|--------------------|------------|-------------|

| BIT                          | 15  | 14                      | 13          | 12            | 11             | 10            | 9                  | 8            | 7   | 6   | 5   | 4   | 3           | 2                  | 1          | 0           |

| MASKED<br>INTERRUPT<br>FEILD | RES | CE_<br>INT2             | CE_<br>INT1 | SYNTH_<br>IRQ | XUART_<br>INTB | XUART<br>ĪNTA | OTG_<br>FS_<br>INT | ENET_<br>INT | RES | RES | RES | RES | FSH_<br>OVR | OTG_<br>FS_<br>OVR | PB_<br>IRQ | LOW_<br>BAT |

| OPER                         | R/W | R/W                     | R/W         | R/W           | R/W            | R/W           | R/W                | R/W          | R/W | R/W | R/W | R/W | R/W         | R/W                | R/W        | R/W         |

| RESET                        | 0   | 0                       | 0           | 0             | 0              | 0             | 0                  | 0            | 0   | 0   | 0   | 0   | 0           | 0                  | 0          | 0           |

# 1.10.3 GPIO Interrupt Grouping and Non Registered Interrupts

Some interrupt signals are not associated with any CPLD register but are instead directly routed (inside the CPLD) to a GPIO pin. The SD and Memory Stick detect functions are logically ORed together since only one or the other should be implemented at any given time.

The interrupt are grouped in the following way:

| GPIO    | Interrupt sources                                                                                                  |

|---------|--------------------------------------------------------------------------------------------------------------------|

| GPIO1_1 | SD1_DET + MS1_DET                                                                                                  |

| GPIO1_2 | SD2_DET + MS2_DET                                                                                                  |

| GPIO1_3 | PRI_INT (ATLAS)                                                                                                    |

| GPIO1_4 | XUART_INTA, XUART_INTB, ENET_INT, LOW_BAT, PB_IRQ, OTG_FS_OVR,<br>OTG_FS_INT, FSH_OVR, SYNTH_IRQ, CE_INT1, CE_INT2 |

|         |                                                                                                                    |

|         |                                                                                                                    |

#### Table 23 GPIO Interrupt Bit Descriptions

| Name    | Description                                | Settings                    |

|---------|--------------------------------------------|-----------------------------|

| GPIO1_1 | SD1 OR MS1 memory card detect status       | 0 – No Card is inserted     |

|         |                                            | 1- A card has been detected |

| GPIO1_2 | SD2 OR MS2 memory card detect status       | 0 – No Card is inserted     |

|         |                                            | 1- A card has been detected |

| GPIO1_3 | Atlas' Primary Interrupt output status bit | 0 – No interrupt pending    |

|         |                                            | 1- Interrupt active         |

| GPIO1_4 | Registered Interrupt Status bit            | 0 – No interrupt pending    |

|         |                                            | 1- Interrupt active         |

Peripheral Bus Control

# **1.14 References**

[1] ZAS peripheral Bus Control CPLD, November 30, 2004, Version 2.0, Freescale Semiconductor.

[2] CS8900A ISA Ethernet Controller Data Sheet, April 2001, Cirrus Logic.

[3] SC16C652 Dual UART Controller, June 20, 2003, Rev 04, Philips Semiconductors.

[4] ISA System Architecture, October 1993, Mindshare, In