This document describes the differences between masks of the DSP56309: the 0J17D and the mask immediately preceding it, 5H80G. The 0J17D mask of the DSP56309 uses the communications design rules (CDR2) process. The 0J17D mask set also has new I/O and a new PLL, with the requisite change in the PLL capacitor equation (PCAP).

## **CONTENTS**

| 1 | PLL Input Capacitor      |   |

|---|--------------------------|---|

| 2 | ESD Protection           |   |

| 3 | Differences Overview     |   |

| 1 | Identification Registers |   |

| 5 | Errata Removal           |   |

| 3 | Documentation Errata     | 1 |

# 1 PLL Input Capacitor

The process change results in a changed requirement for computing the size of C<sub>PCAP</sub> the capacitor used with the PCAP input. **Table 1** lists the new formulas for computing the value of this input capacitor for the DSP.

## 2 ESD Protection

The 0J17D mask set incorporates improved I/O structures to ensure Electro Static Discharge (ESD) protection to Freescale's MC qualification levels of 2000 volts Human Body Model (HBM) and 200 volts Machine Model (MM).

## 3 Differences Overview

The primary functional differences between the masks are due to inherent differences between the two design technologies. **Table 1** compares the mask sets.

| Feature                                        | 5H80G                                                                                                                            | (80 MHz)                        |                                 | 0J17D (100 MHz)                                                                                                                                 |                                 |                                  |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------------------------|

|                                                | Recommended                                                                                                                      | Min                             | Max                             | Recommended                                                                                                                                     | Min                             | Max                              |

| Technology                                     | 0.5 micron                                                                                                                       | 1                               | -                               | Sub 0.4 micron                                                                                                                                  | 1                               | _                                |

| PLL input<br>capacitor<br>(C <sub>PCAP</sub> ) | Uses the following rules: For MF $\leq$ 4: $C_{PCAP} = [(500 \times MF) - 150] pF$ For MF $>$ 4: $C_{PCAP} = (690 \times MF) pF$ | (MF × 425)<br>- 125<br>MF × 520 | (MF × 590)<br>- 175<br>MF × 920 | Use the following rules:<br>For MF $\leq$ 4:<br>$C_{PCAP} = [(680 \times MF) - 120] pF$<br>For MF $>$ 4:<br>$C_{PCAP} = (1100 \times MF)$<br>pF | (MF × 580)<br>- 100<br>MF × 830 | (MF × 780)<br>- 140<br>MF × 1470 |

Table 1. Functional Comparison of 5H80G and 0J17D

Key differences between the masks are as follows:

- Target operating frequency for the 0J17D mask set is 100 MHz full voltage range (3.0–3.6 V). The preceding 5H80G mask set was 80 MHz full voltage range (3.0–3.6 V) and 100 MHz with de-rated operating voltage (3.125–3.6 V).

- On the 0J17D mask set, the peripheral I/O are 5 V tolerant without keepers. The preceding 5H80G mask set did not have 5 V tolerant I/O and had keepers.

- The J17D mask set has split voltage supply between core and I/O supplies.

- Pull-up was removed from the TCK pin in order to make the DSP56309 consistent with the DSP563xx family. The preceding 5H80G mask set had a pull-up on the TCK pin

# 4 Identification Registers

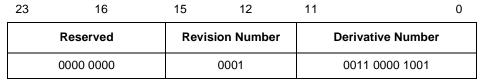

Values in the Device Identification register (IDR) and JTAG Identification (ID) register are changed to reflect the new 0J17D mask set, as shown in **Figure 1** and **Figure 2**. The IDR is a 24-bit, read-only factory-programmed register that identifies DSP56300 family members. It specifies the derivative number and revision number of the device. This information is used in testing or by software. **Figure 1** shows the contents of the IDR for mask set 0J17D. Revision numbers are assigned as follows: \$0 is revision 0, \$1 is revision A, and so on.

Figure 1. Identification Register Configuration (Revision 3)

The JTAG ID register is a 32-bit read-only factory-programmed register that distinguishes the component on a board according to the IEEE 1149.1 standard. **Figure 2** shows the JTAG ID register configuration for mask set 0J17D. Version information corresponds to the revision number (\$0 for revision 0, \$1 for revision A, and so forth).

Functional Differences Between Masks 5H80G and 0J17D of the DSP56309, Rev. 3

| 31          | 28        | 27 | 22                   | 21 | 12                | 11  | 1                     | 0 |

|-------------|-----------|----|----------------------|----|-------------------|-----|-----------------------|---|

| Version Inf | formation |    | tomer Part<br>lumber |    | equence<br>Number |     | nufacturer<br>dentity | 1 |

| 000         | 01        | (  | 000110               | 00 | 00001001          | 000 | 0000 1110             | 1 |

Figure 2. JTAG Identification Register Configuration (Revision 3)

## 5 Errata Removal

The 0J17D mask set removes all known functional errata on the 5H80G mask set. This section shows the functional errata that the 0J17D mask set removes. For further documentation updates, consult the errata for each device. The specific differences in errata items are listed in the following tables. A detailed description of each errata item is available in the chip errata documents on the web site listed on the back cover of this document.

The silicon errata present on the 5H80G mask but not on the 0J17D masks are listed as follows:

| Errata<br>Number | Errata Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Status               |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| ES33             | Description (added 3/3/1997):  When using the JTAG instructions SAMPLE/PRELOAD, EXTEST, and CLAMP, erroneous data may be driven out on the parallel pins and TDO. Data cannot be shifted through the Boundary Scan Register (BSR) using the SAMPLE/PRELOAD instruction. Because the BSR must be preloaded using the SAMPLE/PRELOAD instruction, the EXTEST and CLAMP instructions cannot be used for testing the board connections.  Workaround: None available.                                                                                                                                                                                                          | Fixed<br>on<br>QJ17D |

| ES42             | Description (added 2/27/1998):  When a DMA channel is in Line mode (that is, DTM = 010) with address modes defined by D3D = 0 and DMA = 10010x (that is, DCO in A mode), and the DCO value is greater than \$FFF, then the DMA does not function properly. This address mode implies "no update" at the destination and "no update" or "post increment by 1" mode at the source.  Workaround:  Use Block Transfer mode (that is, DTM = 000). For the DCO and DAM settings described in this erratum, the Line Transfer mode of DMA is identical to its Block Transfer mode, so this combination is redundant. In fact, a block containing only one line is still a block. | Fixed<br>on<br>0J17D |

Functional Differences Between Masks 5H80G and 0J17D of the DSP56309, Rev. 3

| Errata<br>Number | Errata Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Status      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|                  | Description (added 9/25/1997):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Fixed       |

|                  | Using the JTAG instruction code 1111 (\$F) or 1101 (\$D) for the BYPASS instruction may cause the chip to enter Debug mode (which then correctly sets the Status bits (OS[1:0]) in the OnCE Status and Control Register (OSCR[7:6]) and asserts the $\overline{\rm DE}$ output to acknowledge Debug mode status).                                                                                                                                                                                                                                                  | on<br>0J17D |

|                  | Workaround: Use one of the following alternatives:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |

| ES53             | • If possible, do not use instruction code 1111 (\$F) or 1101 (\$D) for the BYPASS instruction. Use one of the other defined BYPASS instruction codes (that is, any code from 1000–1100 (\$8–\$C) or 1110 (\$E)).                                                                                                                                                                                                                                                                                                                                                  |             |

|                  | <ul> <li>If you must use instruction code 1111 (\$F) or 1101 (\$D), use the following procedure:</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |

|                  | <ul> <li>— While the \$F or \$D instruction code is in the Instruction Register, ensure that the JTAG Test Access Port (TAP) state machine does not pass through the JTAG Test-Logic-Reset state while accessing any JTAG registers (that is, Instruction Register, Boundary Scan Register, or ID Register).</li> <li>— Before using any other JTAG instruction, load one of the other BYPASS instruction codes (that is, any code from 1000–1100 (\$8–\$C) or 1110 (\$E)) into the instruction register. Then, any other JTAG instruction may be used.</li> </ul> |             |

|                  | Description (added 2/27/1998):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Fixed       |

|                  | When a DMA channel is configured to use its DMA Control Register (DCR) in the following way:                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | on<br>0J17D |

|                  | • Line Transfer mode is selected (that is, DTM[2:0] = 010).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |

|                  | • Non-three-dimensional Address mode is selected (that is, $\mathrm{D3D}=0$ ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |

| ES54             | <ul> <li>Destination Address Offset Register DOR1 or DOR2 is selected<br/>(that is, DAM[5:3] = 001 or 011).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |

|                  | • No Source Address Offset is selected (that is, DAM[2:0] = 100 or 101).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

|                  | then DMA transfers do not occur as intended.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |

|                  | Workaround:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |

|                  | Select Destination Address Offset Register DOR0 or DOR2 by setting $DAM[5:3] = 000$ or 010.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |

| Errata<br>Number | Errata Description                                                                                                                                                                                                                                                                                                                                                                          | Status               |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| ES77             | Description (added 2/27/98):  The PCAP pin of the H80G is marginal to Freescale's XC qualification requirement of 1K Volt Human Body Model ElectroStatic Discharge (ESD) and 100V Machine Model ESD.                                                                                                                                                                                        | Fixed<br>on<br>0J17D |

|                  | Workaround: Minimize PCAP exposure to ElectroStatic Discharge.                                                                                                                                                                                                                                                                                                                              |                      |

| ES78             | Description (added 2/27/98):  When the SCI is configured in Synchronous mode, if the internal clock and all SCI pins are enabled simultaneously, then an extra pulse of 1 DSP clock-length is provided on the SCLK pin.  Workaround:  Do both these steps in this order:  a. Enable an SCI pin other than SCLK.  b. In the next instruction, enable the remaining SCI pins, including SCLK. | Fixed<br>on<br>0J17D |

| ES79             | Description (added 2/27/1998):  When activity passes from one DMA channel to another and the DMA interface accesses external memory, requiring one or more wait states, the DACT and DCH status bits in the DMA Status Register (DSTR) may indicate improper activity status for DMA Channel 0 (that is, DACT = 1 and DCH[2:0] = 000).  Workaround: none                                    | Fixed<br>on<br>0J17D |

| Errata<br>Number | Errata Description                                                                                                                                                                                                                                                           | Status      |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|                  | Description (added 5/13/98):                                                                                                                                                                                                                                                 | Fixed       |

|                  | When software disables a DMA channel (by clearing the DE bit of the DCR), the DTD status bit of the channel may not be set if any of the following events occur:                                                                                                             | on<br>0J17D |

|                  | a. Software disables the DMA channel just before a conditional transfer stall (Described by App B-3.5.1,UM).                                                                                                                                                                 |             |

|                  | <ul> <li>Software disables the DMA channel at the end of the block<br/>transfer (that is after the counter is loaded with its initial value<br/>and transfer of the last word of the block is completed).</li> </ul>                                                         |             |

|                  | As a result, the Transfer Done interrupt might not be generated.                                                                                                                                                                                                             |             |

|                  | Workaround: Avoid using the instruction sequence causing the conditional transfer stall (See DSP56300 UM, App B-3.5.1 for description) in fast interrupt service routines. Every time the DMA channel needs to be disabled by software, the following sequence must be used: |             |

| ES84             | <pre>bclr #DIE,x:M_DCR ; not needed if DIE is cleared bclr #DE,x:M_DCR ; instead of two instructions above, one 'movep' instruction ; may be used ; to clear DIE and DE bits     movep #DCR_Dummy_Value,x:M_DCR     bclr #DE,x:M_DCR     nop     nop</pre>                   |             |

|                  | Here, the DCR_Dummy_value is any value of the DCR register that complies with the following requirements:                                                                                                                                                                    |             |

|                  | <ul> <li>DE is set;</li> <li>DIE is set if Transfer Done interrupt request should be generated and cleared otherwise;</li> <li>DRS[4:0] bits must encode a reserved DMA request source (see the following list of reserved DRS values);</li> </ul>                           |             |

|                  | List of reserved DRS[4:0] values (per device):                                                                                                                                                                                                                               |             |

|                  | <ul> <li>DSP56302, DSP56309, DSP56303, DSP56306, DSP56362 —         <sup>10101-11111</sup></li> <li>DSP56305 — 11011</li> <li>DSP56301 — 10011-11011</li> <li>DSP56307 — 10111-11111</li> </ul>                                                                              |             |

| Errata<br>Number | Errata Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Status               |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| ES85             | Description (added 5/3/98):  If both the DMA channel and the core simultaneously access the same 1/4K page of internal memory (X, Y, or program), an improper DMA channel operation may occur.  Workaround:  Avoid simultaneous DMA and core accesses to the same 1/4K page of internal memory.                                                                                                                                                                                                                                                                                                                                                                 | Fixed<br>on<br>0J17D |

| ES89             | Description (added 6/25/98):  If the SCI Receiver is programmed to work with a different serial clock than the SCI Transmitter so that either the Receiver or Transmitter is using the external serial clock and the other is using the internally-generated serial clock—RCM and TCM in the SCCR are programmed differently)—then the internal serial clock generator will not operate and the SCI portion (Receiver or Transmitter) clocked by the internal clock will be stuck.  Workaround:  Do not use SCI with the two SCI portions (Receiver and Transmitter) clocked by different serial clocks; use either both externally or both internally clocked. | Fixed<br>on<br>0J17D |

|                  | Or: When using both portions of the SCI (Receiver & Transmitter), do not program different values on RCM and TCM in the SCCR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |

| a Rem            | oval                                                                          |

|------------------|-------------------------------------------------------------------------------|

| Errata<br>Number | Errata Description                                                            |

|                  | Description (added 6/25/98)/Modified 4/19/99:                                 |

|                  | A deadlock occurs during DMA transfers if all the following conditions exist: |

| Number |                                                                                                                                                                                                                                                         |             |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|        | Description (added 6/25/98)/Modified 4/19/99:                                                                                                                                                                                                           | Fixed       |

|        | A deadlock occurs during DMA transfers if all the following conditions exist:                                                                                                                                                                           | on<br>0J17D |

|        | 1. DMA transfers data between internal memory and external memory through port A.                                                                                                                                                                       |             |

|        | 2. DMA and the core access the same internal 0.25K memory module.                                                                                                                                                                                       |             |

|        | 3. One of the following occurs:                                                                                                                                                                                                                         |             |

|        | a. The bus arbitration system is active, that is, $\overline{BG}$ is changing, not tied to ground.                                                                                                                                                      |             |

| ES90   | b. Packing mode (bit 7 in the AAR[3 - 0] registers) is active for DMA transfers on Port A.                                                                                                                                                              |             |

|        | Workaround:                                                                                                                                                                                                                                             |             |

|        | One of the following, but workarounds 2, and 3 are valid ONLY to section 3 a of the errata - that is, not valid if packing mode is used, and workaround 4 is valid only to section 3 b of the errata - that is, not valid if bus arbitration is active. |             |

|        | 1. Use intermediate internal memory on which there is no contention with the core.                                                                                                                                                                      |             |

|        | 2. Tie $\overline{BG}$ to ground, or have an external arbiter that asserts $\overline{BG}$ even if BR is not asserted.                                                                                                                                  |             |

|        | 3. Set the BCR[BRH] bit, whenever BR must be active.                                                                                                                                                                                                    |             |

|        | 4. Avoid using packing mode.                                                                                                                                                                                                                            |             |

Status

| Errata<br>Number | Errata Description                                                                                                                                                                                                                                                                                              | Status      |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|                  | Description (added 7/22/98):                                                                                                                                                                                                                                                                                    | Fixed       |

|                  | If the Core reads data from the HRX while instructions are fetched from the memory Expansion Port (Port A) using 2 or more wait states, data may be lost.                                                                                                                                                       | on<br>0J17D |

|                  | Workaround :                                                                                                                                                                                                                                                                                                    |             |

|                  | There are three possible workarounds:                                                                                                                                                                                                                                                                           |             |

|                  | 1) The host should guarantee that there is no more than one word in the TXH:TXM:TXL-HRX data path at any time. This can be achieved if the host writes a word to the HI08 only when the TRDY flag is set (that is, the data path is empty).                                                                     |             |

|                  | 2) Use a service routine running from fast (that is, one wait state) external memory or internal memory to read the HRX read code; ensure that code that is fetched from slow (that is, more than 1 wait state) external memory is located at least 4 instructions after the HRX register is read. For example: |             |

| ES91             | READ_HRX_DATA NOP NOP NOP NOP                                                                                                                                                                                                                                                                                   |             |

|                  | Note:                                                                                                                                                                                                                                                                                                           |             |

|                  | a) Interrupt requests that fetch instructions from slow external memory should be masked during this service routine.  Nonmaskable interrupt (NMI) request routines must not be in external memory.                                                                                                             |             |

|                  | b) If running from fast external memory and if a DMA channel accessing external memory is used, then the DMA may cause extra wait states to the core. Thus, the DMA should have a lower priority than the core so that the core can access the external memory with no more than 1 wait state.                  |             |

|                  | 3) Read the HRX using one of the channels of the on-chip DMA controller.                                                                                                                                                                                                                                        |             |

| Errata<br>Number | Errata Description                                                                                                                                                                                                                                                                      | Status      |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|                  | Description (added 8/10/98):                                                                                                                                                                                                                                                            | Fixed       |

|                  | Enabling any DMA channel by software for transferring a block of data (TM=011 in the channel control register) might not work properly.                                                                                                                                                 | on<br>0J17D |

|                  | Workaround:                                                                                                                                                                                                                                                                             |             |

|                  | Triggering of a channel for block transfer by software can be replaced<br>by triggering of the DMA channel for block transfer by a peripheral<br>(e.g. Timer, SCI, and so forth) that is not used while the block of data<br>should be transferred by DMA. This can be done as follows: |             |

|                  | 1. Set the DSR, DDR and DCO registers of the DMA channel according to the application case.                                                                                                                                                                                             |             |

|                  | 2. Transfer mode of the DMA channel (in the DCR register) should be set to $TM=000$ or $TM=100$ (See Section 8.1.5.3, 563xx UM).                                                                                                                                                        |             |

| ES94             | 3. DMA Request Source of the DMA channel should be set according to the chosen peripheral, which should trigger the DMA channel (see Section 8.1.5.6 56300 UM and "DMA Request Sources" Table in the CORE CONFIGURATION item of the 563xx UM).                                          |             |

|                  | 4. All others fields of the DCR register, except the DE bit, should be set according to the application case.                                                                                                                                                                           |             |

|                  | 5. Configure the peripheral to assert its DMA request line;                                                                                                                                                                                                                             |             |

|                  | 6. Set DE bit of the DCR register.                                                                                                                                                                                                                                                      |             |

|                  | Example 1:                                                                                                                                                                                                                                                                              |             |

|                  | Assuming that the SCI is not used while the block of #DCO3 words is transferred by DMA channel 3, the SCI Transmit Data (TDRE = 1, DRS[4:0] = 01111) trigger can be used instead of a software trigger for channel 3.                                                                   |             |

|                  | 1. Initialize DMA channel registers                                                                                                                                                                                                                                                     |             |

|                  | <pre>movep #DSR3,x:M_DSR3 movep #DDR3,x:M_DDR3 movep #DCO3,x:M_DCO3 bset #0,x:M_PCRE</pre>                                                                                                                                                                                              |             |

|                  | Now when the DMA channel is enabled, a transfer of the block begins.                                                                                                                                                                                                                    |             |

| Errata<br>Number | Errata Description                                                                                                                                                                                             |             |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|                  | 2. Enable DMA channel                                                                                                                                                                                          | Fixed       |

|                  | <pre>movep #\$867a40,x:M_DCR3 ;; enable DMA channel 3,</pre>                                                                                                                                                   | on<br>0J17D |

|                  | Example 2 :                                                                                                                                                                                                    |             |

|                  | Assuming that Timer 0 is not used while a block of #DCO3 words is to be transferred by DMA channel 3, the Timer0 (TCF0 = 1, DRS[4:0] = 10000) trigger can be used instead of a software trigger for channel 3. |             |

|                  | 1. Initialize DMA channel registers                                                                                                                                                                            |             |

|                  | <pre>movep #DSR3,x:M_DSR3 movep #DDR3,x:M_DDR3</pre>                                                                                                                                                           |             |

|                  | movep #DCO3,x:M_DCO3                                                                                                                                                                                           |             |

| <b>ES94</b>      | 2. Initialize Timer 0                                                                                                                                                                                          |             |

| cont.            | <pre>movep #\$0,x:M_TCSR0 ;;no prescaling, inv=0, mode 0,</pre>                                                                                                                                                |             |

|                  | ;; no interrupt, reload is disabled                                                                                                                                                                            |             |

|                  | movep #\$0,x:M_TLR0 ;;initialize load reg. movep #\$0,x:M_TCPR0 ;;initialize compare reg.                                                                                                                      |             |

|                  | 3. Generate DMA channel trigger                                                                                                                                                                                |             |

|                  | - option 1                                                                                                                                                                                                     |             |

|                  | <pre>movep #\$A48254,x:M_DCR3 ;; enable DMA channel 3, block ;; transfer mode, DE isn't ;; disabled at end of ;; transfer, triggered by ;; Timer0 (TCF0=1)</pre>                                               |             |

|                  | <pre>bset #M_TE,x:M_TCSR0 ;; enable timer nop nop</pre>                                                                                                                                                        |             |

|                  | bclr #M_TE,x:M_TCSR0 ;; disable timer                                                                                                                                                                          |             |

| Errata<br>Number | Errata Description                                                                                                                                                                                                                                                                                                                                                              | Status     |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|                  | - option 2                                                                                                                                                                                                                                                                                                                                                                      | Fixed      |

|                  | movep #\$848254,x:M_DCR3 ;; enable DMA channel 3, block ;; transfer mode, DE is ;; disabled at the end of ;; the transfer, triggered by ;; Timer0 ;; (TCF0=1)                                                                                                                                                                                                                   | on<br>W17D |

|                  | <pre>bset #M_TE,x:M_TCSR0 ;; enable timer nop nop</pre>                                                                                                                                                                                                                                                                                                                         |            |

|                  | bclr #M_TE,x:M_TCSR0 ;; disable timer                                                                                                                                                                                                                                                                                                                                           |            |

|                  | - option 3                                                                                                                                                                                                                                                                                                                                                                      |            |

|                  | bset #M_TE,x:M_TCSR0 ;; enable timer                                                                                                                                                                                                                                                                                                                                            |            |

|                  | <pre>movep #\$848254,x:M_DCR3 ;; enable DMA channel 3, block transfer</pre>                                                                                                                                                                                                                                                                                                     |            |

|                  | ;; mode, DE is disabled at the                                                                                                                                                                                                                                                                                                                                                  |            |

|                  | end of ;; the transfer, triggered by                                                                                                                                                                                                                                                                                                                                            |            |

|                  | Timer0 ;; (TCF0=1)                                                                                                                                                                                                                                                                                                                                                              |            |

| ES94 cont.       | bclr #M_TE,x:M_TCSR0 ;; disable timer                                                                                                                                                                                                                                                                                                                                           |            |

| cont.            | Following are the differences between these three options:                                                                                                                                                                                                                                                                                                                      |            |

|                  | option 1 : The DMA channel should be enabled only for the first block transfer. An additional block transfers can be triggered by the following sequence:                                                                                                                                                                                                                       |            |

|                  | <pre>bset #M_TE,x:M_TCSR0 ;; enable timer nop nop</pre>                                                                                                                                                                                                                                                                                                                         |            |

|                  | bclr #M_TE,x:M_TCSR0 ;; disable timer                                                                                                                                                                                                                                                                                                                                           |            |

|                  | Note:                                                                                                                                                                                                                                                                                                                                                                           |            |

|                  | Execution of this sequence can be interrupted because the DMA channel is triggered after the TE bit of the TCSR0 register is set. The TE bit must be cleared no later than 33554430 DSP clock cycles after it is set. Otherwise, an undesirable trigger for the DMA channel is generated. The DMA channel must be disabled every time when Timer 0 is used for another purpose. |            |

|                  | option 2 : The whole sequence must be used every time when a block transfer is to be triggered.                                                                                                                                                                                                                                                                                 |            |

| Errata<br>Number | Errata Description                                                                                                                                                                                                                                                                               |                      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|                  | Note:  Execution of this sequence may be interrupted because the DMA channel is triggered after the TE bit of the TCSR0 register is set. The TE bit must be cleared no later than 33554430 DSP clock cycles after is is set. Otherwise, an undesirable trigger for the DMA channel is generated. | Fixed<br>on<br>0J17D |

| ES94<br>cont.    | option 3: The whole sequence must be used every time a block transfer is to be triggered.                                                                                                                                                                                                        |                      |

| cont.            | Note: Execution of the first two instructions of the sequence must be uninterruptable. The TE bit of the TCSR0 register must be cleared no later than 33554430 DSP clock cycles after it is set. Otherwise, an undesirable trigger for the DMA channel is generated.                             |                      |

|                  | Another peripheral can be used for this purpose, but taking into consideration its specific features.                                                                                                                                                                                            |                      |

|                  | Description (added 8/15/98):                                                                                                                                                                                                                                                                     | Fixed                |

| ES95             | If more than a single DMA channel is enabled while the DSP stays in the WAIT processing state, and triggering one of the DMA channels causes an exit from the WAIT state (See A-6.115, UM), triggering another DMA channel might cause improper DMA operation.                                   | on<br>0J17D          |

| E393             | Workaround:                                                                                                                                                                                                                                                                                      |                      |

|                  | Assure that only a single DMA channel can be triggered during DSP WAIT state. If the application cannot guarantee this, other DMA channels should be disabled before the WAIT processing state is entered and then reenabled after WAIT state is exited.                                         |                      |

|                  | Description (added 10/22/98):                                                                                                                                                                                                                                                                    | Fixed                |

| ES100            | The VDD requirements for 100 MHz operation are VDD min = $3.15$ volts and VDD max = $3.6$ volts.                                                                                                                                                                                                 | on<br>0J17D          |

| E3100            | Workaround:                                                                                                                                                                                                                                                                                      |                      |

|                  | Ensure that the VDD supply value is within the specified voltage range requirements.                                                                                                                                                                                                             |                      |

| Errata<br>Number | Errata Description                                                                                                                                                                                                                                                                                                                                           |             |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|                  | Description (added 10/26/98):                                                                                                                                                                                                                                                                                                                                | Fixed       |

|                  | If the reset mode is expanded mode (for example, mode 0 or mode 8 on the DSP5630x), A MOVE (not a PROGRAM FETCH) from internal P memory to any destination may not work properly.                                                                                                                                                                            | on<br>0J17D |

| ES101            | Workaround: After each reset (RESET) negation and before the first move from internal program memory, execute the following sequence:                                                                                                                                                                                                                        |             |

|                  | BSET #M_CE,sr<br>NOP<br>NOP<br>NOP<br>BCLR #M_CE,sr                                                                                                                                                                                                                                                                                                          |             |

|                  | Description (added 11/20/98):                                                                                                                                                                                                                                                                                                                                | Fixed       |

|                  | An improper operation may occur when a DMA channel uses the following transfer modes:                                                                                                                                                                                                                                                                        | on<br>0J17D |

|                  | • $DTM(2:0) = 100$                                                                                                                                                                                                                                                                                                                                           |             |

|                  | • $DTM(2:0) = 101$                                                                                                                                                                                                                                                                                                                                           |             |

| ES104            | where the DE bit is not automatically cleared at the end of block and the DMA channel is disabled by software (DE bit is cleared) while it is triggered for a new transfer.                                                                                                                                                                                  |             |

| E3104            | Workaround: The DMA channel should be disabled only when it cannot be triggered by a new transfer. Use one of the following alternatives:                                                                                                                                                                                                                    |             |

|                  | 1. The system configuration must guarantee that no DMA trigger can occur while the DE bit is cleared.                                                                                                                                                                                                                                                        |             |

|                  | 2.The following sequence disables the DMA channel:                                                                                                                                                                                                                                                                                                           |             |

|                  | a/ Wait until the DTD bit is cleared                                                                                                                                                                                                                                                                                                                         |             |

|                  | b/ Clear the DE bit<br>c/ Wait until the DTD bit is set                                                                                                                                                                                                                                                                                                      |             |

|                  | Description (added 12/12/98):                                                                                                                                                                                                                                                                                                                                | Fixed       |

| ES108            | The Timer's TIOx pin does not function properly in WatchDog mode while the $\overline{\text{RESET}}$ pin is asserted. The TIOx pin is tri-stated immediately after $\overline{\text{RESET}}$ assertion; it should be driven for 2.5 internal clock cycles according to the specification (section 9.4.4.1 and 9.4.4.2 of the $DSP56303$ $User's$ $Manual$ ). | on<br>W17D  |

|                  | Workaround:                                                                                                                                                                                                                                                                                                                                                  |             |

|                  | Provide external logic in order to extend the TIOx pin assertion.                                                                                                                                                                                                                                                                                            |             |

| Errata<br>Number | Errata Description                                                                                                                                                                                                                                                                                                                                                                             |                      |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|                  | Description (added 4/19/99, revised 4/30/99):  A DMA channel may operate improperly when the address mode of this channel is defined as three-dimensional (D3D=1) and DAM[5:0]                                                                                                                                                                                                                 | Fixed<br>on<br>0J17D |

| ES114            | = 1xx 1 10 or DAM[5:0] = 01xx 10 (that is, triple counter mode is E).  Workaround:                                                                                                                                                                                                                                                                                                             |                      |

|                  | Use the triple counter modes C(DAM[1:0]=00) or D(DAM[1:0]=01) instead of the E(DAM[1:0]=10) mode.                                                                                                                                                                                                                                                                                              |                      |

|                  | Description (added 4/19/99):                                                                                                                                                                                                                                                                                                                                                                   | Fixed                |

|                  | When a DMA channel (called channel A) is disabled by software clearing the channel's DCR[DE] bit, the DTD bit may not get set, and the DMA end of the block interrupt may not happen if one of the following occurs:                                                                                                                                                                           | on<br>0J17D          |

|                  | 1. There is another channel (channel B) executing EXTERNAL accesses, and the DE bit of channel A is being cleared by software at the end of the channel B word transfer - if channel B is in Word transfer mode, or at the end of the channel B line transfer - if channel B is in Line Transfer mode, or at the end of the channel B block transfer - if channel B is in Block transfer mode. |                      |

| ES115            | 2. This channel (A) is executing EXTERNAL accesses, and the DE bit of this channel (A) is being cleared by software at the end of the channel B word transfer - if channel B is in Word transfer mode, or at the end of the channel B line transfer - if channel B is in Line transfer mode.                                                                                                   |                      |

|                  | Workaround:                                                                                                                                                                                                                                                                                                                                                                                    |                      |

|                  | Avoid executing a DMA external access when any DMA channel should be disabled. This can be done as follows. Every time the DMA channel needs to be disabled by software, the following sequence must be used:                                                                                                                                                                                  |                      |

|                  | ;; initialize an unused DMA channel "C"  movep  #DSR_swflag, x:M_DSRC ;; here DSR_swflag is an ;; unused X, Y or P                                                                                                                                                                                                                                                                             |                      |

|                  | memory ;; location, should ;; be initialized to ;; \$800000                                                                                                                                                                                                                                                                                                                                    |                      |

|                  | ;; M_DSRC - address of                                                                                                                                                                                                                                                                                                                                                                         |                      |

|                  | the ;; channel C DSR                                                                                                                                                                                                                                                                                                                                                                           |                      |

|                  | register.                                                                                                                                                                                                                                                                                                                                                                                      |                      |

#### a Removal

| Errata<br>Number | Errata Description                                                                                             | Status               |

|------------------|----------------------------------------------------------------------------------------------------------------|----------------------|

|                  | <pre>movep #DDR_swflag, x:M_DDRC ;; DDR_swflag is an unused</pre>                                              | Fixed<br>on<br>0J17D |

|                  | movep #TR_LENGTH, x:M_DCOC ;; see below the definition ;; of the TR_LENGTH                                     |                      |

|                  | value, ;; M_DCOC - address ;; of the channel C DCO                                                             |                      |

| ES115<br>cont.   | register .movep #1f0240, x:M_DCRC;; M_DCRB - address of the ;; channel C DCR register.  :: Set transfer mode - |                      |

|                  | <pre>;; block transfer, ;; triggered by ;; software highest ;; priority, continuous ;; mode on no-update</pre> |                      |

|                  | ;; source and destination ;; address mode X memory ;; location for source ;; and destination (can              |                      |

|                  | be ;; chosen by ;; user accordingly to ;;                                                                      |                      |

|                  | DSR_swflag/DDR_swflag)                                                                                         |                      |

| Errata<br>Number | Errata Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|