# **Freescale Semiconductor**

Data Sheet: Technical Data

Document Number: MSC8156E Rev. 5, 07/2013

# Six-Core Digital Signal Processor with Security

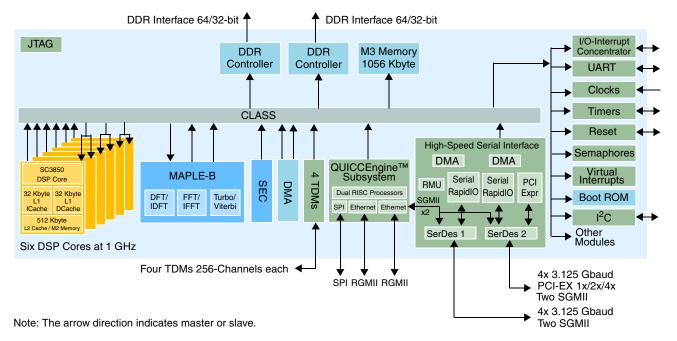

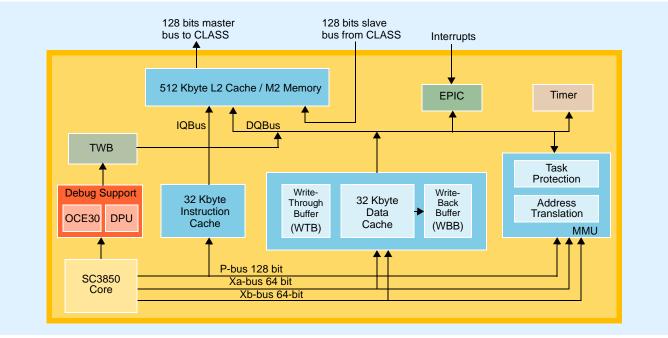

- Six StarCore SC3850 DSP subsystems, each with an SC3850 DSP core, 32 Kbyte L1 instruction cache, 32 Kbyte L1 data cache, unified 512 Kbyte L2 cache configurable as M2 memory in 64 Kbyte increments, memory management unit (MMU), extended programmable interrupt controller (EPIC), two general-purpose 32-bit timers, debug and profiling support, low-power Wait, Stop, and power-down processing modes, and ECC/EDC support.

- Chip-level arbitration and switching system (CLASS) that provides full fabric non-blocking arbitration between the cores and other initiators and the M2 memory, shared M3 memory, DDR SRAM controllers, device configuration control and status registers, MAPLE-B, and other targets.

- 1056 Kbyte 128-bit wide M3 memory, 1024 Kbytes of which can be turned off to save power.

- 96 Kbyte boot ROM.

- Three input clocks (one global and two differential).

- Five PLLs (three global and two Serial RapidIO PLLs).

- Multi-Accelerator Platform Engine for Baseband (MAPLE-B) with a programmable system interface, Turbo decoding, Viterbi decoding, and FFT/iFFT and DFT/iDFT processing. MAPLE-B can be disabled when not required to reduce overall power consumption.

- Security Engine (SEC) optimized to process all the algorithms associated with IPSec, IKE, SSL/TLS, 3GPP, and LTE using 4 crypto-channels with multi-command descriptor chains, integrated controller for assignment of the eight execution units (PKEU, DEU, AESU, AFEU, MDEU, KEU, SNOW, and the random number generator (RNG), and XOR engine to accelerate parity checking for RAID storage applications.

- Two DDR controllers with up to a 400 MHz clock (800 MHz data rate), 64/32 bit data bus, supporting up to a total 2 Gbyte in up to four banks (two per controller) and support for DDR2 and DDR3.

- DMA controller with 32 unidirectional channels supporting 16 memory-to-memory channels with up to 1024 buffer descriptors per channel, and programmable priority, buffer, and multiplexing configuration. It is optimized for DDR SDRAM.

- Up to four independent TDM modules with programmable word size (2, 4, 8, or 16-bit), hardware-base A-law/µ-law conversion, up to 62.5 Mbps data rate for each TDM link, and with glueless

**MSC8156E**

FC-PBGA-783 29 mm × 29 mm

interface to E1 or T1 framers that can interface with H-MVIP/H.110 devices, TSI, and codecs such as AC-97.

- High-speed serial interface that supports two Serial RapidIO interfaces, one PCI Express interface, and two SGMII interfaces (multiplexed). The Serial RapidIO interfaces support 1x/4x operation up to 3.125 Gbaud with a single messaging unit and two DMA units. The PCI Express controller supports 32- and 64-bit addressing, x4, x2, and x1 link.

- QUICC Engine technology subsystem with dual RISC processors, 48 Kbyte multi-master RAM, 48 Kbyte instruction RAM, supporting two communication controllers for two Gigabit Ethernet interfaces (RGMII or SGMII), to offload scheduling tasks from the DSP cores, and an SPI.

- I/O Interrupt Concentrator consolidates all chip maskable interrupt and non-maskable interrupt sources and routes then to <u>INT\_OUT</u>, <u>NMI\_OUT</u>, and the cores.

- UART that permits full-duplex operation with a bit rate of up to 6.25 Mbps.

- Two general-purpose 32-bit timers for RTOS support per SC3850 core, four timer modules with four 16-bit fully programmable timers, and eight software watchdog timers (SWT).

- Eight programmable hardware semaphores.

- Up to 32 virtual interrupts and a virtual NMI asserted by simple write access.

- I<sup>2</sup>C interface.

- Up to 32 GPIO ports, sixteen of which can be configured as external interrupts.

- Boot interface options include Ethernet, Serial RapidIO interface, I<sup>2</sup>C, and SPI.

- Supports standard JTAG interface

- Low power CMOS design, with low-power standby and power-down modes, and optimized power-management circuitry.

- 45 nm SOI CMOS technology.

© 2008–2013 Freescale Semiconductor, Inc. All rights reserved.

Freescale reserves the right to change the detail specifications as may be required

to permit improvements in the design of its products.

# **Table of Contents**

| Pin A | ssignment                                                                                                                               |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 1.1   | FC-PBGA Ball Layout Diagram4                                                                                                            |

| 1.2   | Signal List By Ball Location5                                                                                                           |

| Elect | rical Characteristics                                                                                                                   |

| 2.1   | Maximum Ratings                                                                                                                         |

| 2.2   | Recommended Operating Conditions                                                                                                        |

| 2.3   | Thermal Characteristics                                                                                                                 |

| 2.4   | CLKIN Requirements                                                                                                                      |

| 2.5   | DC Electrical Characteristics                                                                                                           |

| 2.6   | AC Timing Characteristics                                                                                                               |

| Hard  | ware Design Considerations55                                                                                                            |

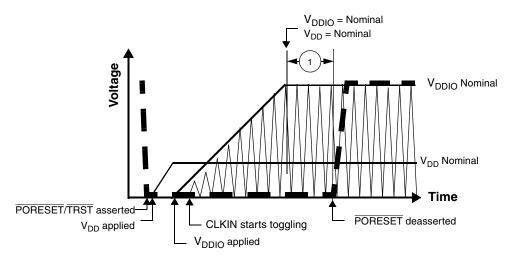

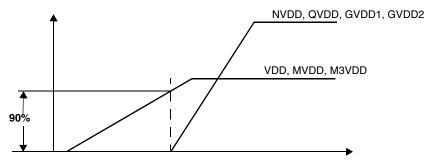

| 3.1   | Power Supply Ramp-Up Sequence                                                                                                           |

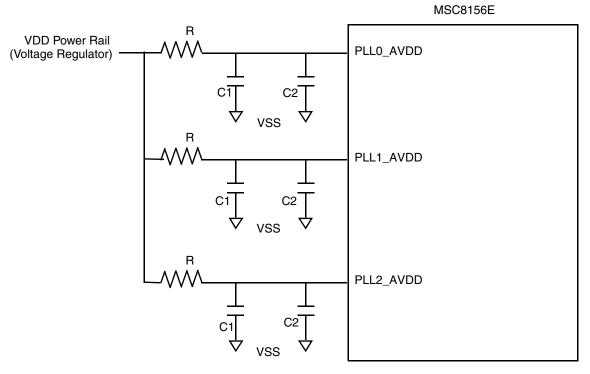

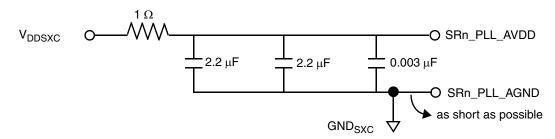

| 3.2   | PLL Power Supply Design Considerations                                                                                                  |

| 3.3   | Clock and Timing Signal Board Layout Considerations 59                                                                                  |

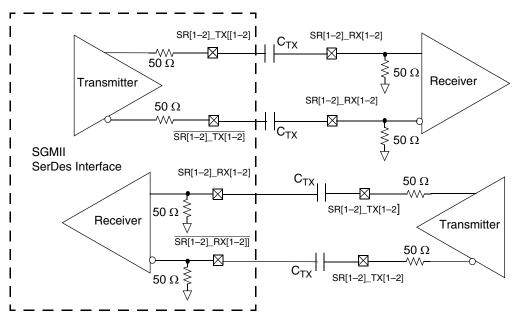

| 3.4   | SGMII AC-Coupled Serial Link Connection Example59                                                                                       |

| 3.5   | Connectivity Guidelines                                                                                                                 |

| 3.6   | Guide to Selecting Connections for Remote Power                                                                                         |

|       | Supply Sensing                                                                                                                          |

| Orde  | ring Information                                                                                                                        |

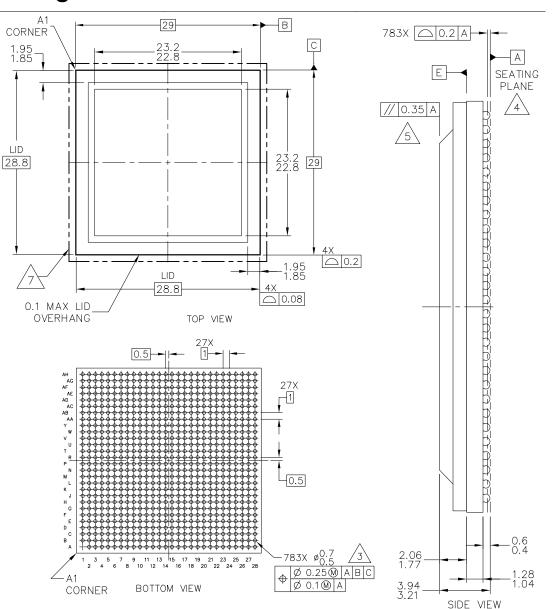

| Pack  | age Information                                                                                                                         |

| Prod  | uct Documentation                                                                                                                       |

| Revis | sion History                                                                                                                            |

|       | 1.1<br>1.2<br>Elect<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>Hard<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>Orde<br>Pack<br>Prod |

# List of Figures

NP

| Figure 1. | MSC8156E Block Diagram 3                              |

|-----------|-------------------------------------------------------|

| Figure 2. | StarCore SC3850 DSP Subsystem Block Diagram 3         |

| Figure 3. | MSC8156E FC-PBGA Package, Top View 4                  |

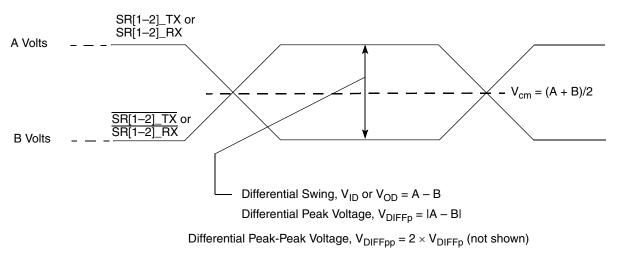

| Figure 4. | Differential Voltage Definitions for Transmitter or   |

|           | Receiver                                              |

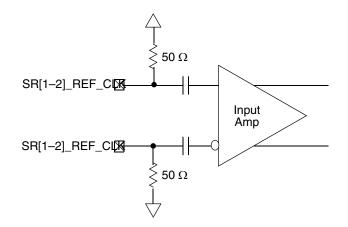

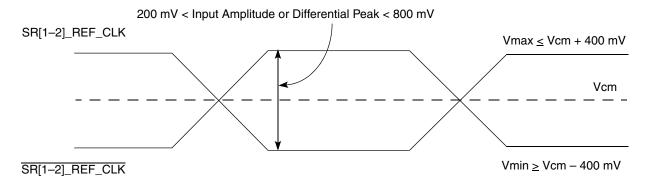

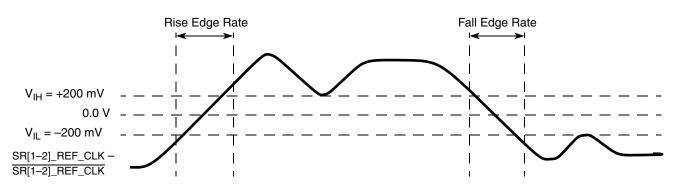

| Figure 5. | Receiver of SerDes Reference Clocks                   |

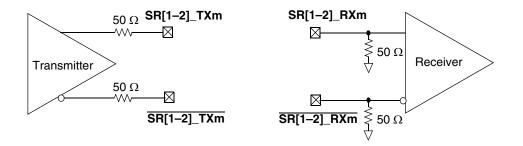

| Figure 6. | SerDes Transmitter and Receiver Reference Circuits 31 |

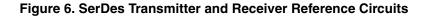

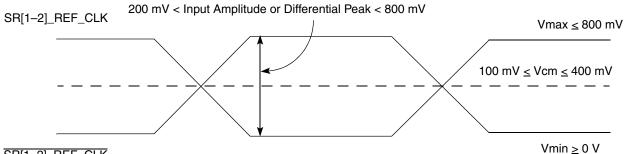

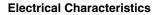

| Figure 7. | Differential Reference Clock Input DC Requirements    |

|           | (External DC-Coupled) 32                              |

| Figure 8. | Differential Reference Clock Input DC Requirements    |

|           | (External AC-Coupled) 32                              |

| Figure 9. | Single-Ended Reference Clock Input DC Requirements 33 |

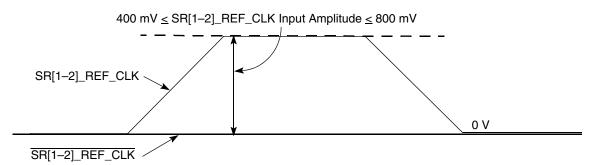

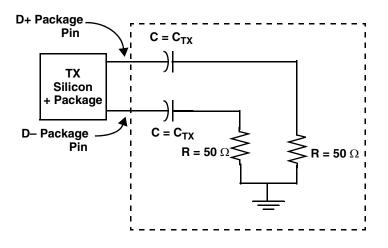

| Figure 10 | .SGMII Transmitter DC Measurement Circuit 35          |

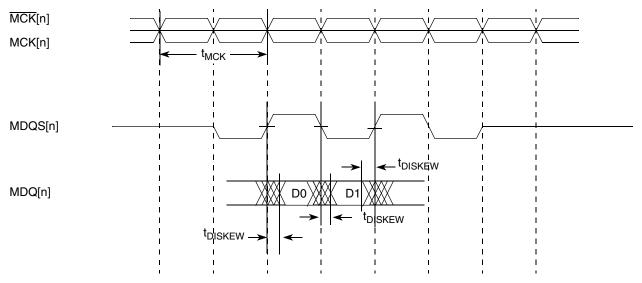

| Figure 11.DDR2 and DDR3 SDRAM Interface Input Timing                |

|---------------------------------------------------------------------|

| Diagram                                                             |

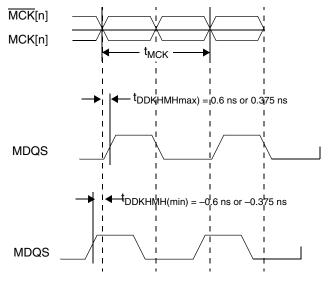

| Figure 12.MCK to MDQS Timing                                        |

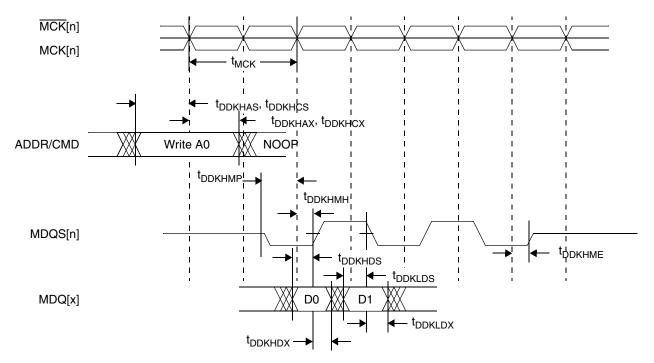

| Figure 13.DDR SDRAM Output Timing                                   |

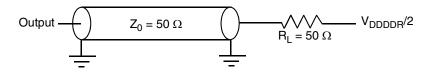

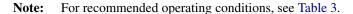

| Figure 14.DDR2 and DDR3 Controller Bus AC Test Load 40              |

| Figure 15.DDR2 and DDR3 SDRAM Differential Timing                   |

| Specifications                                                      |

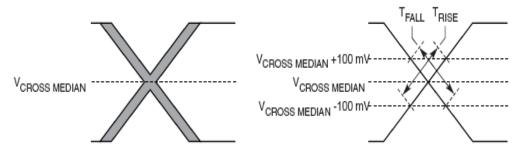

| Figure 16.Differential Measurement Points for Rise and Fall Time 42 |

| Figure 17.Single-Ended Measurement Points for Rise and Fall Time    |

| Matching                                                            |

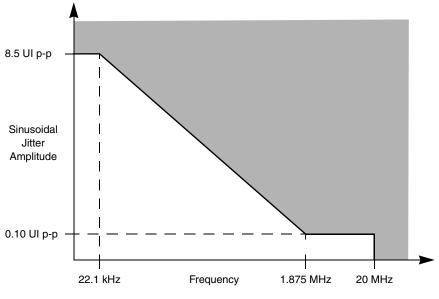

| Figure 18.Single Frequency Sinusoidal Jitter Limits                 |

| Figure 19.SGMII AC Test/Measurement Load                            |

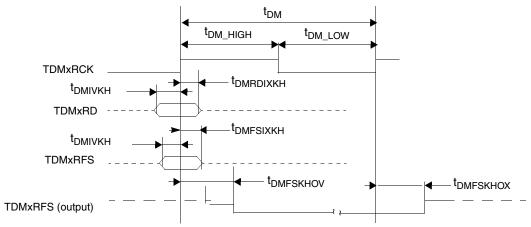

| Figure 20.TDM Receive Signals                                       |

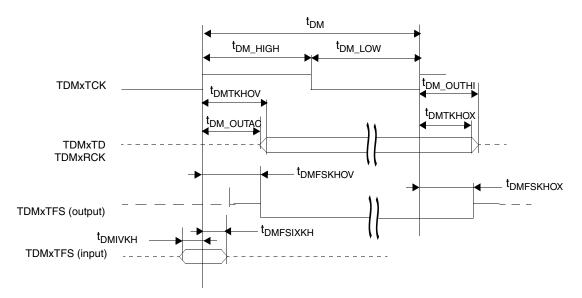

| Figure 21.TDM Transmit Signals                                      |

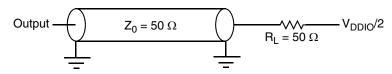

| Figure 22.TDM AC Test Load                                          |

| Figure 23.Timer AC Test Load                                        |

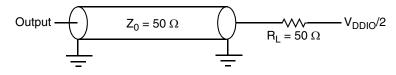

| Figure 24.MII Management Interface Timing                           |

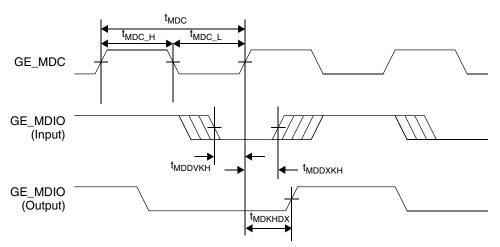

| Figure 25.RGMII AC Timing and Multiplexing                          |

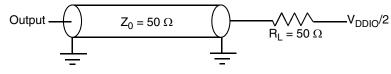

| Figure 26.SPI AC Test Load                                          |

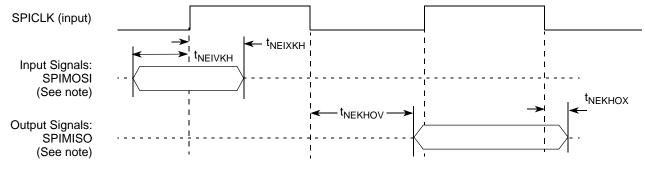

| Figure 27.SPI AC Timing in Slave Mode (External Clock)              |

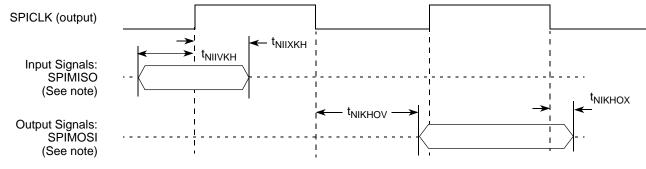

| Figure 28.SPI AC Timing in Master Mode (Internal Clock) 52          |

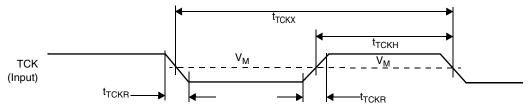

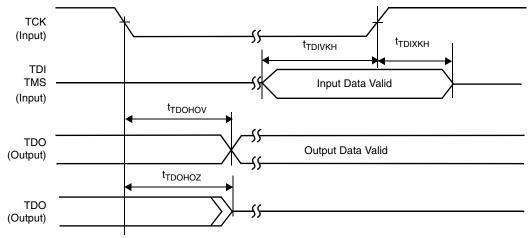

| Figure 29.Test Clock Input Timing                                   |

| Figure 30.Boundary Scan (JTAG) Timing                               |

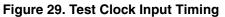

| Figure 31.Test Access Port Timing                                   |

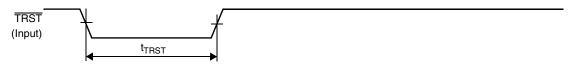

| Figure 32.TRST Timing                                               |

|                                                                     |

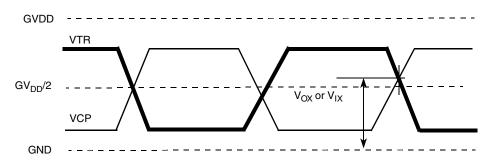

| V <sub>DDIO</sub> and CLKIN Starting With V <sub>DDIO</sub>         |

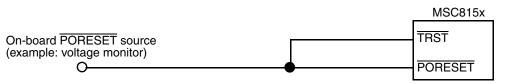

| Figure 35.Reset Connection in Functional Application                |

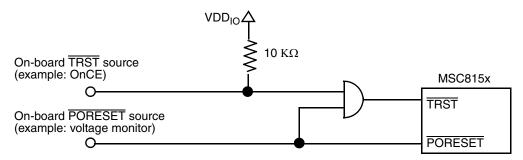

| Figure 36.Reset Connection in Debugger Application                  |

| Figure 37.PLL Supplies                                              |

| Figure 38.SerDes PLL Supplies                                       |

| Figure 39.4-Wire AC-Coupled SGMII Serial Link Connection            |

| Example                                                             |

| Figure 40.MSC8156E Mechanical Information, 783-ball FC-PBGA         |

| Package                                                             |

| 1 donaye0/                                                          |

Figure 1. MSC8156E Block Diagram

Figure 2. StarCore SC3850 DSP Subsystem Block Diagram

**Pin Assignment**

# 1 Pin Assignment

This section includes diagrams of the MSC8156E package ball grid array layouts and tables showing how the pinouts are allocated for the package.

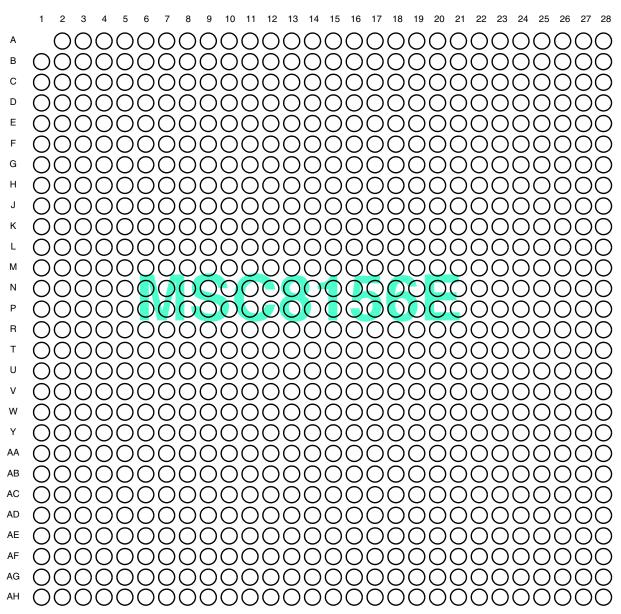

# 1.1 FC-PBGA Ball Layout Diagram

The top view of the FC-PBGA package is shown in Figure 3 with the ball location index numbers.

#### Top View

Figure 3. MSC8156E FC-PBGA Package, Top View

# 1.2 Signal List By Ball Location

Table 1 presents the signal list sorted by ball number. When designing a board, make sure that the power rail for each signal is appropriately considered. The specified power rail must be tied to the voltage level specified in this document if any of the related signal functions are used (active)

**Note:** The information in Table 1 and Table 2 distinguishes among three concepts. First, the power pins are the balls of the device package used to supply specific power levels for different device subsystems (as opposed to signals). Second, the power rails are the electrical lines on the board that transfer power from the voltage regulators to the device. They are indicated here as the reference power rails for signal lines; therefore, the actual power inputs are listed as N/A with regard to the power rails. Third, symbols used in these tables are the names for the voltage levels (absolute, recommended, and so on) and not the power supplies themselves.

| Ball Number | Signal Name <sup>1,2</sup> | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|----------------------------|------------------------|--------------------|

| A2          | M2DQS3                     | I/O                    | GVDD2              |

| A3          | M2DQS3                     | I/O                    | GVDD2              |

| A4          | M2ECC0                     | I/O                    | GVDD2              |

| A5          | M2DQS8                     | I/O                    | GVDD2              |

| A6          | M2DQS8                     | I/O                    | GVDD2              |

| A7          | M2A5                       | 0                      | GVDD2              |

| A8          | M2CK1                      | 0                      | GVDD2              |

| A9          | M2CK1                      | 0                      | GVDD2              |

| A10         | M2CS0                      | 0                      | GVDD2              |

| A11         | M2BA0                      | 0                      | GVDD2              |

| A12         | M2CAS                      | 0                      | GVDD2              |

| A13         | M2DQ34                     | I/O                    | GVDD2              |

| A14         | M2DQS4                     | I/O                    | GVDD2              |

| A15         | M2DQS4                     | I/O                    | GVDD2              |

| A16         | M2DQ50                     | I/O                    | GVDD2              |

| A17         | M2DQS6                     | I/O                    | GVDD2              |

| A18         | M2DQS6                     | I/O                    | GVDD2              |

| A19         | M2DQ48                     | I/O                    | GVDD2              |

| A20         | M2DQ49                     | I/O                    | GVDD2              |

| A21         | VSS                        | Ground                 | N/A                |

| A22         | Reserved                   | NC                     | _                  |

| A23         | SXPVDD1                    | Power                  | N/A                |

| A24         | SXPVSS1                    | Ground                 | N/A                |

| A25         | Reserved                   | NC                     | _                  |

| A26         | Reserved                   | NC                     | _                  |

| A27         | SXCVDD1                    | Power                  | N/A                |

| A28         | SXCVSS1                    | Ground                 | N/A                |

| B1          | M2DQ24                     | I/O                    | GVDD2              |

| B2          | GVDD2                      | Power                  | N/A                |

| B3          | M2DQ25                     | I/O                    | GVDD2              |

| B4          | VSS                        | Ground                 | N/A                |

| B5          | GVDD2                      | Power                  | N/A                |

| B6          | M2ECC1                     | I/O                    | GVDD2              |

#### Table 1. Signal List by Ball Number

| Ball Number | Signal Name <sup>1,2</sup> | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|----------------------------|------------------------|--------------------|

| B7          | VSS                        | Ground                 | N/A                |

| B8          | GVDD2                      | Power                  | N/A                |

| B9          | M2A13                      | 0                      | GVDD2              |

| B10         | VSS                        | Ground                 | N/A                |

| B11         | GVDD2                      | Power                  | N/A                |

| B12         | M2CS1                      | 0                      | GVDD2              |

| B13         | VSS                        | Ground                 | N/A                |

| B14         | GVDD2                      | Power                  | N/A                |

| B15         | M2DQ35                     | I/O                    | GVDD2              |

| B16         | VSS                        | Ground                 | N/A                |

| B17         | GVDD2                      | Power                  | N/A                |

| B18         | M2DQ51                     | I/O                    | GVDD2              |

| B19         | VSS                        | Ground                 | N/A                |

| B20         | GVDD2                      | Power                  | N/A                |

| B21         | Reserved                   | NC                     | —                  |

| B22         | Reserved                   | NC                     | _                  |

| B23         | SR1_TXD0                   | 0                      | SXPVDD1            |

| B24         | SR1_TXD0                   | 0                      | SXPVDD1            |

| B25         | SXCVDD1                    | Power                  | N/A                |

| B26         | SXCVSS1                    | Ground                 | N/A                |

| B27         | SR1_RXD0                   | 1                      | SXCVDD1            |

| B28         | SR1_RXD0                   | 1                      | SXCVDD1            |

| C1          | M2DQ28                     | I/O                    | GVDD2              |

| C2          | M2DM3                      | 0                      | GVDD2              |

| C3          | M2DQ26                     | I/O                    | GVDD2              |

| C4          | M2ECC4                     | I/O                    | GVDD2              |

| C5          | M2DM8                      | 0                      | GVDD2              |

| C6          | M2ECC2                     | I/O                    | GVDD2              |

| C7          | M2CKE1                     | 0                      | GVDD2              |

| C8          | M2CK0                      | 0                      | GVDD2              |

| C9          | M2CK0                      | 0                      | GVDD2              |

| C10         | M2BA1                      | 0                      | GVDD2              |

| C11         | M2A1                       | 0                      | GVDD2              |

| C12         | M2WE                       | 0                      | GVDD2              |

| C13         | M2DQ37                     | I/O                    | GVDD2              |

| C14         | M2DM4                      | 0                      | GVDD2              |

| C15         | M2DQ36                     | I/O                    | GVDD2              |

| C16         | M2DQ32                     | I/O                    | GVDD2              |

| C17         | M2DQ55                     | I/O                    | GVDD2              |

| C18         | M2DM6                      | 0                      | GVDD2              |

| C19         | M2DQ53                     | I/O                    | GVDD2              |

| C20         | M2DQ52                     | I/O                    | GVDD2              |

| C21         | Reserved                   | NC                     | _                  |

| Ball Number | Signal Name <sup>1,2</sup> | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|----------------------------|------------------------|--------------------|

| C22         | SR1_IMP_CAL_RX             | I                      | SXCVDD1            |

| C23         | SXPVSS1                    | Ground                 | N/A                |

| C24         | SXPVDD1                    | Power                  | N/A                |

| C25         | SR1_REF_CLK                | 1                      | SXCVDD1            |

| C26         | SR1_REF_CLK                | 1                      | SXCVDD1            |

| C27         | Reserved                   | NC                     | —                  |

| C28         | Reserved                   | NC                     | —                  |

| D1          | GVDD2                      | Power                  | N/A                |

| D2          | VSS                        | Ground                 | N/A                |

| D3          | M2DQ29                     | I/O                    | GVDD2              |

| D4          | GVDD2                      | Power                  | N/A                |

| D5          | VSS                        | Ground                 | N/A                |

| D6          | M2ECC5                     | I/O                    | GVDD2              |

| D7          | GVDD2                      | Power                  | N/A                |

| D8          | VSS                        | Ground                 | N/A                |

| D9          | M2A8                       | 0                      | GVDD2              |

| D10         | GVDD2                      | Power                  | N/A                |

| D11         | VSS                        | Ground                 | N/A                |

| D12         | M2A0                       | 0                      | GVDD2              |

| D13         | GVDD2                      | Power                  | N/A                |

| D14         | VSS                        | Ground                 | N/A                |

| D15         | M2DQ39                     | I/O                    | GVDD2              |

| D16         | GVDD2                      | Power                  | N/A                |

| D17         | VSS                        | Ground                 | N/A                |

| D18         | M2DQ54                     | I/O                    | GVDD2              |

| D19         | GVDD2                      | Power                  | N/A                |

| D20         | VSS                        | Ground                 | N/A                |

| D21         | SXPVSS1                    | Ground                 | N/A                |

| D22         | SXPVDD1                    | Power                  | N/A                |

| D23         | SR1_TXD1                   | 0                      | SXPVDD1            |

| D24         | SR1_TXD1                   | 0                      | SXPVDD1            |

| D25         | SXCVSS1                    | Ground                 | N/A                |

| D26         | SXCVDD1                    | Power                  | N/A                |

| D27         | SR1_RXD1                   | 1                      | SXCVDD1            |

| D28         | SR1_RXD1                   | 1                      | SXCVDD1            |

| E1          | M2DQ31                     | I/O                    | GVDD2              |

| E2          | M2DQ30                     | I/O                    | GVDD2              |

| E3          | M2DQ27                     | I/O                    | GVDD2              |

| E4          | M2ECC7                     | I/O                    | GVDD2              |

| E5          | M2ECC6                     | I/O                    | GVDD2              |

| E6          | M2ECC3                     | I/O                    | GVDD2              |

| E7          | M2A9                       | 0                      | GVDD2              |

| E8          | M2A6                       | 0                      | GVDD2              |

| Ball Number | Signal Name <sup>1,2</sup>   | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|------------------------------|------------------------|--------------------|

| E9          | M2A3                         | 0                      | GVDD2              |

| E10         | M2A10                        | 0                      | GVDD2              |

| E11         | M2RAS                        | 0                      | GVDD2              |

| E12         | M2A2                         | 0                      | GVDD2              |

| E13         | M2DQ38                       | I/O                    | GVDD2              |

| E14         | M2DQS5                       | I/O                    | GVDD2              |

| E15         | M2DQS5                       | I/O                    | GVDD2              |

| E16         | M2DQ33                       | I/O                    | GVDD2              |

| E17         | M2DQ56                       | I/O                    | GVDD2              |

| E18         | M2DQ57                       | I/O                    | GVDD2              |

| E19         | M2DQS7                       | I/O                    | GVDD2              |

| E20         | Reserved                     | NC                     | _                  |

| E21         | Reserved                     | NC                     | _                  |

| E22         | Reserved                     | NC                     | _                  |

| E23         | SXPVDD1                      | Power                  | N/A                |

| E24         | SXPVSS1                      | Ground                 | N/A                |

| E25         | SR1_PLL_AGND <sup>9</sup>    | Ground                 | SXCVSS1            |

| E26         | SR1_PLL_AVDD <sup>9</sup>    | Power                  | SXCVDD1            |

| E27         | SXCVSS1                      | Ground                 | N/A                |

| E28         | SXCVDD1                      | Power                  | N/A                |

| F1          | VSS                          | Ground                 | N/A                |

| F2          | GVDD2                        | Power                  | N/A                |

| F3          | M2DQ16                       | I/O                    | GVDD2              |

| F4          | VSS                          | Ground                 | N/A                |

| F5          | GVDD2                        | Power                  | N/A                |

| F6          | M2DQ17                       | I/O                    | GVDD2              |

| F7          | VSS                          | Ground                 | N/A                |

| F8          | GVDD2                        | Power                  | N/A                |

| F9          | M2BA2                        | 0                      | GVDD2              |

| F10         | VSS                          | Ground                 | N/A                |

| F11         | GVDD2                        | Power                  | N/A                |

| F12         | M2A4                         | 0                      | GVDD2              |

| F13         | VSS                          | Ground                 | N/A                |

| F14         | GVDD2                        | Power                  | N/A                |

| F15         | M2DQ42                       | I/O                    | GVDD2              |

| F16         | VSS                          | Ground                 | N/A                |

| F17         | GVDD2                        | Power                  | N/A                |

| F18         | M2DQ58                       | I/O                    | GVDD2              |

| F19         | M2DQS7                       | I/O                    | GVDD2              |

| F20         | GVDD2                        | Power                  | N/A                |

| F21         | SXPVDD1                      | Power                  | N/A                |

| F22         | SXPVSS1                      | Ground                 | N/A                |

| F23         | SR1_TXD2/SG1_TX <sup>4</sup> | 0                      | SXPVDD1            |

| Ball Number | Signal Name <sup>1,2</sup>   | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|------------------------------|------------------------|--------------------|

| F24         | SR1_TXD2/SG1_TX <sup>4</sup> | 0                      | SXPVDD1            |

| F25         | SXCVDD1                      | Power                  | N/A                |

| F26         | SXCVSS1                      | Ground                 | N/A                |

| F27         | SR1_RXD2/SG1_RX <sup>4</sup> | 1                      | SXCVDD1            |

| F28         | SR1_RXD2/SG1_RX <sup>4</sup> | 1                      | SXCVDD1            |

| G1          | M2DQS2                       | I/O                    | GVDD2              |

| G2          | M2DQS2                       | I/O                    | GVDD2              |

| G3          | M2DQ19                       | I/O                    | GVDD2              |

| G4          | M2DM2                        | 0                      | GVDD2              |

| G5          | M2DQ21                       | I/O                    | GVDD2              |

| G6          | M2DQ22                       | I/O                    | GVDD2              |

| G7          | M2CKE0                       | 0                      | GVDD2              |

| G8          | M2A11                        | 0                      | GVDD2              |

| G9          | M2A7                         | 0                      | GVDD2              |

| G10         | M2CK2                        | 0                      | GVDD2              |

| G11         | M2APAR_OUT                   | 0                      | GVDD2              |

| G12         | M2ODT1                       | 0                      | GVDD2              |

| G13         | M2APAR_IN                    | I                      | GVDD2              |

| G14         | M2DQ43                       | I/O                    | GVDD2              |

| G15         | M2DM5                        | 0                      | GVDD2              |

| G16         | M2DQ44                       | I/O                    | GVDD2              |

| G17         | M2DQ40                       | I/O                    | GVDD2              |

| G18         | M2DQ59                       | I/O                    | GVDD2              |

| G19         | M2DM7                        | 0                      | GVDD2              |

| G20         | M2DQ60                       | I/O                    | GVDD2              |

| G21         | Reserved                     | NC                     | _                  |

| G22         | Reserved                     | NC                     | _                  |

| G23         | SXPVSS1                      | Ground                 | N/A                |

| G24         | SXPVDD1                      | Power                  | N/A                |

| G25         | SR1_IMP_CAL_TX               | I                      | SXCVDD1            |

| G26         | SXCVSS1                      | Ground                 | N/A                |

| G27         | Reserved                     | NC                     | _                  |

| G28         | Reserved                     | NC                     | _                  |

| H1          | GVDD2                        | Power                  | N/A                |

| H2          | VSS                          | Ground                 | N/A                |

| H3          | M2DQ18                       | I/O                    | GVDD2              |

| H4          | GVDD2                        | Power                  | N/A                |

| H5          | VSS                          | Ground                 | N/A                |

| H6          | M2DQ20                       | I/O                    | GVDD2              |

| H7          | GVDD2                        | Power                  | N/A                |

| H8          | VSS                          | Ground                 | N/A                |

| H9          | M2A15                        | 0                      | GVDD2              |

| H10         | M2CK2                        | 0                      | GVDD2              |

| Ball Number | Signal Name <sup>1,2</sup>   | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|------------------------------|------------------------|--------------------|

| H11         | M2MDIC0                      | I/O                    | GVDD2              |

| H12         | M2VREF                       | 1                      | GVDD2              |

| H13         | M2MDIC1                      | I/O                    | GVDD2              |

| H14         | M2DQ46                       | I/O                    | GVDD2              |

| H15         | M2DQ47                       | I/O                    | GVDD2              |

| H16         | M2DQ45                       | I/O                    | GVDD2              |

| H17         | M2DQ41                       | I/O                    | GVDD2              |

| H18         | M2DQ62                       | I/O                    | GVDD2              |

| H19         | M2DQ63                       | I/O                    | GVDD2              |

| H20         | M2DQ61                       | I/O                    | GVDD2              |

| H21         | Reserved                     | NC                     | _                  |

| H22         | Reserved                     | NC                     | _                  |

| H23         | SR1_TXD3/SG2_TX <sup>4</sup> | 0                      | SXPVDD1            |

| H24         | SR1_TXD3/SG2_TX <sup>4</sup> | 0                      | SXPVDD1            |

| H25         | SXCVSS1                      | Ground                 | N/A                |

| H26         | SXCVDD1                      | Power                  | N/A                |

| H27         | SR1_RXD3/SG2_RX <sup>4</sup> | I                      | SXCVDD1            |

| H28         | SR1_RXD3/SG2_RX <sup>4</sup> | I                      | SXCVDD1            |

| J1          | M2DQS1                       | I/O                    | GVDD2              |

| J2          | M2DQS1                       | I/O                    | GVDD2              |

| J3          | M2DQ10                       | I/O                    | GVDD2              |

| J4          | M2DQ11                       | I/O                    | GVDD2              |

| J5          | M2DQ14                       | I/O                    | GVDD2              |

| J6          | M2DQ23                       | I/O                    | GVDD2              |

| J7          | M2ODT0                       | 0                      | GVDD2              |

| J8          | M2A12                        | 0                      | GVDD2              |

| J9          | M2A14                        | 0                      | GVDD2              |

| J10         | VSS                          | Ground                 | N/A                |

| J11         | GVDD2                        | Power                  | N/A                |

| J12         | VSS                          | Ground                 | N/A                |

| J13         | GVDD2                        | Power                  | N/A                |

| J14         | VSS                          | Ground                 | N/A                |

| J15         | GVDD2                        | Power                  | N/A                |

| J16         | VSS                          | Ground                 | N/A                |

| J17         | GVDD2                        | Power                  | N/A                |

| J18         | VSS                          | Ground                 | N/A                |

| J19         | GVDD2                        | Power                  | N/A                |

| J20         | Reserved                     | NC                     | _                  |

| J21         | Reserved                     | NC                     |                    |

| J22         | Reserved                     | NC                     |                    |

| J23         | SXPVDD1                      | Power                  | N/A                |

| J24         | SXPVSS1                      | Ground                 | N/A                |

| J25         | SXCVDD1                      | Power                  | N/A                |

| Ball Number | Signal Name <sup>1,2</sup> | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|----------------------------|------------------------|--------------------|

| J26         | SXCVSS1                    | Ground                 | N/A                |

| J27         | SXCVDD1                    | Power                  | N/A                |

| J28         | SXCVSS1                    | Ground                 | N/A                |

| K1          | VSS                        | Ground                 | N/A                |

| K2          | GVDD2                      | Power                  | N/A                |

| K3          | M2DM1                      | 0                      | GVDD2              |

| K4          | VSS                        | Ground                 | N/A                |

| K5          | GVDD2                      | Power                  | N/A                |

| K6          | M2DQ0                      | I/O                    | GVDD2              |

| K7          | VSS                        | Ground                 | N/A                |

| K8          | GVDD2                      | Power                  | N/A                |

| K9          | M2DQ5                      | I/O                    | GVDD2              |

| K10         | VSS                        | Ground                 | N/A                |

| K11         | VDD                        | Power                  | N/A                |

| K12         | VSS                        | Ground                 | N/A                |

| K13         | VDD                        | Power                  | N/A                |

| K14         | VSS                        | Ground                 | N/A                |

| K15         | VDD                        | Power                  | N/A                |

| K16         | VSS                        | Ground                 | N/A                |

| K17         | VDD                        | Power                  | N/A                |

| K18         | VSS                        | Ground                 | N/A                |

| K19         | VDD                        | Power                  | N/A                |

| K20         | Reserved                   | NC                     | _                  |

| K21         | Reserved                   | NC                     | _                  |

| K22         | Reserved                   | NC                     | _                  |

| K23         | SXPVDD2                    | Power                  | N/A                |

| K24         | SXPVSS2                    | Ground                 | N/A                |

| K25         | SXCVDD2                    | Power                  | N/A                |

| K26         | SXCVSS2                    | Ground                 | N/A                |

| K27         | SXCVDD2                    | Power                  | N/A                |

| K28         | SXCVSS2                    | Ground                 | N/A                |

| L1          | M2DQ9                      | I/O                    | GVDD2              |

| L2          | M2DQ12                     | I/O                    | GVDD2              |

| L3          | M2DQ13                     | I/O                    | GVDD2              |

| L4          | M2DQS0                     | I/O                    | GVDD2              |

| L5          | M2DQS0                     | I/O                    | GVDD2              |

| L6          | M2DM0                      | 0                      | GVDD2              |

| L7          | M2DQ3                      | I/O                    | GVDD2              |

| L8          | M2DQ2                      | I/O                    | GVDD2              |

| L9          | M2DQ4                      | I/O                    | GVDD2              |

| L10         | VDD                        | Power                  | N/A                |

| L11         | VSS                        | Ground                 | N/A                |

| L12         | M3VDD                      | Power                  | N/A                |

| Ball Number | Signal Name <sup>1,2</sup>           | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|--------------------------------------|------------------------|--------------------|

| L13         | VSS                                  | Ground                 | N/A                |

| L14         | VDD                                  | Power                  | N/A                |

| L15         | VSS                                  | Ground                 | N/A                |

| L16         | VDD                                  | Power                  | N/A                |

| L17         | VSS                                  | Ground                 | N/A                |

| L18         | VDD                                  | Power                  | N/A                |

| L19         | VSS                                  | Ground                 | N/A                |

| L20         | Reserved                             | NC                     | —                  |

| L21         | Reserved                             | NC                     | —                  |

| L22         | Reserved                             | NC                     | —                  |

| L23         | SR2_TXD3/PE_TXD3/SG2_TX <sup>4</sup> | 0                      | SXPVDD2            |

| L24         | SR2_TXD3/PE_TXD3/SG2_TX4             | 0                      | SXPVDD2            |

| L25         | SXCVSS2                              | Ground                 | N/A                |

| L26         | SXCVDD2                              | Power                  | N/A                |

| L27         | SR2_RXD3/PE_RXD3/SG2_RX <sup>4</sup> | 1                      | SXCVDD2            |

| L28         | SR2_RXD3/PE_RXD3/SG2_RX <sup>4</sup> | 1                      | SXCVDD2            |

| M1          | M2DQ8                                | I/O                    | GVDD2              |

| M2          | VSS                                  | Ground                 | N/A                |

| M3          | GVDD2                                | Power                  | N/A                |

| M4          | M2DQ15                               | I/O                    | GVDD2              |

| M5          | M2DQ1                                | I/O                    | GVDD2              |

| M6          | VSS                                  | Ground                 | N/.A               |

| M7          | GVDD2                                | Power                  | N/A                |

| M8          | M2DQ7                                | I/O                    | GVDD2              |

| M9          | M2DQ6                                | I/O                    | GVDD2              |

| M10         | VSS                                  | Ground                 | N/A                |

| M11         | VDD                                  | Power                  | N/A                |

| M12         | VSS                                  | Ground                 | N/A                |

| M13         | VDD                                  | Power                  | N/A                |

| M14         | VSS                                  | Ground                 | N/A                |

| M15         | VDD                                  | Power                  | N/A                |

| M16         | VSS                                  | Ground                 | N/A                |

| M17         | VDD                                  | Power                  | N/A                |

| M18         | VSS                                  | Ground                 | N/A                |

| M19         | VDD                                  | Power                  | N/A                |

| M20         | Reserved                             | NC                     | _                  |

| M21         | Reserved                             | NC                     | _                  |

| M22         | Reserved                             | NC                     | —                  |

| M23         | SXPVSS2                              | Ground                 | N/A                |

| M24         | SXPVDD2                              | Power                  | N/A                |

| M25         | SR2_IMP_CAL_TX                       | 1                      | SXCVDD2            |

| M26         | SXCVSS2                              | Ground                 | N/A                |

| M27         | Reserved                             | NC                     |                    |

| Ball Number | Signal Name <sup>1,2</sup>           | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|--------------------------------------|------------------------|--------------------|

| M28         | Reserved                             | NC                     | _                  |

| N1          | VSS                                  | Ground                 | N/A                |

| N2          | TRST <sup>7</sup>                    |                        | QVDD               |

| N3          | PORESET <sup>7</sup>                 | Ι                      | QVDD               |

| N4          | VSS                                  | Ground                 | N/A                |

| N5          | TMS <sup>7</sup>                     | Ι                      | QVDD               |

| N6          | CLKOUT                               | 0                      | QVDD               |

| N7          | VSS                                  | Ground                 | N/A                |

| N8          | VSS                                  | Ground                 | N/A                |

| N9          | VSS                                  | Ground                 | N/A                |

| N10         | VDD                                  | Power                  | N/A                |

| N11         | VSS                                  | Ground                 | N/A                |

| N12         | M3VDD                                | Power                  | N/A                |

| N13         | VSS                                  | Ground                 | N/A                |

| N14         | VDD                                  | Power                  | N/A                |

| N15         | VSS                                  | Ground                 | N/A                |

| N16         | VDD                                  | Power                  | N/A                |

| N17         | VSS                                  | Ground                 | N/A                |

| N18         | VDD                                  | Power                  | N/A                |

| N19         | VSS                                  | Ground                 | N/A                |

| N20         | Reserved                             | NC                     | _                  |

| N21         | SXPVDD2                              | Power                  | N/A                |

| N22         | SXPVSS2                              | Ground                 | N/A                |

| N23         | SR2_TXD2/PE_TXD2/SG1_TX <sup>4</sup> | 0                      | SXPVDD2            |

| N24         | SR2_TXD2/PE_TXD2/SG1_TX4             | 0                      | SXPVDD2            |

| N25         | SXCVDD2                              | Power                  | N/A                |

| N26         | SXCVSS2                              | Ground                 | N/A                |

| N27         | SR2_RXD2/PE_RXD2/SG1_RX <sup>4</sup> | I                      | SXCVDD2            |

| N28         | SR2_RXD2/PE_RXD2/SG1_RX <sup>4</sup> |                        | SXCVDD2            |

| P1          |                                      |                        | QVDD               |

| P2          | EE0                                  | I                      | QVDD               |

| P3          | QVDD                                 | Power                  | N/A                |

| P4          | VSS                                  | Ground                 | N/A                |

| P5          | STOP_BS                              |                        | QVDD               |

| P6          | QVDD                                 | Power                  | N/A                |

| P7          | VSS                                  | Ground                 | N/A                |

| P8          | PLL0_AVDD <sup>9</sup>               | Power                  | VDD                |

| P9          | PLL2_AVDD <sup>9</sup>               | Power                  | VDD                |

| P10         | VSS                                  | Ground                 | N/A                |

| P11         | VDD                                  | Power                  | N/A                |

| P12         | VSS                                  | Ground                 | N/A                |

| P13         | VDD                                  | Power                  | N/A                |

| P14         | VSS                                  | Ground                 | N/A                |

| Ball Number | Signal Name <sup>1,2</sup>    | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|-------------------------------|------------------------|--------------------|

| P15         | MVDD                          | Power                  | N/A                |

| P16         | VSS                           | Ground                 | N/A                |

| P17         | MVDD                          | Power                  | N/A                |

| P18         | VSS                           | Ground                 | N/A                |

| P19         | VDD                           | Power                  | N/A                |

| P20         | Reserved                      | NC                     | —                  |

| P21         | Reserved                      | NC                     | —                  |

| P22         | Reserved                      | NC                     | —                  |

| P23         | SXPVDD2                       | Power                  | N/A                |

| P24         | SXPVSS2                       | Ground                 | N/A                |

| P25         | SR2_PLL_AGND <sup>9</sup>     | Ground                 | SXCVSS2            |

| P26         | SR2_PLL_AVDD <sup>9</sup>     | Power                  | SXCVDD2            |

| P27         | SXCVSS2                       | Ground                 | N/A                |

| P28         | SXCVDD2                       | Power                  | N/A                |

| R1          | VSS                           | Ground                 | N/A                |

| R2          | NMI                           | I                      | QVDD               |

| R3          | NMI_OUT <sup>6</sup>          | 0                      | QVDD               |

| R4          | HRESET <sup>6,7</sup>         | I/O                    | QVDD               |

| R5          | INT_OUT <sup>6</sup>          | 0                      | QVDD               |

| R6          | EE1                           | 0                      | QVDD               |

| R7          | VSS                           | Ground                 | N/A                |

| R8          | PLL1_AVDD <sup>9</sup>        | Power                  | VDD                |

| R9          | VSS                           | Ground                 | N/A                |

| R10         | VDD                           | Power                  | N/A                |

| R11         | VSS                           | Non-user               | N/A                |

| R12         | VDD                           | Power                  | N/A                |

| R13         | VSS                           | Ground                 | N/A                |

| R14         | VDD                           | Power                  | N/A                |

| R15         | VSS                           | Ground                 | N/A                |

| R16         | MVDD                          | Power                  | N/A                |

| R17         | VSS                           | Ground                 | N/A                |

| R18         | VDD                           | Power                  | N/A                |

| R19         | VSS                           | Ground                 | N/A                |

| R20         | VSS                           | Non-user               | N/A                |

| R21         | SXPVSS2                       | Ground                 | N/A                |

| R22         | SXPVDD2                       | Power                  | N/A                |

| R23         | SR2_TXD1/PE_TXD1 <sup>4</sup> | 0                      | SXPVDD2            |

| R24         | SR2_TXD1/PE_TXD1 <sup>4</sup> | 0                      | SXPVDD2            |

| R25         | SXCVSS2                       | Ground                 | N/A                |

| R26         | SXCVDD2                       | Power                  | N/A                |

| R27         | SR2_RXD1/PE_RXD1 <sup>4</sup> | l                      | SXCVDD2            |

| R28         | SR2_RXD1/PE_RXD1 <sup>4</sup> | I                      | SXCVDD2            |

| T1          | VSS                           | Ground                 | N/A                |

| Ball Number | Signal Name <sup>1,2</sup> | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|----------------------------|------------------------|--------------------|

| T2          | ТСК                        | I                      | QVDD               |

| Т3          | SRESET <sup>6,7</sup>      | I/O                    | QVDD               |

| T4          | TDI                        | I                      | QVDD               |

| T5          | VSS                        | Ground                 | N/A                |

| Т6          | TDO                        | 0                      | QVDD               |

| Τ7          | VSS                        | Ground                 | N/A                |

| Т8          | VSS                        | Ground                 | N/A                |

| Т9          | QVDD                       | Power                  | N/A                |

| T10         | VSS                        | Ground                 | N/A                |

| T11         | VDD                        | Power                  | N/A                |

| T12         | VSS                        | Ground                 | N/A                |

| T13         | M3VDD                      | Power                  | N/A                |

| T14         | VSS                        | Ground                 | N/A                |

| T15         | VDD                        | Power                  | N/A                |

| T16         | VSS                        | Ground                 | N/A                |

| T17         | MVDD                       | Power                  | N/A                |

| T18         | VSS                        | Ground                 | N/A                |

| T19         | VDD                        | Power                  | N/A                |

| T20         | VSS                        | Ground                 | N/A                |

| T21         | VSS                        | Non-user               | N/A                |

| T22         | SR2_IMP_CAL_RX             | I                      | SXCVDD2            |

| T23         | SXPVSS2                    | Ground                 | N/A                |

| T24         | SXPVDD2                    | Power                  | N/A                |

| T25         | SR2_REF_CLK                | I                      | SXCVDD2            |

| T26         | SR2_REF_CLK                | I                      | SXCVDD2            |

| T27         | Reserved                   | NC                     | _                  |

| T28         | Reserved                   | NC                     | _                  |

| U1          | M1DQ8                      | I/O                    | GVDD1              |

| U2          | VSS                        | Ground                 | N/A                |

| U3          | GVDD1                      | Power                  | N/A                |

| U4          | M1DQ15                     | I/O                    | GVDD1              |

| U5          | M1DQ1                      | I/O                    | GVDD1              |

| U6          | VSS                        | Ground                 | N/A                |

| U7          | GVDD1                      | Power                  | N/A                |

| U8          | M1DQ7                      | I/O                    | GVDD1              |

| U9          | M1DQ6                      | I/O                    | GVDD1              |

| U10         | VDD                        | Power                  | N/A                |

| U11         | VSS                        | Ground                 | N/A                |

| U12         | M3VDD                      | Power                  | N/A                |

| U13         | VSS                        | Ground                 | N/A                |

| U14         | VDD                        | Power                  | N/A                |

| U15         | VSS                        | Ground                 | N/A                |

| U16         | VDD                        | Power                  | N/A                |

| Ball Number | Signal Name <sup>1,2</sup>    | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|-------------------------------|------------------------|--------------------|

| U17         | VSS                           | Ground                 | N/A                |

| U18         | VDD                           | Power                  | N/A                |

| U19         | VSS                           | Ground                 | N/A                |

| U20         | VSS                           | Ground                 | N/A                |

| U21         | VSS                           | Ground                 | N/A                |

| U22         | VSS                           | Non-user               | N/A                |

| U23         | SR2_TXD0/PE_TXD0 <sup>4</sup> | 0                      | SXPVDD2            |

| U24         | SR2_TXD0/PE_TXD0 <sup>4</sup> | 0                      | SXPVDD2            |

| U25         | SXCVDD2                       | Power                  | N/A                |

| U26         | SXCVSS2                       | Ground                 | N/A                |

| U27         | SR2_RXD0/PE_RXD0 <sup>4</sup> | I                      | SXCVDD2            |

| U28         | SR2_RXD0/PE_RXD0 <sup>4</sup> | I                      | SXCVDD2            |

| V1          | M1DQ9                         | I/O                    | GVDD1              |

| V2          | M1DQ12                        | I/O                    | GVDD1              |

| V3          | M1DQ13                        | I/O                    | GVDD1              |

| V4          | M1DQS0                        | I/O                    | GVDD1              |

| V5          | M1DQS0                        | I/O                    | GVDD1              |

| V6          | M1DM0                         | 0                      | GVDD1              |

| V7          | M1DQ3                         | I/O                    | GVDD1              |

| V8          | M1DQ2                         | I/O                    | GVDD1              |

| V9          | M1DQ4                         | I/O                    | GVDD1              |

| V10         | VSS                           | Ground                 | N/A                |

| V11         | VDD                           | Power                  | N/A                |

| V12         | VSS                           | Ground                 | N/A                |

| V13         | VDD                           | Power                  | N/A                |

| V14         | VSS                           | Ground                 | N/A                |

| V15         | VDD                           | Power                  | N/A                |

| V16         | VSS                           | Ground                 | N/A                |

| V17         | VDD                           | Power                  | N/A                |

| V18         | VSS                           | Ground                 | N/A                |

| V19         | VDD                           | Power                  | N/A                |

| V20         | NVDD                          | Power                  | N/A                |

| V21         | RCW_LSEL_3/RC20               | I/O                    | NVDD               |

| V22         | RCW_LSEL_2/RC19               | I/O                    | NVDD               |

| V23         | SXPVDD2                       | Power                  | N/A                |

| V24         | SXPVSS2                       | Ground                 | N/A                |

| V25         | RCW_LSEL_1/RC18               | I/O                    | NVDD               |

| V26         | RC21                          | I                      | NVDD               |

| V27         | SXCVDD2                       | Power                  | N/A                |

| V28         | SXCVSS2                       | Ground                 | N/A                |

| W1          | VSS                           | Ground                 | N/A                |

| W2          | GVDD1                         | Power                  | N/A                |

| W3          | M1DM1                         | 0                      | GVDD1              |

| Ball Number | Signal Name <sup>1,2</sup>         | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|------------------------------------|------------------------|--------------------|

| W4          | VSS                                | Ground                 | N/A                |

| W5          | GVDD1                              | Power                  | N/A                |

| W6          | M1DQ0                              | I/O                    | GVDD1              |

| W7          | VSS                                | Ground                 | N/A                |

| W8          | GVDD1                              | Power                  | N/A                |

| W9          | M1DQ5                              | I/O                    | GVDD1              |

| W10         | VDD                                | Power                  | N/A                |

| W11         | VSS                                | Ground                 | N/A                |

| W12         | VDD                                | Power                  | N/A                |

| W13         | VSS                                | Ground                 | N/A                |

| W14         | VDD                                | Power                  | N/A                |

| W15         | VSS                                | Ground                 | N/A                |

| W16         | VDD                                | Power                  | N/A                |

| W17         | VSS                                | Ground                 | N/A                |

| W18         | VDD                                | Power                  | N/A                |

| W19         | VSS                                | Ground                 | N/A                |

| W20         | VSS                                | Ground                 | N/A                |

| W21         | RCW_LSEL0/RC17                     | I/O                    | NVDD               |

| W22         | GPIO19/SPI_MISO <sup>5,8</sup>     | I/O                    | NVDD               |

| W23         | VSS                                | Ground                 | N/A                |

| W24         | NVDD                               | Power                  | N/A                |

| W25         | GPIO11/IRQ11/RC11 <sup>5,8</sup>   | I/O                    | NVDD               |

| W26         | GPIO3/DRQ1/IRQ3/RC3 <sup>5,8</sup> | I/O                    | NVDD               |

| W27         | GPIO7/IRQ7/RC7 <sup>5,8</sup>      | I/O                    | NVDD               |

| W28         | GPIO2/IRQ2/RC2 <sup>5,8</sup>      | I/O                    | NVDD               |

| Y1          | M1DQS1                             | I/O                    | GVDD1              |

| Y2          | M1DQS1                             | I/O                    | GVDD1              |

| Y3          | M1DQ10                             | I/O                    | GVDD1              |

| Y4          | M1DQ11                             | I/O                    | GVDD1              |

| Y5          | M1DQ14                             | I/O                    | GVDD1              |

| Y6          | M1DQ23                             | I/O                    | GVDD1              |

| Y7          | M1ODT0                             | 0                      | GVDD1              |

| Y8          | M1A12                              | 0                      | GVDD1              |

| Y9          | M1A14                              | 0                      | GVDD1              |

| Y10         | VSS                                | Ground                 | N/A                |

| Y11         | GVDD1                              | Power                  | N/A                |

| Y12         | VSS                                | Ground                 | N/A                |

| Y13         | GVDD1                              | Power                  | N/A                |

| Y14         | VSS                                | Ground                 | N/A                |

| Y15         | GVDD1                              | Power                  | N/A                |

| Y16         | VSS                                | Ground                 | N/A                |

| Y17         | GVDD1                              | Power                  | N/A                |

| Y18         | VSS                                | Ground                 | N/A                |

| Ball Number | Signal Name <sup>1,2</sup>            | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|---------------------------------------|------------------------|--------------------|

| Y19         | GVDD1                                 | Power                  | N/A                |

| Y20         | VSS                                   | Ground                 | N/A                |

| Y21         | NVDD                                  | Power                  | N/A                |

| Y22         | GPIO20/SPI_SL <sup>5,8</sup>          | I/O                    | NVDD               |

| Y23         | GPIO17/SPI_SCK <sup>5,8</sup>         | I/O                    | NVDD               |

| Y24         | GPIO14/DRQ0/IRQ14/RC14 <sup>5,8</sup> | I/O                    | NVDD               |

| Y25         | GPIO12/IRQ12/RC12 <sup>5,8</sup>      | I/O                    | NVDD               |

| Y26         | GPIO8/IRQ8/RC8 <sup>5,8</sup>         | I/O                    | NVDD               |

| Y27         | NVDD                                  | Power                  | N/A                |

| Y28         | VSS                                   | Ground                 | N/A                |

| AA1         | GVDD1                                 | Power                  | N/A                |

| AA2         | VSS                                   | Ground                 | N/A                |

| AA3         | M1DQ18                                | I/O                    | GVDD1              |

| AA4         | GVDD1                                 | Power                  | N/A                |

| AA5         | VSS                                   | Ground                 | N/A                |

| AA6         | M1DQ20                                | I/O                    | GVDD1              |

| AA7         | GVDD1                                 | Power                  | N/A                |

| AA8         | VSS                                   | Ground                 | N/A                |

| AA9         | M1A15                                 | 0                      | GVDD1              |

| AA10        | M1CK2                                 | 0                      | GVDD1              |

| AA11        | M1MDIC0                               | I/O                    | GVDD1              |

| AA12        | M1VREF                                | I                      | GVDD1              |

| AA13        | M1MDIC1                               | I/O                    | GVDD1              |

| AA14        | M1DQ46                                | I/O                    | GVDD1              |

| AA15        | M1DQ47                                | I/O                    | GVDD1              |

| AA16        | M1DQ45                                | I/O                    | GVDD1              |

| AA17        | M1DQ41                                | I/O                    | GVDD1              |

| AA18        | M1DQ62                                | I/O                    | GVDD1              |

| AA19        | M1DQ63                                | I/O                    | GVDD1              |

| AA20        | M1DQ61                                | I/O                    | GVDD1              |

| AA21        | VSS                                   | Ground                 | N/A                |

| AA22        | GPIO21 <sup>5,8</sup>                 | I/O                    | NVDD               |

| AA23        | GPIO18/SPI_MOSI <sup>5,8</sup>        | I/O                    | NVDD               |

| AA24        | GPIO16/RC16 <sup>5,8</sup>            | I/O                    | NVDD               |

| AA25        | GPIO4/DDN1/IRQ4/RC4 <sup>5,8</sup>    | I/O                    | NVDD               |

| AA26        | GPIO9/IRQ9/RC9 <sup>5,8</sup>         | I/O                    | NVDD               |

| AA27        | GPIO6/IRQ6/RC6 <sup>5,8</sup>         | I/O                    | NVDD               |

| AA28        | GPIO1/IRQ1/RC1 <sup>5,8</sup>         | I/O                    | NVDD               |

| AB1         | M1DQS2                                | I/O                    | GVDD1              |

| AB2         | M1DQS2                                | I/O                    | GVDD1              |

| AB3         | M1DQ19                                | I/O                    | GVDD1              |

| AB4         | M1DM2                                 | 0                      | GVDD1              |

| AB5         | M1DQ21                                | I/O                    | GVDD1              |

| Ball Number | Signal Name <sup>1,2</sup>          | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|-------------------------------------|------------------------|--------------------|

| AB6         | M1DQ22                              | I/O                    | GVDD1              |

| AB7         | M1CKE0                              | 0                      | GVDD1              |

| AB8         | M1A11                               | 0                      | GVDD1              |

| AB9         | M1A7                                | 0                      | GVDD1              |

| AB10        | M1CK2                               | 0                      | GVDD1              |

| AB11        | M1APAR_OUT                          | 0                      | GVDD1              |

| AB12        | M1ODT1                              | 0                      | GVDD1              |

| AB13        | M1APAR_IN                           | 1                      | GVDD1              |

| AB14        | M1DQ43                              | I/O                    | GVDD1              |

| AB15        | M1DM5                               | 0                      | GVDD1              |

| AB16        | M1DQ44                              | I/O                    | GVDD1              |

| AB17        | M1DQ40                              | I/O                    | GVDD1              |

| AB18        | M1DQ59                              | I/O                    | GVDD1              |

| AB19        | M1DM7                               | 0                      | GVDD1              |

| AB20        | M1DQ60                              | I/O                    | GVDD1              |

| AB21        | VSS                                 | Ground                 | N/A                |

| AB22        | GPIO31/I2C_SDA <sup>5,8</sup>       | I/O                    | NVDD               |

| AB23        | GPIO27/TMR4/RCW_SRC0 <sup>5,8</sup> | I/O                    | NVDD               |

| AB24        | GPIO25/TMR2/RCW_SRC1 <sup>5,8</sup> | I/O                    | NVDD               |

| AB25        | GPIO24/TMR1/RCW_SRC2 <sup>5,8</sup> | I/O                    | NVDD               |

| AB26        | GPIO10/IRQ10/RC10 <sup>5,8</sup>    | I/O                    | NVDD               |

| AB27        | GPIO5/IRQ5/RC5 <sup>5,8</sup>       | I/O                    | NVDD               |

| AB28        | GPIO0/IRQ0/RC0 <sup>5,8</sup>       | I/O                    | NVDD               |

| AC1         | VSS                                 | Ground                 | N/A                |

| AC2         | GVDD1                               | Power                  | N/A                |

| AC3         | M1DQ16                              | I/O                    | GVDD1              |

| AC4         | VSS                                 | Ground                 | N/A                |

| AC5         | GVDD1                               | Power                  | N/A                |

| AC6         | M1DQ17                              | I/O                    | GVDD1              |

| AC7         | VSS                                 | Ground                 | N/A                |

| AC8         | GVDD1                               | Power                  | N/A                |

| AC9         | M1BA2                               | 0                      | GVDD1              |

| AC10        | VSS                                 | Ground                 | N/A                |

| AC11        | GVDD1                               | Power                  | N/A                |

| AC12        | M1A4                                | 0                      | GVDD1              |