## Application Note

# Kinetis 100 MHz Rev 1.x to 120 MHz Migration Guide

### 1 Purpose and overview

This document describes the details of migrating from Kinetis 100 MHz Revision 1.x microcontrollers to Kinetis 120/150 MHz microcontrollers. Migrating between the two devices within the same family could require hardware and/or software changes in some cases. Changes that might be required are described in this document.

#### **Contents**

| 1 | Purpose and overview            | 1  |

|---|---------------------------------|----|

| 2 | New Modules                     | 3  |

| 3 | Updated Modules                 | 4  |

| 4 | Enhanced Modules                | 36 |

| 5 | Modules with New Instantiations | 75 |

| 6 | Unchanged Modules               | 75 |

| 7 | Appendices                      | 76 |

rurpose and overview

### 1.1 Part numbering and mask set information

The table below lists all of the Kinetis 100 MHz rev 1.x mask sets that have been produced as of the writing of this document.

Table 1. Kinetis 100 MHz Rev 1.x mask sets

| Revision | Mask Set                               | Part Number Example                                          |

|----------|----------------------------------------|--------------------------------------------------------------|

| 1.0      | 0M33Z                                  | PK10N512VMD100                                               |

| 1.1      | 0N30D                                  | N/A                                                          |

| 1.2      | 1N30D / 2N30D (functionally identical) | PK10N512VMD100                                               |

| 1.4      |                                        | MK10DN512ZVMD10 ('Z' character: INITIAL Production mask set) |

The table below lists the Kinetis 120 and 150 MHz masks sets that have been produced as of the writing of this document.

Table 2. Kinetis 120 and 150 MHz mask sets

| Revision | Mask Set | Part Number Example |

|----------|----------|---------------------|

| 1.0      | 0N96B    | PK60FN1M0VMJ12      |

| 1.1      | 1N96B    | PK60FN1M0VMJ12      |

| 1.3      | 3N96B    | MK60FN1M0VMJ12      |

This document is primarily focused on migration between 100 MHz and 120/150MHz devices within the same Kinetis family. For example, this document will help if you are migrating from an MK60DN512VMD10 to a PK60FN1M0VMD12, but if you are migrating from a K10 to a K60 device, this document might still have some helpful information but it is not focused on addressing the changes in functionality between the Kinetis families.

### 1.2 About this document

This document describes migration between Kinetis 100 MHz and Kinetis 120 and 150 MHz devices. The 120 and 150 MHz devices are speed grade options for the same devices. There are no functional or feature differences between the speed grades with the exception of the core frequency and resulting performance increase. For simplicity, the document will refer to these devices as Kinetis 120 MHz devices. The information applies to the 150 MHz devices as well, but they will not be specifically referenced.

This document is divided up into five major sections – new modules, updated modules, enhanced modules, modules with additional instantiations, and unchanged modules.

The new modules section provides a quick overview of modules that are completely new for the 120 MHz devices. These are modules that don't have any functional equivalent available in the 100 MHz microcontrollers. If any of these new modules will be used in your application, then you'll require software changes to use the new module. Most of the modules will also require hardware changes to use them with the exception of the LMEM and FPU.

The updated modules section outlines the modules that have been updated to use newer versions. The overall functionality provided will be similar, however, changes will be required in software. Hardware changes may be required in order to utilize new features.

The enhanced modules section outlines the existing modules which have undergone minor changes. Software and hardware changes may be required in order to utilize new features.

The modules with additional instantiations sections describes modules where the modules themselves don't have changes, but there are more instantiations of the module included in the microcontroller.

The unchanged modules section lists modules that are the same between the 100 MHz and 120 MHz devices.

Additionally, a color coding scheme has been used throughout this document where:

- GREEN: Designates new additions,YELLOW: Designates changes, and

- RED: Designates removals

### 2 New Modules

The Kinetis 120 MHz platforms adds several modules that are not available on the 100 MHz devices. The following sections give an overview of the features of these modules. Applications that want to take advantage of these new modules will require software changes and in some cases hardware changes to take advantage of the new functionality.

Availability of these modules can depend on the specific Kinetis device that you are using. Please refer to the reference manual for your Kinetis device for information on which features are available.

### 2.1 NAND Flash Controller (NFC)

The NAND flash controller (NFC) interfaces to standard NAND flash memory devices. It is composed of various control logic units and a 9 KB SRAM buffer. The NFC provides a glueless interface to 8- and 16-bit NAND flash devices with page sizes of 512 bytes, 2 KB, 4 KB, and 8 KB.

### 2.2 DDR Memory Controller (DDRMC)

Interface to store and retrieve data from an external SDRAM. Supports glue-less interface to 16-bit or 8-bit DDR1, DDR2, or LPDDR SDRAM memories.

### 2.3 USB High Speed OTG Controller (USBHS)

The USB high speed OTG controller (USBHS) is a USB 2.0-compliant serial interface engine for implementing a USB interface. The registers and data structures are based on the Enhanced Host Controller Interface Specification for Universal Serial Bus (EHCI) from Intel Corporation. The USBHS module can act as a host, a device, or an On-The-Go negotiable host/device on the USB bus. The USBHS controller interfaces to the processor's core. The controller is programmable to support host or device operations under firmware control. To operate the USB HS OTG controller, connect the USB HS controller to an external ULPI PHY/transceiver via the ULPI interface.

### 2.4 Graphical LCD Controller (LCDC)

Provides display data for external gray-scale or color LCD panels. It supports black-and-white, gray-scale, passive-matrix color (CSTN), and active-matrix color (TFT) LCD panels. The maximum panel resolution supported is 800x600 with up to 24 bpp color.

### 2.5 MCU Drylce

The MCU DryIce module includes a 32-byte secure memory that is asynchronously erased on any tamper detect. In addition it can optionally force a system reset and/or invalidate the Real Time Clock.

### 2.6 Local Memory Controller (LMEM)

The local memory controller is a combination of the system RAM controller that is used on all Kinetis devices and a system cache controller that is new to the 120 MHz Kinetis devices. The LMEM manages simultaneous accesses to system RAM by multiple master peripherals and core and also controls cache which improves system performance by providing single-cycle access to the instruction and data pipelines.

### 2.7 Floating Point Unit (FPU)

The Kinetis 120 MHz devices add in the Cortex M4 core's optional floating point unit. The single precision FPU is compliant to the *IEEE Standard for Floating-Point Arithmetic* (IEEE 754).

### 3 Updated Modules

### 3.1 Flash Memory Module (FTFL to FTFE)

In order to support the higher density of flash available on the 120 MHz Kinetis devices, the flash block has been changed. The 100 MHz devices use the FTFL module and support up to 512 KB of flash, while the 120 MHz devices use the FTFE module and support up to 1 MB of flash.

In addition to supporting larger flash arrays, the 120 MHz devices also support a larger FlexRAM. 100 MHz devices have up to 4 KB of FlexRAM, while the 120 MHz devices have up to 16 KB of FlexRAM.

### 3.1.1 Memory map comparison

The FTFE and FTFL use different module acronyms, but other than that the memory map remains the same. For example, on a 100 MHz device there is an FTFL\_FSTAT register. The FTFL\_FSTAT register becomes the FTFE\_FSTAT register on a 120 MHz device. All of the register addresses and fields are identical only the preceding acronym changes.

### 3.1.2 Software impact

The biggest change when moving from the FTFL to the FTFE module is that the programming size for the flash changes. The FTFL module uses a program longword command (FCMD = 0x6) to program 32 bits at a time, while the FTFE module uses a program phrase command (FCMD = 0x7) to program 64 bits at a time. Any application that modifies the flash contents will need to be changed to use the new program size.

Another change is that the default size of the flash protection regions increases. For example, there are 32 P-flash protection regions on both the FTFE and FTFL where the total P-flash size is even distributed across the 32 regions. For an FTFE device with twice as much P-flash, the size of the P-flash protection regions will double. The D-flash and EEPROM protection region sizes also increase accordingly.

### 3.1.3 Hardware impact

No hardware impact.

### 3.2 Power Management Controller (PMC)

The primary duties of the Power Management Controller (PMC) are: control the regulator, control the POR and LVD circuits, and provide voltage and current sources for the MCU. For Kinetis 120 MHz devices the I/O retention control is now in the PMC. The functionality of the PMC is linked closely with the Low Leakage Wakeup Unit (LLWU), the System Mode Controller (SMC), and the new Reset Control Module (RCM).

### 3.2.1 Memory map comparison

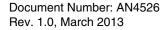

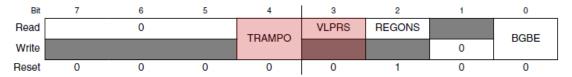

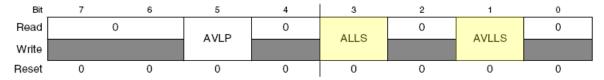

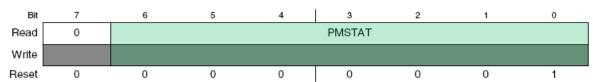

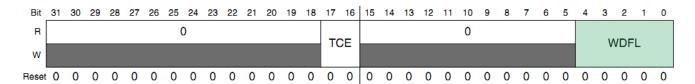

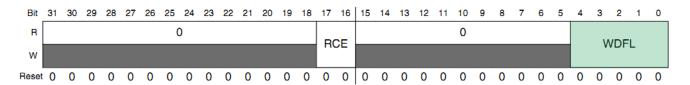

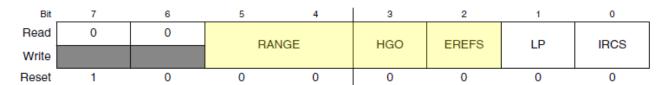

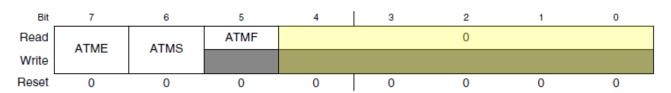

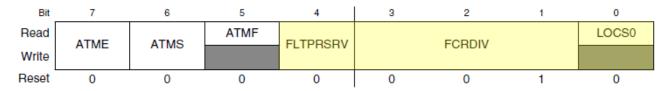

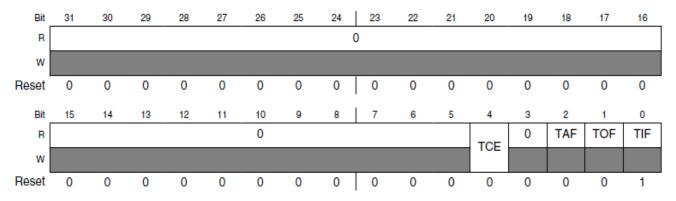

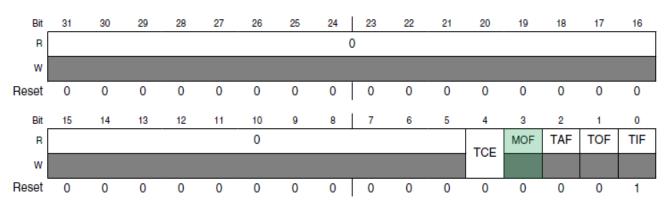

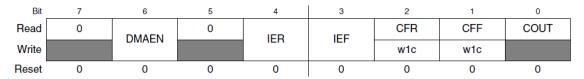

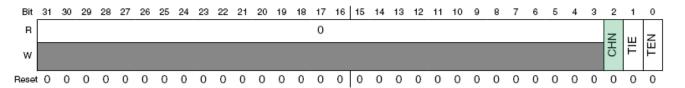

The register map and names have remained the same. The figure below shows the only bit level changes to the memory map.

Figure 1. PMC REGSC—Kinetis 100 MHz Rev. 1.x

Figure 2. PMC\_REGSC—Kinetis 120 MHz

#### Removed bit/field names:

- TRAMPO

- VLPRS

#### Changed bit/field names:

• ACKISO - Moved from LLWU to PMC

### 3.2.2 Software impact

The PMC register names are the same; however, some important bit changes have been made.

**TRAMPO:** The TRAMPO bit has been removed. There is a new bit in the SMC—RAM2PO—that controls the RAM power in VLLS2. The new RAM2PO bit has different functionality, however.

**VLPRS:** The VLPRS bit has been removed. Software only needs to check the Run Regulator Status and the SMC\_PMSTAT register when entering VLPR mode. The REGONS bit will clear when the regulator is in stop regulation or transition to/from it and the SMC\_PMSTAT will read 04 when the MCU power mode is in VLPR.

**ACKISO:** The PMC has the acknowledge to clear the hold on the state of the I/O pins and oscillator module. This bit used to reside in the LLWU. This bit must be cleared upon recovery from VLLSx modes to release the hold on the I/O and oscillator modules.

### 3.2.3 Hardware impact

**Bandgap Enable (BGEN)**: The new bit has hardware interaction impact. If BGEN is set, then the bandgap is turned on. The operation of this bit may be needed by other circuitry like the VREF module or ADC.

**ACKISO:** The ACKISO bit is an important bit to consider when working with the low power modes of operation. The MCU recovers from VLLSx through the reset flow. Typically the port I/O, module initialization of timers, communications modules, and the oscillator should be initialized prior to acknowledging the release of the I/O.

### 3.3 Mode Controller Version 1 to Version 2

The primary duty of the Mode Controller (MC) and System Mode Controller (SMC) has been to control the entry into and exit from each power mode. The module has a new name in newer Kinetis devices. The MC is now the SMC. The functionality of the SMC has always been linked closely with the Power Management Controller (PMC), the Low Leakage Wakeup Unit (LLWU), and the new Reset Control Module (RCM).

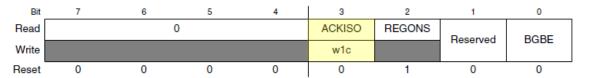

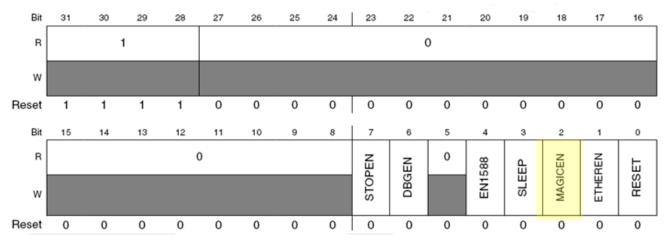

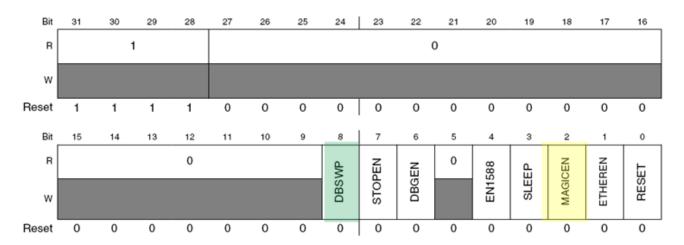

### 3.3.1 Memory Map Comparison

There are two new registers in the SMC module. They are SMC\_VLLSCTRL and SMC\_PMSTAT. The two SRS registers that are in the MC have been moved to the RCM. The changes to this register will be discussed in the RCM section.

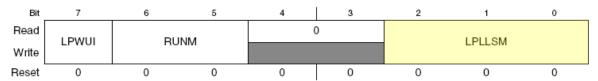

Address: MC\_PMPROT is 4007\_E000h base + 2h offset = 4007\_E002h

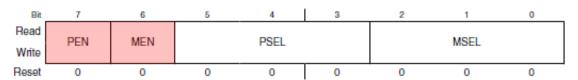

Figure 3. MC\_PMPROT

Address: SMC\_PMPROT is 4007\_E000h base + 0h offset = 4007\_E000h

Figure 4. SMC\_PMPROT

#### Changed bit/field names:

- ALLS—Moved to bit 3

- AVLLS3—AVLLS

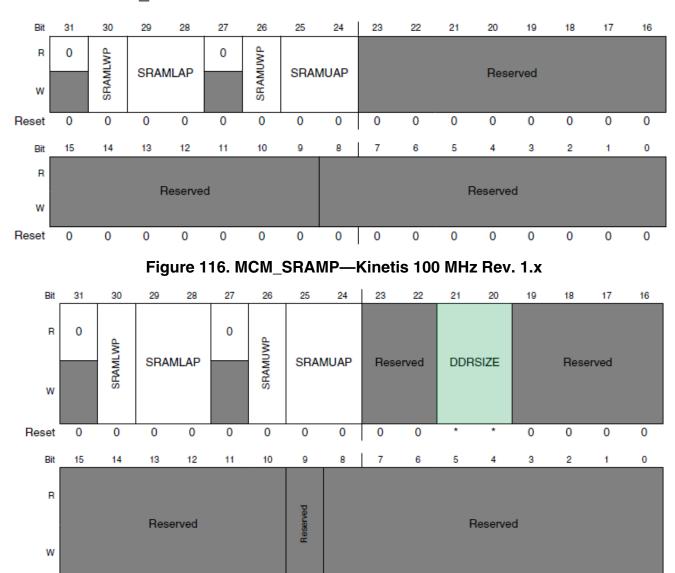

- AVLLS2—AVLLS

- AVLLS1—AVLLS

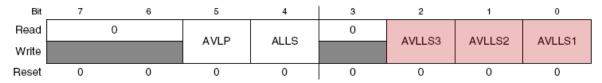

Address: MC\_PMCTRL is 4007\_E000h base + 3h offset = 4007\_E003h

Figure 5. MC\_PMCTRL

Address: SMC\_PMCTRL is 4007\_E000h base + 1h offset = 4007\_E001h

Figure 6. SMC\_PMCTRL

#### Changed bit/field names:

- STOPA—New bit in the SMC

- LPLLSM—VLLSM, moves to new register SMC\_VLLSSCTRL

- STOPM—New bit field in the SMC

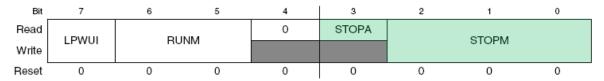

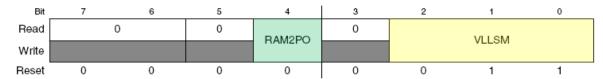

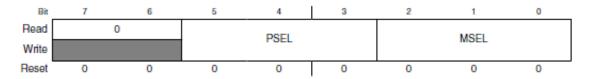

Address: SMC\_VLLSCTRL is 4007\_E000h base + 2h offset = 4007\_E002h

Figure 7. SMC\_VLLCTRL

#### Changed bit/field names:

- RAM2PO—New bit in the SMC

- VLLSM—New bit field in the SMC

Address: SMC\_PMSTAT is 4007\_E000h base + 3h offset = 4007\_E003h

Figure 8. SCM\_PMSTAT

#### Changed bit/field names:

PMSTAT—New bit field in the SMC

### 3.3.2 Software impact

**General impact:** Any register reference to the MC register will need to change the RCM and SMC register names. The SRS registers are in the RCM. The prefix for the mode control functions changes from MC to SMC.

**SMC\_PMPROT:** The SMC\_PMPROT register is still a one-time-write after reset type of register. The protection of entry into the VLLSx low-power modes is controlled by one bit in the SMC. Software will need to write to the PMPROT in the initialization code to allow only the desired low-power modes. The address changes of the registers and the location change of the ALLS bit is handled by the header file definitions for the SMC.

#### **SMC\_PMCTRL** and **SMC\_VLLSCTRL**:

The SMC\_PMCTRL and SMC\_VLLSCTRL register control mode entry and exit. Software will need to change the values written to these registers to accomplish the functions done in the MC\_PMCTRL register.

A read of the new bit STOPA in the SMC\_PMCTRL register will indicate that an interrupt or reset occurred during a stop entry sequence and the SMC can abort the transition early and return to Run mode without completely entering the stop mode. See the reference manual SMC functional description for more information.

The new STOPM bit field has the following meaning:

| 2-0<br>STOPM | Stop Mode Control  When written, this field controls entry into the selected stop mode when sleep-now or sleep-on-exit mode is entered with SLEEPDEEP=1. Writes to this field are blocked if the protection level has not been enabled using the PMPROT register. After any system reset, this field is cleared by hardware on any successful write to the PMPROT register. |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | NOTE: When set to VLLSx, the VLLSM bits in the VLLSCTRL register is used to further select the particular VLLS sub-mode which will be entered.                                                                                                                                                                                                                              |

|              | NOTE:                                                                                                                                                                                                                                                                                                                                                                       |

|              | 000 Normal stop (STOP) 001 Reserved 010 Very low power stop (VLPS) 011 Low leakage stop (LLS) 100 Very low leakage stop (VLLSx) 101 Reserved 110 Reserved 111 Reserved                                                                                                                                                                                                      |

**Low-Power Mode Entry Change:** If a low-power mode of Stop, VLPS, or LLS is desired, the PMPROT bit must first be set and the a write to STOPM is needed. If one of the VLLSx modes is desired, one additional write to the VLLSM bits in the SMC\_VLLSCTRL is needed.

| 2–0<br>VLLSM | VLLS Mode Control                                               |

|--------------|-----------------------------------------------------------------|

| VLLSIVI      | This field controls which VLLS sub-mode to enter if STOPM=VLLS. |

|              | 000 Reserved                                                    |

|              | 001 VLLS1                                                       |

|              | 010 VLLS2                                                       |

|              | 011 VLLS3                                                       |

|              | 100 Reserved                                                    |

|              | 101 Reserved                                                    |

|              | 110 Reserved                                                    |

|              | 111 Reserved                                                    |

#### **SMC PMSTAT**

A read of this new register in the SMC will give you the current low-power mode.

### 3.3.3 Hardware impact

#### RAM power in VLLS2 mode

A new bit in the SCM\_VLLSCTRL register—RAM2PO—controls whether the RAM partition 2 is powered or not while in VLLS2 low-power mode.

#### VLPR and VLPW now supported

With the SMC the mode VLPR and VLPW are now supported. The way you enter the modes is the same between revisions.

#### **Debug in low-power modes**

Please note that the SMC allows debug operation in Run, Wait, VLPR, or VLPW in the same way as in the MC. The debugger handles attempts to enter Stop and VLPS by entering an emulated stop state. See the reference manual SMC functional description for more information.

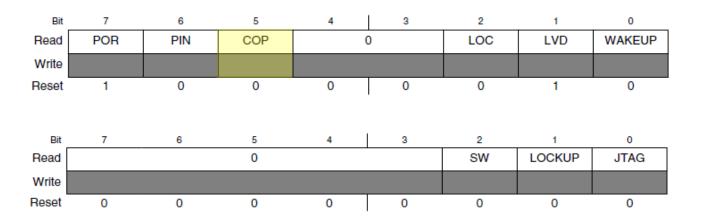

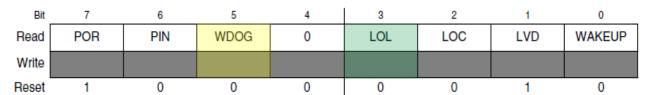

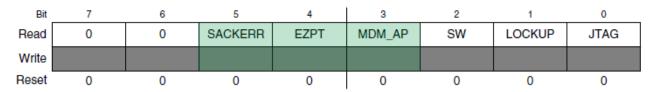

### 3.4 Reset Controller Module (RCM)

The RCM has been updated; however, not all of the functions that are in this module are new. The SRS registers that were in the MC previously are now in the RCM. The SRS register has been revised.

### 3.4.1 Memory map comparison

Figure 9. SRS Register High and Low (MC\_SRSx)

Figure 10. SRS Register 0 (RCM\_SRS0)

Figure 11. SRS Register 1 (RCM\_SRS1)

#### Changed bit/field names:

• COP → WDOG - field name change

#### New bit/field names:

- LOL

- SACKERR

- EZPT

- MDM\_AP

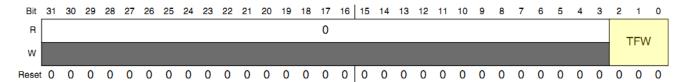

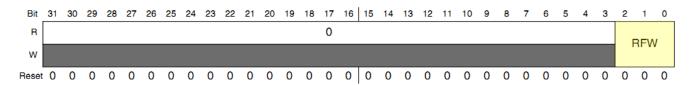

Figure 12. Reset Pin Filter Control Register (RCM\_RPFC)—New register

Figure 13. Reset Pin Filter Width Register (RCM RFPW)—New register

### 3.4.2 Software impact

Any references to MC\_SRSH and MC\_SRSL will need to be changed to the new register names. Software that decoded the reset information in these two registers will need to account for the new bits added in each of the two registers.

If you want to use the new digital filter function of the RCM, please refer to the reference manual sections Reset and Boot and Reset Control Module.

### 3.4.3 Hardware impact

There are four additional sources of reset that have been added to the RCM.

The Reset pin input can be digitally filtered with either the LPO clock or the bus clock. The bus clock filter value is selectable in the RCM\_RFPW register.

#### 3.5 **LLWU**

The Low Leakage Wakeup Unit (LLWU) controls the exit from LLS and VLLSx power modes. The functionality of the LLWU is linked closely with the Power Management Controller (PMC), the System Mode Controller (SMC), and the new Reset Control Module (RCM).

### 3.5.1 Memory map comparison

There are three new registers in the LLWU module. They are the LLWU\_FILT1, LLWU\_FILT2, and LLWU\_RST registers. One register has been removed from Rev. 2 of the LLWU, the LLWU\_CS.

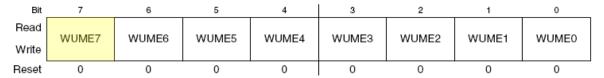

Address: LLWU\_ME is 4007\_C000h base + 4h offset = 4007\_C004h

Figure 14. LLWU\_ME Register

#### Changed bit/field names:

WUME7—Connected to RTC Seconds enable

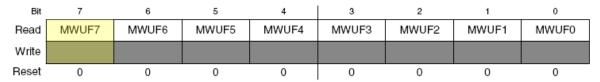

Address: LLWU\_F3 is 4007\_C000h base + 7h offset = 4007\_C007h

Figure 15. LLWU F3 Register

#### Changed bit/field names:

WUMF7—Connected to RTC Seconds interrupt

The RTC seconds flag is connected to bit 7 of the corresponding LLWU flag register.

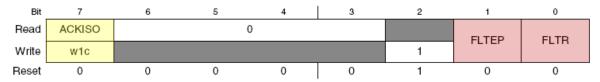

Address: LLWU\_CS is 4007\_C000h base + 8h offset = 4007\_C008h

Figure 16. LLWU CS—Rev. 1 removed

Kinetis 100 MHz Rev 1.x to 120 MHz Migration Guide, Rev. 1.0, March 2013

#### Changed bit/field names:

- ACKISO—Moved to bit 3 of the PMC\_REGSC register

- FLTEP—Filter functionality changed

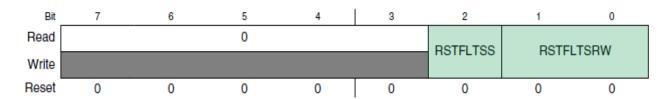

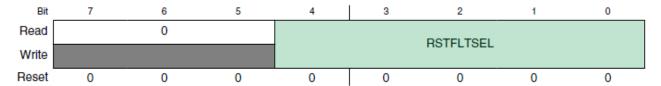

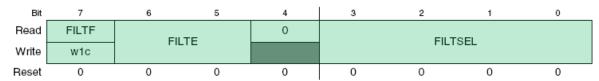

Address: LLWU\_FILT1 is 4007\_C000h base + 8h offset = 4007\_C008h

Figure 17. LLWU\_FILT1—New register Rev. 2.x

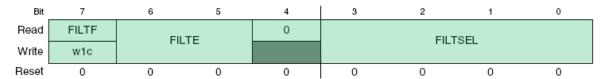

Address: LLWU\_FILT2 is 4007\_C000h base + 9h offset = 4007\_C009h

Figure 18. LLWU\_FILT2—New register Rev. 2.x

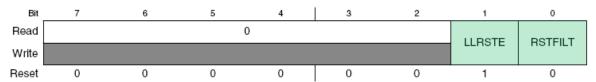

Address: LLWU\_RST is 4007\_C000h base + Ah offset = 4007\_C00Ah

Figure 19. LLWU\_RST—New register Rev. 2.x

The functionality of the LLRSTE and RSTFILT bits is enabled when there is no dedicated Reset pin. Kinetis parts have a dedicated Reset pin; therefore, these bits do not change the operation of the Reset pin.

### 3.5.2 Software impact

#### **LLWU Module Enable and Flag**

Not obvious in the register description for Rev. 2 of the LLWU is the fact that the RTC Seconds module interrupt is connected to bit 7 of the LLWU\_ME register [WUME7]. The RTC seconds flag is connected to bit 7 [MWUF7] of the corresponding LLWU flag register LLWU\_F3.

#### LLWU pin and reset filters

Register LLWU\_FILT1, LLWU\_FILT2, and LLWU\_RST control the filter functionality of the LLWU. See the reference manual LLWU register definition and functional description for more information.

#### **ACKISO** move

The ACKISO bit is now in the PMC module registers. Software will need to re-target the write-1-to-clear operation to the new register. This is an important bit for users who are waking up from VLLSx modes through the reset flow. A read of the ACKISO bit indicates whether the I/O pads and the system oscillator(s) are in a latched state. Care should be used in not clearing this bit too early. You should re-initialize the I/O and the oscillator before writing the ACKISO or there might be a glitch on the pins or in the oscillator startup.

### 3.5.3 Hardware impact

**LLWU\_M7IF** → **RTC seconds:** In Rev. 2 of the LLWU, Module Wakeup bit 7 is connected to the output of the RTC seconds interrupt. This allows the RTC seconds output to wake up the MCU from LLS and VLLSx low-power modes.

**LLWU pin filter function:** The functionality of the pin filter in the LLWU module has changed. In the original LLWU, all of the LLWU inputs are fed into one pin filter circuitry resulting in a single wakeup flag. In the new revision, only two preselected LLWU inputs are fed into two pin filter circuits resulting in two possible filtered pin wakeup flags.

The newer version of the LLWU has filter and pin enable for the reset pin to wake up the MCU from LLS and VLLSx low power modes. For devices like Kinetis that have a dedicated Reset pin, the wakeup from LLS and VLLSx modes is always enabled and these bits do not enable or disable the Reset pin as a wakeup source in low-power modes.

#### 3.6 RNG-B to RNG-A

Kinetis 100 MHz 1.x versions use random number generator version B (RNG-B) while the latest versions of the Kinetis family use random number generator version A (RNG-A). While these two versions are radically different, the migration is surprisingly simple. This section details the differences between the two versions and describes the necessary changes to your Kinetis setup to ensure a smooth transition from RNG-B to RNG-A.

#### 3.6.1 RNG-A vs. RNG-B

The RNG-B variant is a cryptographically strong random number generator with three distinctive features:

- National Institute of Standards and Technology (NIST)-approved pseudo-random number generator (http://csrc.nist.gov)

- Inclusion of the key generation algorithm defined in the Digital Signature Standard (http://www.itl.nist.gov/fipspubs/fip186.htm)

- Integrated entropy sources capable of providing the PRNG with entropy for its seed

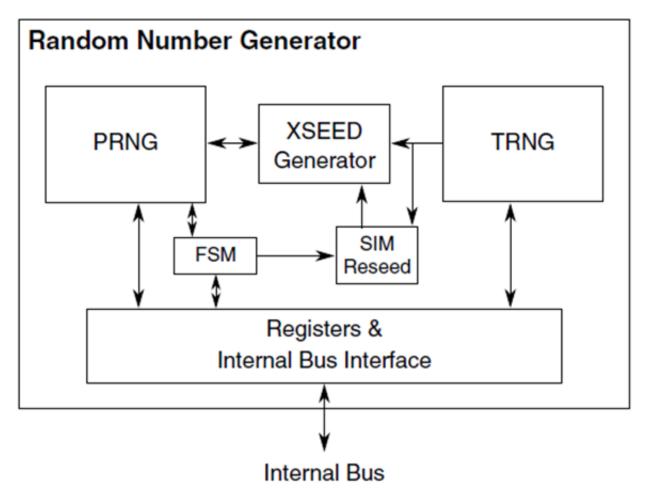

RNG-B uses a true random number generator module (TRNG) to add entropy to a register from which the pseudo-random number generator is seeded. See below for a detailed block diagram of the RNG-B module.

Figure 20. Random number generator

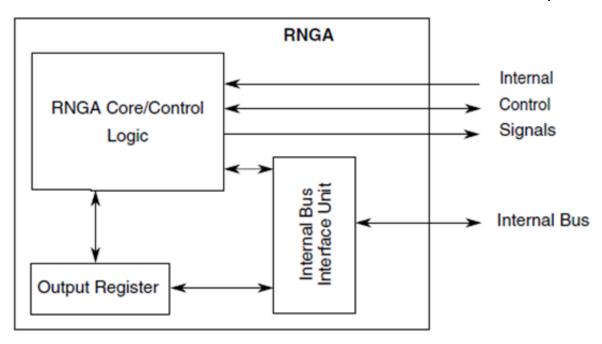

The RNG-A variant is simply a pseudo-random number generator. This module is less bulky and less complex than the RNG-B variant. The RNG-A block diagram is shown in the block diagram below.

Figure 21. RNG-A block diagram

There is no known cryptographic proof showing that this is a secure method of generating random data. Therefore, it is highly recommended that the random data produced by this module be used as an input seed to a NIST-approved (based on DES or SHA-1) pseudo-random number generator as defined in NIST Fips Pub 186-2 Appendix 3 and NIST Fips Pub SP 800-90.

Though these modules are very different internally, operationally they are very similar. The RNG-A module does not allow for manual seeding. Thus, only the automatic operation algorithms will be compared here. The two different initialization and operation modes are displayed below.

Table 3. Initialization and operation algorithms comparison

| RNG-A                                                                                                                                                                                                                                                                                                                                    | RNG-B (Automatic)                                                                                                                                                                                                                                                                                                                                                                                                         | RNG-B (Manual)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ol> <li>Reset/initialize</li> <li>Write to the RNGA Control Register and set the Interrupt Mask (INTM), High Assurance (HA), and GO bits.</li> <li>Poll the RNGA Status Register for RNGA Output Register level.</li> <li>Read available random data from the RNGA Output Register.</li> <li>Repeat steps 3 and 4 as needed.</li> </ol> | <ol> <li>Reset/initialize.</li> <li>Write to the RNG_CR to set up the RNGB for automatic seeding and the desired functionality.</li> <li>Wait for interrupt to indicate completion of first seed.</li> <li>Poll RNG_SR for FIFO level.</li> <li>Read available random data from output FIFO.</li> <li>Repeat steps 4 and 5 as needed. Automatic seeding occurs when necessary and is transparent to operation.</li> </ol> | <ol> <li>Reset/initialize.</li> <li>Write to the RNG_CR to set up the desired functionality.</li> <li>Write to RNG_CMD register to run self-test or seed generation.</li> <li>Wait for interrupt to indicate completion of the requested operation(s).</li> <li>Repeat steps 3 and 4 if seed generation is not complete.</li> <li>Poll RNG_SR for FIFO level.</li> <li>Read available random data from output FIFO.</li> <li>Repeat steps 6 and 7 as needed, until 2<sup>20</sup> words have been generated.</li> <li>Write to RNG_CMD to run seed mode.</li> <li>Repeat steps 4 through 9.</li> </ol> |

### 3.6.2 Memory map comparison

The RNG-A and RNG-B modules share all of the registers that are present in the RNG-A module with the exception of the entropy register. Therefore, migration to the RNG-A module requires that you remove some code and change the values written to the registers that are shared.

Though they may share registers, the registers are not located in the same memory locations. Therefore, it is important to update your system with the latest Freescale-provided header files for your system to work correctly.

The changes in the memory map locations are displayed in the figure below. Changes in the reset values for these registers are discussed in the specific register comparisons.

| Memory map comparison |                     |         |           |        |  |  |

|-----------------------|---------------------|---------|-----------|--------|--|--|

|                       | RNG-B Location Name |         |           | RNG-A  |  |  |

|                       |                     |         | Location  | Name   |  |  |

| Control Register      | 400A_0008           | RNG_CR  | 400A_0000 | RNG_CR |  |  |

| Status Register       | 400A_000C           | RNG_SR  | 400A_0004 | RNG_SR |  |  |

| Output Register       | 400A_0014           | RNG_OUT | 400A_000C | RNG_OR |  |  |

| Entropy Register      | N/A                 | N/A     | 400A_0008 | RNG_ER |  |  |

| Command Register      | 400A_0004           | RNG_CMD | N/A       | N/A    |  |  |

| Error Status Register | 400A_0010           | RNG_ESR | N/A       | N/A    |  |  |

| Version Register      | 400A_0000           | RNG_VER | N/A       | N/A    |  |  |

In addition to the changes in location, there have also been changes to the register structures and some reset values. The control register structure of RNG-A and RNG-B is shown below. Note that the register structures are completely different.

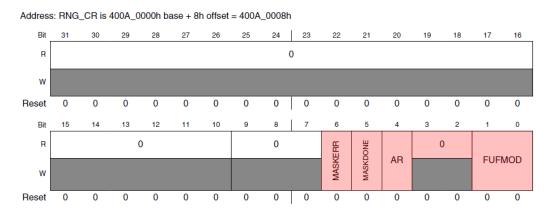

Figure 22. RNG-B module RNG\_CR

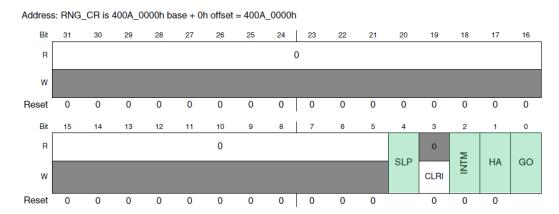

Figure 23. RNG-A module RNG\_CR

#### Deleted bit fields:

- MASKERR

- MASKDONE

- AR

- FUFMOD

#### Added bit fields:

- SLP: Setting this bit puts the RNG module in Sleep mode; clearing this bit awakens it.

- CLRI: Setting this bit clears the error interrupt flag.

- INTM: Setting this bit enables RNG interrupts; clearing it disables them.

- HA: Enables the security violation bit in the RNG register. Reads of the RNG register while this bit is set are not permitted.

- GO: RNG register is loaded with random data.

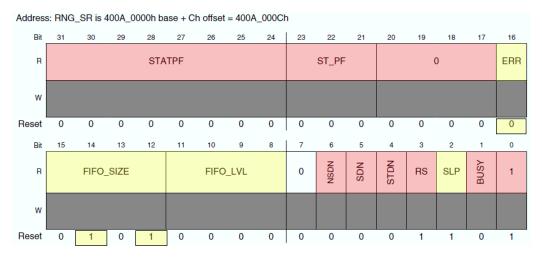

Figure 24. RNG-B module RNG\_SR

Address: RNG\_ESR is 400A\_0000h base + 10h offset = 400A\_0010h

Figure 25. RNG-B module RNG\_ESR

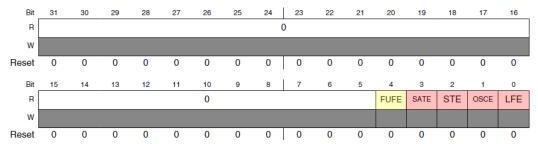

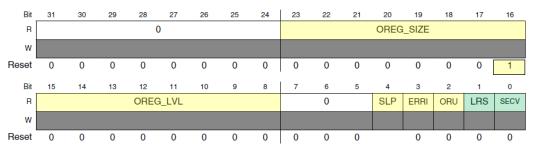

Address: RNG\_SR is 400A\_0000h base + 4h offset = 400A\_0004h

Figure 26. RNG-A module RNG\_SR

#### Added bit fields:

- SECV: Signals that a security violation has occurred if set. No security violation has occurred if cleared.

- LRS: When set, the last read status bit indicates that the last read was performed while the output register was empty (underflow condition).

#### Changed bit fields:

- OREG\_SIZE: This is an 8-bit integer field that indicates the size of the output register and has been renamed from FIFO\_SIZE in the RNG-B variant.

- OREG\_LVL: This bit indicates that a random word is available in the output register. Only two values are possible (0b00000001 or 0b00000000). This bit was renamed from FIFO\_LVL in the RNG-B variant.

- SLP: Indicates that the RNG module is in Sleep mode when set. This bit was moved from bit 2 (in the RNG-B variant) to bit 4.

- ERRI: When set, this bit indicates that the output register was read while empty. This bit was moved from bit 16 (in the RNG-B variant) to bit 3.

- ORU: When set, this bit indicates that the output register was read while empty since the last read of the status register. This bit was moved from bit 4 of the ESR register (in the RNG-B variant) to bit 2.

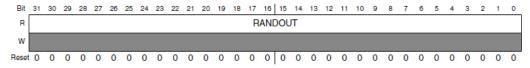

Address: RNG\_OUT is 400A\_0000h base + 14h offset = 400A\_0014h

Figure 27. RNG-B module RNG\_OUT

Figure 28. RNG-A module RNG\_OR

The output register is simply a 32-bit register that holds the resultant random number once a random number has been generated and, thus, the structure has not been changed. The register has been renamed as shown below.

Figure 29. RNG-A module RNG\_ER

The RNG-A module allows you to add entropy to the random number generation process. This is done by writing a value to the write-only entropy register. Sources of entropy that may feed the entropy registers are:

- Current time (highest precision possible)

- Mouse and/or keyboard motions

- Other random number generators

### 3.6.3 Software impact

Freescale Semiconductor will provide customers affected by this migration with new header and linker files, making the migration to the new RNG-A module as seamless as possible. It is important to remember (as previously mentioned in this document) that the RNG-A algorithm does not produce a cryptographically strong random number. If your current software setup relies on a cryptographically strong random number generator for your cryptographic algorithm, you will need NIST-approved support software to generate a cryptographically strong random number to feed into your current software solution. In addition, it is recommended that you use the entropy register of the RNG-A module to add extra entropy to your random number generation process.

There are two general cases for RNG-B to RNG-A migration: either a manually seeded RNG-B algorithm is being implemented or an automatically seeded RNG-B algorithm is being implemented. The manually seeded RNG-B implementation is examined first below.

### 3.6.4 Impact when using manual seeding algorithm

If you are using manual seeding in your code, you will need to rewrite your code based on the automatic seeding algorithm of RNG-A, as RNG-A provides no manual seeding option. The two algorithms are presented below in a side-by-side comparison highlighting the similarities in the algorithms

| RNG-B Manual Algorithm                                 | RNG-A Algorithm                                                                             |

|--------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Reset/Initialize                                       | Reset/Initialize                                                                            |

| Write to the RNG_CR to setup the desired functionality | Write to the RNGA_CR and set the Interrupt Mask (INTM),<br>High Assurance (HA), and GO bits |

Table continues on the next page...

| RNG-B Manual Algorithm                                                           | RNG-A Algorithm                                   |

|----------------------------------------------------------------------------------|---------------------------------------------------|

| Write to RNG_CMD register to run self-test or seed generation.                   |                                                   |

| Wait for interrupt to indicate completion of the requested operation(s).         |                                                   |

| Repeat steps 3-4 if seed generation is not complete.                             |                                                   |

| Poll RNG_SR for FIFO level.                                                      | Poll RNG_SR for Output register level.            |

| Read available random data from output FIFO.                                     | Read the available data from the Output Register. |

| Repeat steps 6 and 7 as needed, until 2 <sup>20</sup> words have been generated. |                                                   |

| Write to RNG_CMD to run seed mode                                                |                                                   |

| Repeat steps 4 through 9.                                                        | Repeat steps 3 and 4.                             |

As can be seen from the comparison above, when switching to the RNG-A algorithm, steps 3, 4, 5, and 9 may be deleted from your code project. If you will not be using the Freescale-provided header and linker files, remember that, when writing to the RNGA\_CR register, you will need to update the value that is written to the CR register. Also, when polling the SR register, you will to poll bits 8–15 (instead of just 8–11).

### 3.6.5 Impact when using automatic seeding algorithm

The algorithmic difference between RNG-A and RNG-B are minimal when implementing the automatic seeding functionality. Observe the chart comparison below.

| RNG-B Manual Algorithm                                   | RNG-A Manual Algorithm                                                                   |

|----------------------------------------------------------|------------------------------------------------------------------------------------------|

| Reset/initialize                                         | Reset/initialize                                                                         |

| Write to the RNG_CR to set up the desired functionality  | Write to the RNGA_CR and set the Interrupt Mask (INTM), High Assurance (HA), and GO bits |

| Wait for interrupt to indicate completion of first seed. |                                                                                          |

| Poll RNG_SR for FIFO level.                              | Poll RNG_SR for output register level.                                                   |

| Read available random data from output FIFO.             | Read the available data from the output register.                                        |

| Repeat steps 4 through 9.                                | Repeat steps 3 and 4.                                                                    |

If you are using the automatic seeding algorithm, you will simply need to remove your code related to the RNG-B seeding interrupt, adjusting the value written to the control register to be the proper value for RNG-A, and adjusting your code to read from the correct output level register. To simplify the output register reads, it is recommended that you insert a define statement converting the output register name of RNG-B to the output register name of the RNG-A output register.

(#define RNG\_OUT RNG\_OR).

### 3.6.6 Hardware impact

No hardware impact.

### 3.7 SSI to SAI

The Kinetis 100 MHz Rev. 1.x devices used the SSI module to provide I2S capability, but newer Kinetis devices use the SAI module. While the modules have similar functionality, there are many differences.

In addition to changing from the SSI to the SAI, the 120MHz devices have up to two instantiations of the SAI while the 100MHz devices only had one.

#### 3.7.1 Features

Even though the register map and bit definitions of the SAI module are quite different from the SSI module, the main features are still the same. SAI supports full duplex synchronous serial interfaces with frame sync such as I2S, TDM, AC97, codec, and DSP interfaces. However, in the movement from the SSI to the SAI module, some features have been added and some have been removed:

Following is a list of what has been removed on the SAI module:

- No option to disable transmit and receive frame sync separately. Once TE or RE enabled, frame sync generates, it can only be disabled by clearing TE or RE.

- No option to output oversampling clock on RX bit clock.

- No separate bits to control whether SAI operates under I2S mode or network mode; it all depends on how you

configure the frame sync size.

- No longer supports gated clock mode.

- No hardware support for AC97, though AC97 can still be supported with software if configured for 13 or more words per frame.

- No support for separate start-of-frame flag and start-of-last-unmasked-word-in-frame-flag. These have been replaced with single flag to represent the start of a word in a frame.

- No option to disable TX or RX FIFOs. They are always enabled.

- No support for separate left/right FIFOs. Instead there are two separate pins for TX and RX, each associated with its own FIFO.

- No option to select MSB aligned or LSB aligned

- No bits to represent FIFO entry counts. Instead, a write and read FIFO pointer is used to represent current FIFO entry and can be used to tell whether the FIFO is full or empty.

Below is a list of what is new on the SAI module

- Support for Stop mode operation

- Support for Debug mode operation

- Support for 32-bit transfers

- Added option to enable and disable bit clock separately

- Added frame sync error flag

- Added TX FIFO empty or RX FIFO full flag to allow trigger interrupt and DMA, apart from the TX and RX FIFO watermark trigger

- · One additional TX and RX data channel

- SAI master clock select and divide registers relocated to SAI's own memory space. (For Kinetis Rev. 1.x, these were located in the SIM module.)

### 3.7.2 Memory map comparison

Table 7 provides a memory map comparison of the SSI and SAI modules. Since the memory map and the registers' intended functions have changed significantly in some cases, the table uses the following conventions:

- 1. Registers that implement similar functions are listed in the same row; for example, I2S0\_TX0 corresponds to I2S0\_TDR0.

- 2. If there is an SSI module register whose function needs to be implemented with more than one register, that one register map is merged so that it corresponds to all those related registers in the SAI module; for example, I2S0\_TCR's function needs to be implemented with I2S0\_TCR2, I2S0\_TCR3, and I2S0\_TCR4.

- 3. Some of the registers in either the SSI or SAI module do not have a related register in the other module; for example, there is no hardware acceleration support for AC97 on SAI and no related AC97 registers on SAI. In these cases, "N/A" in the associated row indicates that the register is not available.

- 4. For the SSI module, master clock generation needs to configure two registers in the SIM module, while SAI has pulled related registers into its own memory space.

Table 7. Memory map comparison

|                               | S         | SI                           |                                             | SAI       |           |

|-------------------------------|-----------|------------------------------|---------------------------------------------|-----------|-----------|

| I2S transmit data register 0  | 4002_F000 | I2S0_TX0                     | SAI transmit data register 0                | 4002_F020 | I2S0_TDR0 |

| I2S transmit data register 1  | 4002_F004 | I2S0_TX1                     | SAI transmit data register 1                | 4002_F024 | I2S0_TDR1 |

| I2S receive data register 0   | 4002_F008 | I2S0_RX0                     | SAI receive data register 0                 | 4002_F0A0 | I2S0_RDR0 |

| I2S receive data register 1   | 4002_F00C | I2S0_RX1                     | SAI receive data register 1                 | 4002_F0A4 | I2S0_RDR1 |

| I2S control register          | 4002_F010 | I2S0_CR                      | SAI transmit control register               | 4002_F000 | I2S0_TCSR |

|                               |           | SAI receive control register | 4002_F080                                   | I2S0_RCSR |           |

|                               |           |                              | SAI transmit<br>configuration 2<br>register | 4002_F008 | I2S0_TCR2 |

|                               |           |                              | SAI receive<br>configuration 2<br>register  | 4002_F088 | I2S0_RCR2 |

|                               |           |                              | SAI transmit<br>configuration 3<br>register | 4002_F00C | I2S0_TCR3 |

|                               |           |                              | SAI receive<br>configuration 3<br>register  | 4002_F08C | I2S0_RCR3 |

| I2S interrupt status register | 4002_F014 | I2S0_ISR                     | SAI transmit control register               | 4002_F000 | I2S0_TCSR |

|                               |           |                              | SAI receive control register                | 4002_F080 | I2S0_RCSR |

| 2S interrupt enable register  | 4002_F018 | I2S0_IER                     | SAI transmit control register               | 4002_F000 | I2S0_TCSR |

|                               |           |                              | SAI receive control register                | 4002_F080 | I2S0_RCSR |

Table continues on the next page...

### Table 7. Memory map comparison (continued)

|                                           | SSI       |                                            |                                             | SAI       |           |

|-------------------------------------------|-----------|--------------------------------------------|---------------------------------------------|-----------|-----------|

| I2S transmit<br>configuration<br>register | 4002_F01C | I2S0_TCR                                   | SAI transmit<br>configuration 2<br>register | 4002_F008 | I2S0_TCR2 |

|                                           |           |                                            | SAI transmit<br>configuration 3<br>register | 4002_F00C | I2S0_TCR3 |

|                                           |           |                                            | SAI transmit<br>configuration 4<br>register | 4002_F010 | I2S0_TCR4 |

| I2S receive configuration register        | 4002_F020 | I2S0_RCR                                   | SAI receive<br>configuration 2<br>register  | 4002_F088 | I2S0_RCR2 |

|                                           |           | SAI receive<br>configuration 3<br>register | 4002_F08C                                   | I2S0_RCR3 |           |

|                                           |           | SAI receive<br>configuration 4<br>register | 4002_F090                                   | I2S0_RCR4 |           |

| I2S transmit clock control register       | 4002_F024 | I2S0_TCCR                                  | SAI transmit<br>configuration 2<br>register | 4002_F008 | I2S0_TCR2 |

|                                           |           |                                            | SAI transmit<br>configuration 4<br>register | 4002_F010 | I2S0_TCR4 |

|                                           |           |                                            | SAI transmit<br>configuration 5<br>register | 4002_F014 | I2S0_TCR5 |

| I2S receive clock control register        | 4002_F028 | I2S0_RCCR                                  | SAI receive<br>configuration 2<br>register  | 4002_F088 | I2S0_RCR2 |

|                                           |           |                                            | SAI receive<br>configuration 4<br>register  | 4002_F090 | I2S0_RCR4 |

|                                           |           |                                            | SAI receive<br>configuration 5<br>register  | 4002_F094 | I2S0_RCR5 |

Table continues on the next page...

Table 7. Memory map comparison (continued)

| SSI                                   |           |             | SAI                                         |           |           |

|---------------------------------------|-----------|-------------|---------------------------------------------|-----------|-----------|

| I2S FIFO control/<br>status register  | 4002_F02C | I2S0_FCSR   | SAI transmit<br>configuration 1<br>register | 4002_F004 | I2S0_TCR1 |

|                                       |           |             | SAI receive<br>configuration 1<br>register  | 4002_F084 | I2S0_RCR1 |

|                                       |           |             | SAI transmit FIFO<br>0 register             | 4002_F040 | I2S0_TFR0 |

|                                       |           |             | SAI transmit FIFO<br>1 register             | 4002_F044 | I2S0_TFR1 |

|                                       |           |             | SAI receive FIFO 0 register                 | 4002_F0C0 | I2S0_RFR0 |

|                                       |           |             | SAI receive FIFO 1 register                 | 4002_F0C4 | I2S0_RFR1 |

| I2S0 transmit time slot mask register | 4002_F048 | I2S0_TMSK   | SAI transmit mask register                  | 4002_F060 | I2S0_TMR  |

| I2S0 receive time slot mask register  | 4002_F04C | I2S0_RMSK   | SAI receive mask register                   | 4002_F0E0 | I2S0_RMR  |

| I2S AC97<br>command data<br>register  | 4002_F040 | I2S0_ACDAT  | N/A                                         | N/A       | N/A       |

| I2S AC97 tag<br>register              | 4002_F044 | I2S0_ATAG   | N/A                                         | N/A       | N/A       |

| I2S AC97 Channel status register      | 4002_F050 | I2S0_ACCST  | N/A                                         | N/A       | N/A       |

| I2S AC97 channel enable register      | 4002_F054 | I2S0_ACCEN  | N/A                                         | N/A       | N/A       |

| I2S AC97 channel disable register     | 4002_F058 | I2S0_ACCDIS | N/A                                         | N/A       | N/A       |

| System option register 2              | 4004_8004 | SIM_SOPT2   | SAI MCLK control register                   | 4002_F100 | I2S0_MCR  |

| System clock divider register 2       | 4004_8048 | SIM_CLKDIV2 | SAI MCLK divider register                   | 4002_F014 | I2S0_MDR  |

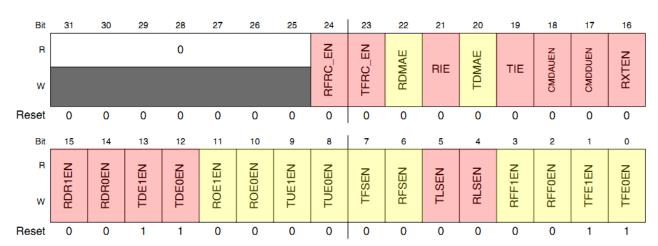

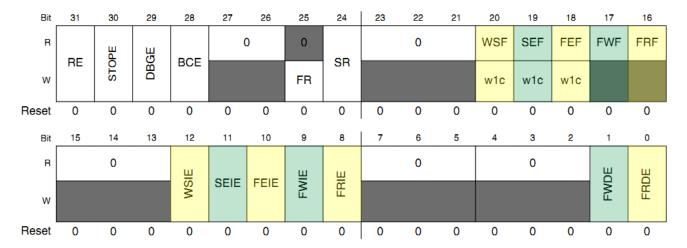

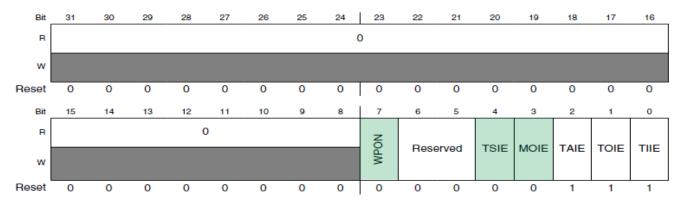

### 3.7.2.1 Control register

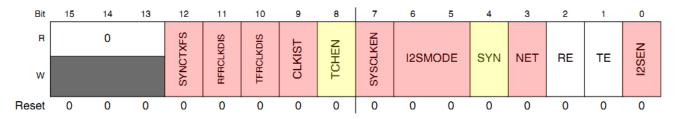

Figure 30. I2S0\_CR-SSI

Figure 31. I2S0\_TCSR-SAI

Figure 32. I2S0\_RCSR-SAI

Figure 33. I2S0\_TCR2 and I2S0\_RCR2-SAI

Figure 34. I2S0\_TCR3-SAI

Figure 35. I2S0\_RCR3-SAI

#### New bits/fields added:

STOPE: Stop Enable

DBGE: Debug Enable

FR: FIFO Reset

SR:Software Reset

#### Changed bits/fields name:

• TCHEN → TCE and RCE

SYN → SYNC

#### Removed bits/fields:

• SYNCTXFS: CR[TE] latch with FS occurrence

• **RFRCLKDIS:** Receive Frame Sync Disable

• TFRCLKDIS: Transmit Frame Sync Disable

• CLKIST: Clock Idle State during I2S Gated Clock Mode

• SYSCLKEN: Oversampling Clock Enable

• I2SMODE: I2S Mode Select

• NET: Network Mode I2SEN: I2S enable

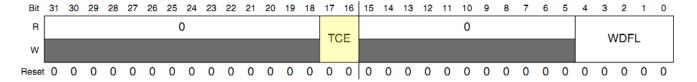

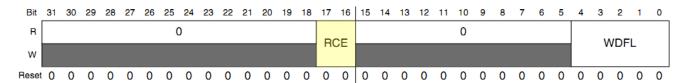

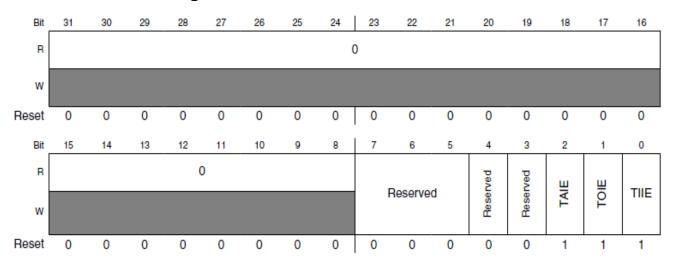

### 3.7.2.2 Interrupt and status enable register

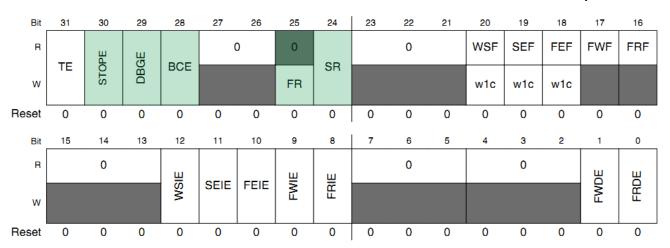

Figure 36. I2S0\_ISR—SSI

Figure 37. I2S0\_IER—SSI

Figure 38. I2SO TCSR—SAI

Figure 39. I2S0\_RCSR—SAI

#### New bits/fields added:

- **SEF:** Sync Error Flag

- FWF: FIFO Warning Flag

- **SEIE:** Sync Error Interrupt Enable

- FWIE: FIFO Warning Interrupt Enable

- FWDE: FIFO Warning DMA Enable

#### Changed bits/fields name:

- ROE1 & ROE0 → RCSR[FEF] (Receive FIFO Error, overrun)

- TUE1 & TUE0 → TCSR[FEF] (Transmit FIFO Error, underrun)

- TFS → TCSR[WSF] (Transmit Frame Sync)

- RFS → RCSR[WSF] (Receive Frame Sync)

- RFF1 & RFF0 → RCSR[FRF] (Receive FIFO Request, received data greater than watermark)

- TFE1 & TFE0 → TCSR[FRF] (Transmit FIFO Request, transmit data less than watermark)

- RDMAE → RCSR[FRDE] (Receive FIFO Request DMA Enable)

- TDMAE → TCSR[FRDE] (Transmit FIFO Request DMA Enable)

- ROE1EN & ROE0EN → RCSR[FEIE]

- TUE1EN & TUE0EN → TCSR[FEIE]

- TFSEN → TCSR[WSIE]

- RFSEN → RCSR[WSIE]

- RFF1EN and RFF0EN → RCSR[FRIE]

- TFE1EN and TFE0EN → TCSR[FRIE]

#### Removed bits/fields:

- TFRC and RFRC: Transmit and Receive Frame Complete

- TLS and RLS: Transmit and Receive Last Time Slot

- RDR1 and RDR0: Receive Data Ready

- TDE1 and TDE0: Transmit Data Empty

- CMDAU: Command Address Register Updated

- CMDDU: Command Data Register Updated

- RXT: Receive Tag Updated

#### Associated interrupt enable bits:

- TFRCEN and RFRCEN,

- TLSEN and RLSEN,

- RDR1EN and RDR0EN,

- · TDE1EN, and

- TDE0E, CMDAUEN, CMDDUEN, RXTEN, RIE, TIE

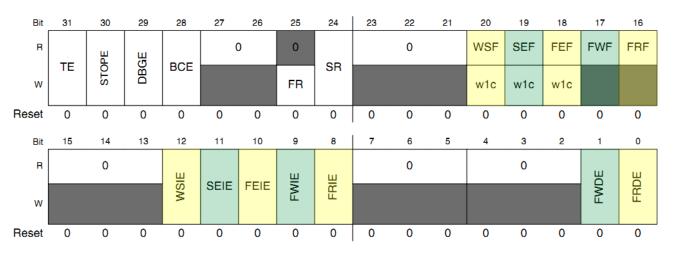

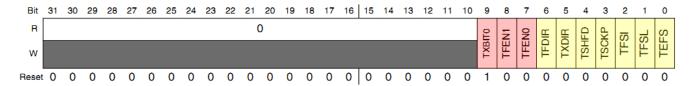

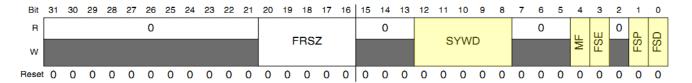

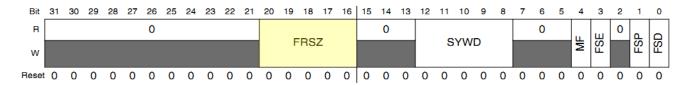

### 3.7.2.3 Transmit and receive configuration register

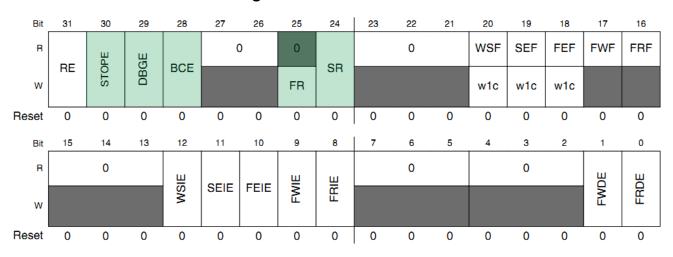

Figure 40. I2S0\_TCR—SSI

Figure 41. I2S0 RCR—SSI

Figure 42. I2S0\_TCR2 and I2S0\_RCR2—SAI

Figure 43. I2S0\_TCR3—SAI

Figure 44. I2S0\_RCR3—SAI

Figure 45. I2S0\_TCR4 and I2S0\_RCR4—SAI

#### New bits/fields added:

- BCS: Bit Clock Swap

- BCI: Bit Clock Input

- WDFL: Configures which word start of word flag is set

#### Changed bits/fields name:

- TSCKP and RSCKP → BCP (Bit Clock Polarity)

- TXDIR and RXDIR → BCD (Bit Clock Direction)

- TFSL and RFSL → SYWD (Frame sync length)

- TSHFD and RSHFD → MF (MSB or LSB transmit first)

- TEFS and REFS → FSE (Frame Sync Early)

- TFSI and RFSI → FSP (Frame Sync Polarity)

- TFDIR and RFDIR → FSD (Frame Sync Direction)

#### Removed bits/fields:

- TXBIT0 and RXBIT0: MSB aligned or LSB aligned

- TFEN0 and TFEN1: Transmit FIFO Enable

- RXEXT: Receive Sign Extension

- RFEN0 and RFEN1: Receive FIFO Enable

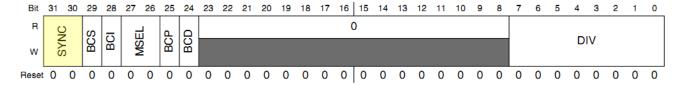

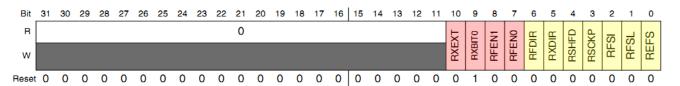

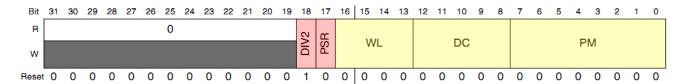

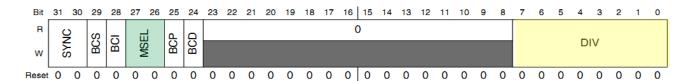

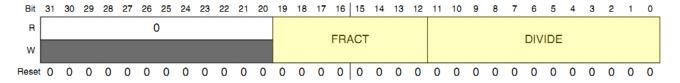

### 3.7.2.4 Transmit and receive clock configuration register

Figure 46. I2S0 TCCR and I2S0 RCCR—SSI

Figure 47. I2S0\_TCR2 and I2S0\_RCR2—SAI

Figure 48. I2S0\_TCR4 and I2S0\_RCR4—SAI

Figure 49. I2S0\_TCR5 and I2S0\_RCR5—SAI

#### New bits/fields added:

- MSEL: Master Clock Select before it is divided down to bit clock

- WNW: Configures number of bits of each word, except the first word in a frame

- FBT: Configures the bit index of the first bit transmitted in each word in a frame

#### Changed bits/fields name:

- DC → FRSZ (number of words in each frame)

- WL --> W0W (number of bits in each word)

- PM → DIV (bit clock prescaler)

#### Removed bits/fields:

- DIV2: Whether or not to divide by 2

- PSR: Prescaler divide by 8

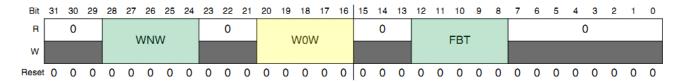

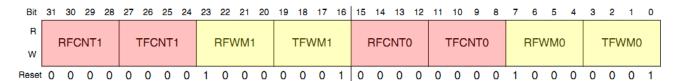

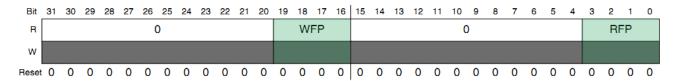

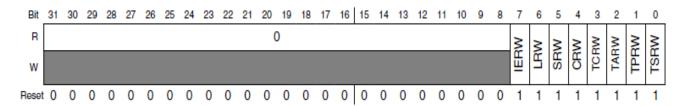

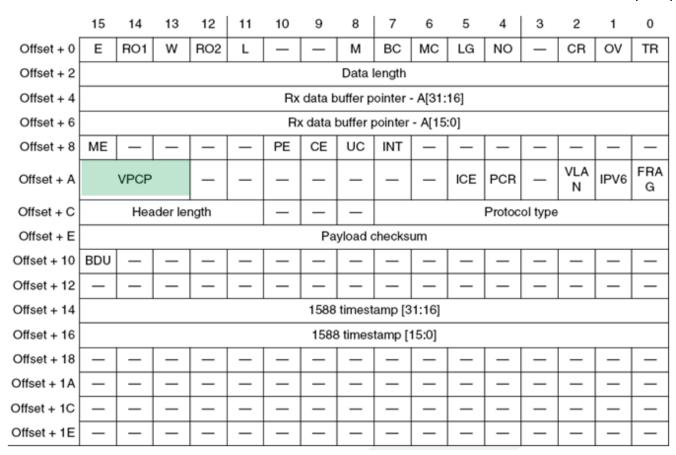

### 3.7.2.5 FIFO control and status register

#### Figure 50. I2S0\_FCSR—SSI

### Figure 51. I2S0\_TCR1—SAI

Figure 52. I2S0\_RCR1—SAI

Figure 53. I2S0 TFR0, I2S0 TFR1, I2S0 RFR0, and I2S0 RFR1—SAI

New bits/fields added:

WFP: Write FIFO PointerRFP: Read FIFO Pointer

#### Changed bits/fields name:

- RFWM0 and RFWM1 → RFW (Receive FIFO Watermark)

- TFWM0 and TFWM1 → TFW (Transmit FIFO Watermark)

#### Removed bits/fields:

- RFCNT0 and RFCNT1: Receive FIFO Counter

- TFCNT0 and TFCNT1: Transmit FIFO Counter

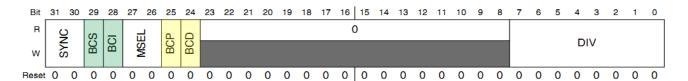

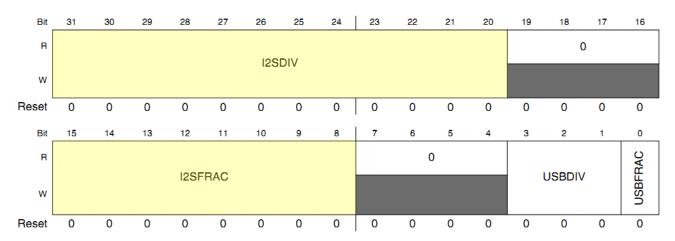

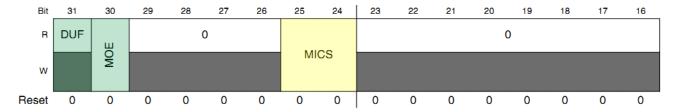

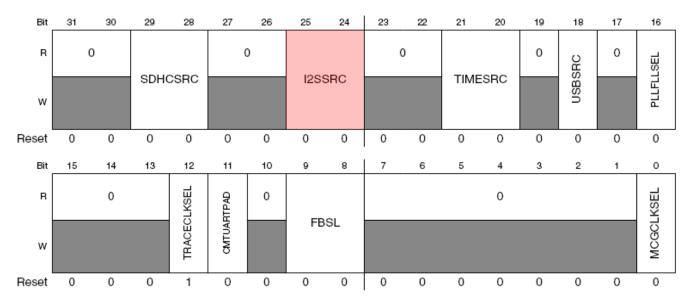

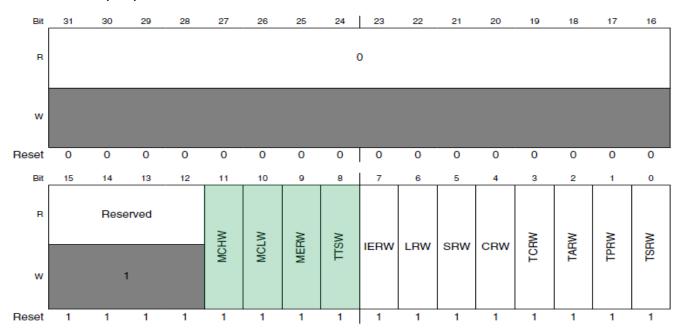

### 3.7.2.6 Master clock generation register

Figure 54. SIM\_SOPT2—SSI

Figure 55. SIM\_CLKDIV2—SSI

Figure 56. I2S0\_MCR—SAI

Figure 57. I2S0\_MDR—SAI

#### New bits/fields added:

• DUF: Divide Update Flag

• MOE: Master Clock Output Enable

#### Changed bits/fields name:

• I2SSRC → MICS (Master Clock Source Select)

• I2SFRAC --> FRACT (Clock Divider Fraction)

### 3.7.3 Software impact

There is not much change in software configuration for the SAI module. Bit clock and frame sync generation, their direction and polarity selection, frame size, and word size setting are the same as for the SSI module. Only the bit naming is different.

With the option to trigger DMA with a TX FIFO empty or RX FIFO full condition, it is easier to program the DMA controller for automatic data transfer by simply programming the total transfer size to be the same as the FIFO depth for the TX and RX FIFO. If instead the FIFO watermark condition is used to trigger DMA, take care to program the DMA controller with a total transfer size less than (FIFO depth – FIFO watermark); otherwise, either TX FIFO is pushed with more data than it can hold, or the RX FIFO is pulled with more data that has been received.

Also note that there is no longer any FIFO count information; instead we have write and read FIFO pointer, so the actual FIFO entry needs to be calculated in your code. Also you need to include logic to determine whether the FIFO is empty or full, and to stop writing data when the FIFO is full or reading data when the FIFO is empty.

### 3.7.4 Hardware impact

There is not much hardware change from the SSI to the SAI. There is one more data channel for TX and RX, so there are I2S0\_TXD0 and I2S0\_TXD1, as well as I2S0\_RXD0 and I2S0\_RXD1. It makes no difference whether you use channel 0 or 1 for transmit or receive data. Since each channel has its own FIFO, each channel can send or receive same or different data and do this at the same time they share the same frame sync and bit clock.

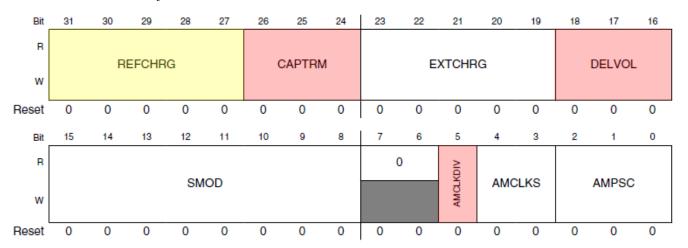

### 3.8 TSI Version 1 to TSI Version 2

This section addresses the specific differences between the TSI module version 1 and version 2. The TSI module has been simplified in the new version to simplify configuration. The current ranges for the oscillator remain the same, but the number of possible configuration values has been reduced by half. Delta voltage configuration was removed; now, a constant delta voltage is used. Threshold registers used to generate an interrupt when capacitance increases have been removed for each channel; only one register was kept for the low-power wake-up channel, exclusively. Linked to this change, the status register for all these thresholds was also removed; now the threshold is only used to wake up. The changes in software needed to adjust for these differences are detailed in the sections below.

### 3.8.1 Memory map comparison

|                                        | Kinetis Rev. 100 MHz 1.x (TSI 1.0) |                | Kinetis 120 MHz (TSI 2.0) |                |

|----------------------------------------|------------------------------------|----------------|---------------------------|----------------|

|                                        | Location                           | Name           | Location                  | Name           |

| General Control and<br>Status Register | 4004_5000                          | TSI0_GENCS     | 4004_5000                 | TSI0_GENCS     |

| SCAN control register                  | 4004_5004                          | TSI0_SCANC     | 4004_5004                 | TSI0_SCANC     |

| Pin enable register                    | 4004_5008                          | TSI0_PEN       | 4004_5008                 | TSI0_PEN       |

| Status Register                        | 4004_500C                          | TSI0_STATUS    | N/A                       | N/A            |

| Counter Registers                      | 4004_5100-<br>4004_511C            | TSI0_CNTRn     | 4004_5100-<br>4004_511C   | TSI0_CNTRn     |

| Channel threshold register(s)          | 4004_5120-<br>4004_515C            | TSI0_THRESHLDn | 4004_5120                 | TSI0_THRESHOLD |

| Wake-up counter                        | N/A                                | N/A            | 4004_500C                 | TSI_WUCNTR     |

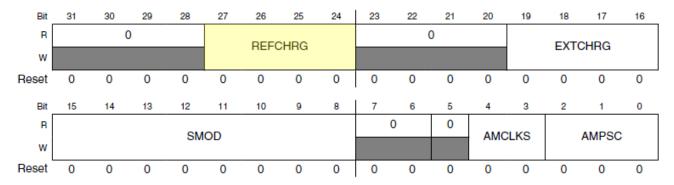

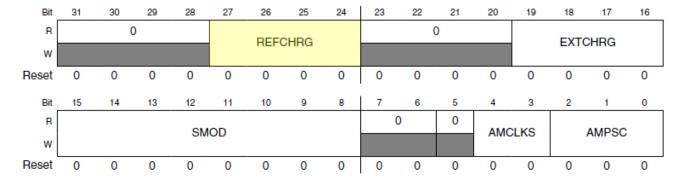

• **GENCS**: No change, but the out-of-range setting is now only operational in low-power modes.

• SCANC: CAPTRM removed (internal cap is now fixed to 1 pF), REFCHRG and EXTCHRG have been scaled down from 5 bits to 4 bits. Change involves reducing the amount of possible current values from 32 to 16. Current range is now from 2 μA to 32 μA in increments of 2. DELVOL eliminated, delta voltage value is now fixed. AMCLKS clock sources changed: bus clock reference was changed for LPOCLK. AMCLKSDIV was also removed because it was only practical with bus clock as reference. Instead of dividing down the clock source, now a slower, lower power source can be used. This reduces overall power consumption of the module. If a slow source is needed, use LPOCLOCK and adjust with AMPSC. If a faster source is needed, use MCGIRCLK or OSCERCLK.

Figure 58. TSI\_SCANC—TSI Rev. 1

Figure 59. TSI\_SCANC—TSI Rev. 2

• TSI\_PEN: No change

• TSI\_WUCNTR: New register, stores the value of the counter for the low power electrode upon wakeup.

• TSI\_STATUS: Removed

Figure 60. TSI\_STATUS (completely removed)

- TSI\_CNTR: No change

- **TSI\_THRESHLDn:** Used to be one threshold register for each electrode; now there is a single threshold register for the selected wakeup electrode because the out-of-range function now only operates in low-power modes.

Figure 61. Single TSI\_THRESHOLD for wakeup instead of separate registers for each channel

### 3.8.2 Software impact

- No delta voltages register because there is no difference between internal delta voltage and the external, so the frequency relationship is not affected. The highest voltage that can be output has been selected as a fixed voltage to increase EMC tolerance. As the change in delta voltages does not affect the relationship between oscillators and thus, the counters, this change does not affect software other than the need to remove the code that configured this register.

- Less current for external and internal oscillators. Touch sensing does not require the level of granularity that was in the first TSI version, so the number of values has been scaled down to 16. It is important to note that this change caused the EXTCHRG and REFCHRG registers to go from 5 to 4 bits, meaning that it is necessary to scale down the value. Make sure to take care of this modification. If the value used previously is now not valid, choose either the next value up or down depending on convenience.

Kinetis 100 MHz Rev 1.x to 120 MHz Migration Guide, Rev. 1.0, March 2013

#### **⊏**manced Modules

- The change of bus clock to LPOCLK for timing reference in AMCLKS means that the prescaler (AMPSC) and modulo (SMOD) need to be adjusted to the LPOCLK, which is a 1 kHz reference. If the other two clock sources were used (MCGIRCLK or OCSERCLK), no change is needed.

- Only one threshold register instead of one for each counter. Consider that the wakeup source can wake up from EOSF (end of scan) or out of range. Because out of range is only available in the low leakage modes (LLS and VLLSx), it is recommended that any of these be used to wake up with TSI. If another mode is needed (like Stop, Low-power Stop, Wait, and so on) and it is needed to wake-up with TSI, then it is important to have a periodic wakeup to check the TSI status. The periodic wakeup can be an external source like RTC or MTIM, or can be the TSI module by configuring the scan time to be very slow (for example, every two or three seconds). This will cause reaction time to be slow, but also lower power.

- Remove references to TSI\_STATUS, as it is no longer available.

- Remove references to the numbered TSI\_THRESHLDn registers; remember now only one TSI\_THRESHOLD register, with the OURGF flag and interrupt, is used for wakeup.

- If the first counter value upon wakeup is needed (from the configured wake-up electrode), use TSI\_WUCNTR to read this value. If not, wait for next scan and read directly from the counter registers.

### 3.8.3 Hardware impact

There is no hardware impact. The signaling and measurement algorithm are the same.

### 4 Enhanced Modules

### 4.1 System Integration Module (SIM)

### 4.1.1 Impacted registers

The SIM's memory map only adds a few registers, but there are many changes to fields within the existing registers as well. There are additions associated with the control of new modules and additional instantiations of modules and new functionality. The function of some fields is slightly modified. Some control functions have been relocated to other modules, and therefore the SIM bits previously associated with these functions are removed.

The table below shows the memory map differences between the original SIM from the Kinetis 100 MHz Rev. 1.x devices and the SIM on the 120 MHz devices. The following sections provide information on the field changes within the registers.

Table 9. Memory map comparison

| Location   | Kinetis 100 MHz Rev. 1.x SIM | Kinetis 120 MHz SIM                           |

|------------|------------------------------|-----------------------------------------------|

| 0x40047004 | N/A                          | SOPT1 Configuration Register (SIM_SOPT1CFG)   |

| 0x40048064 | N/A                          | System Clock Divider Register 3 (SIM_CLKDIV3) |

| 0x40048068 | N/A                          | System Clock Divider Register 4 (SIM_CLKDIV4) |

| 0x4004806C | N/A                          | Misc Control Register (SIM_MCR)               |

# 4.1.1.1 SIM SOPT register changes

The changes to the SIM system options registers (SOPT) are shown below.

<sup>\*</sup> Notes:

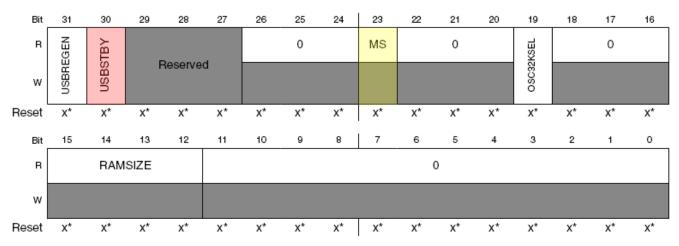

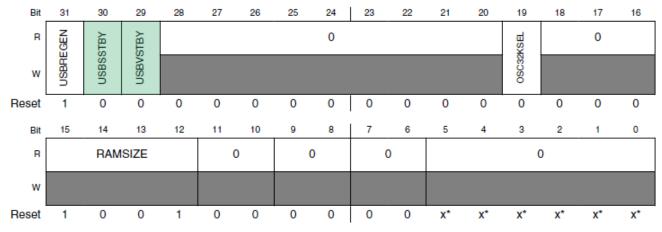

Figure 62. SIM\_SOPT1 register—Kinetis 100 MHz Rev. 1.x

<sup>\*</sup> Notes:

Figure 63. SIM\_SOPT1 register—Kinetis 120 MHz

#### New bits/fields added:

- USBSSTBY

- USBVSTBY

#### Remove bit/field names:

• USBSTBY

#### Changed bit/field names:

• MS → EZP\_MS moved to the RCM\_MR Register

x = Undefined at reset.

x = Undefined at reset.

#### system Integration Module (SIM)

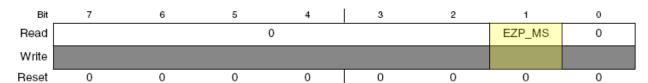

Address: RCM\_MR is 4007\_F000h base + 7h offset = 4007\_F007h

Figure 64. Mode register (RCM\_MR)—Kinetis 120 MHz

Address: SIM\_SOPT1CFG is 4004\_7000h base + 4h offset = 4004\_7004h

Figure 65. SIM\_SOPT1CFG—Kinetis 120 MHz

SIM\_SOPT1CFG is a new register added to control the operation of the USB regulator. Refer to the USB section for more details.

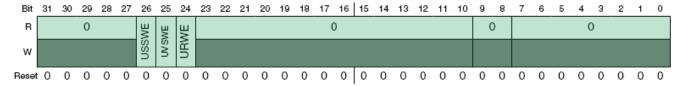

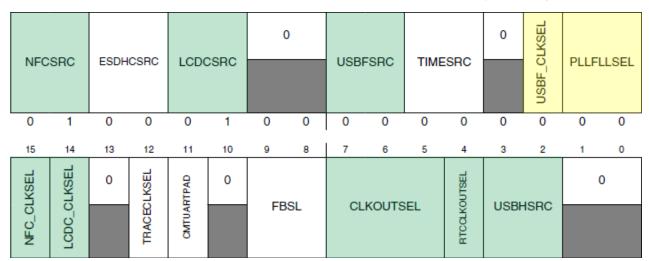

Figure 66. SIM\_SOPT2—Kinetis 100 MHz Rev. 1.x

Figure 67. SIM\_SOPT2—Kinetis 120 MHz

#### New bits/fields added:

- NFCSRC selects the clock divider source for the new NFC module

- LCDCSRC selects the clock divider source for the new LCDC module

- USBFSRC clock select for the new USBFS fractional divider

- NFC\_CLKSEL selects between the NFC clock divider and EXTAL1 clock

- LCDC\_CLKSEL selects between the LCDC clock divider and EXTAL1 clock

- CLKOUTSEL selects the internal clock to output on the CLKOUT pin

- RTCCLKOUTTSEL Selects the clock to output on the RTC\_CLKOUT pin (32 kHz or 1 Hz)

- USBHSRC selects the clock divider source for the new USB HS module

#### Remove bit/field names:

- I2SSRC

- MCGCLKSEL

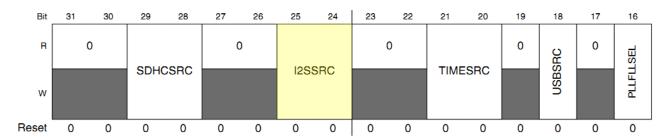

#### Changed bit/field names:

- USBSRC → USBFSRC bit field renamed to differentiate between USB FS and USB HS

- PLLFLLSEL → PLLFLLSEL field expanded to two bits to allow for selection of new internal clocks. The encodings are compatible between revisions, so code changes are not required to keep the same clock selection.

#### ວysເem Integration Module (SIM)

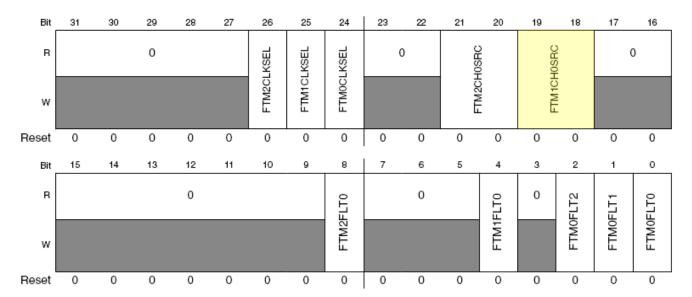

Figure 68. SIM\_SOPT4—Kinetis 100 MHz Rev. 1.x

Figure 69. SIM\_SOPT4—Kinetis 120 MHz

#### New bits/fields added:

- FTM3TRG1SRC, FTM3TRG0SRC, FTM0TRG1SRC, and FTM0TRG0SRC new hardware trigger source selects

- FTM3CLKSEL Clock select for new FTM instantiation

- FTM3FLT0 Fault select for new FTM instantiation

- FTM0FLT3 FTM0 fault 3 selection

#### Changed bit/field names:

• FTM1CH0SRC → Added option for the USB Start-of-Frame Pulse

#### **System Integration Module (SIM)**

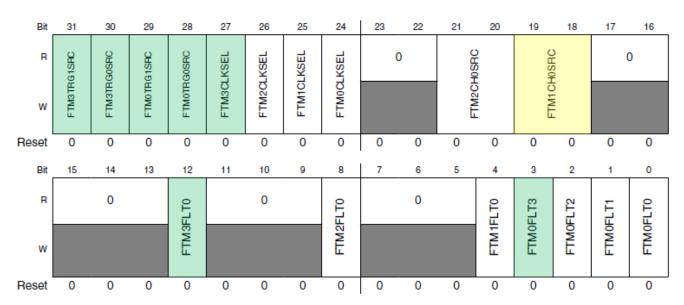

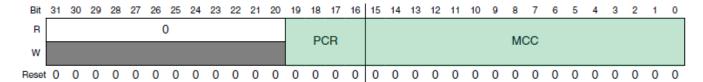

Figure 70. SIM\_SOPT6—Kinetis 100 MHz Rev. 1.x

Figure 71. SIM\_SOPT6—Kinetis 120 MHz

#### New bits/fields added:

• PCR and MCC -These fields control hold times for sharing of pins between the NFC and FlexBus

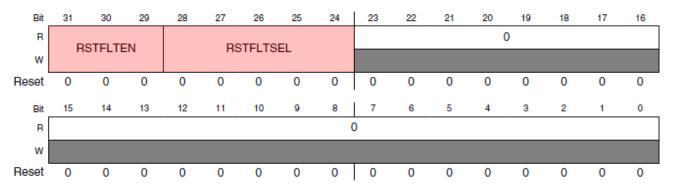

#### Remove bit/field names:

- RSTFLTEN and RSTFLTSEL the reset pin filter functionality has moved to the RCM

- MCGCLKSEL

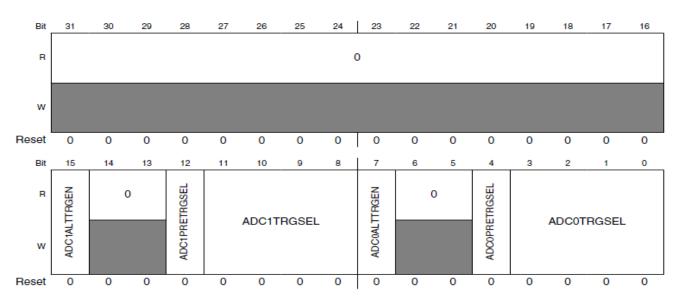

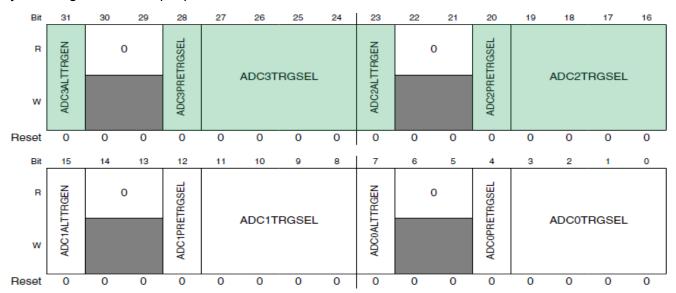

Figure 72. SIM\_SOPT7—Kinetis 100 MHz Rev. 1.x

#### **System Integration Module (SIM)**

Figure 73. SIM\_SOPT7—Kinetis 120 MHz

#### New bits/fields added:

- ADC3ALTTRGEN, ADC3PRETRGSEL, ADC3TRGSEL bits added to control new ADC instantiation

- ADC2ALTTRGEN, ADC2PRETRGSEL, ADC2TRGSEL bits added to control new ADC instantiation

#### 4.1.1.2 SIM SCGC register changes

The SIM module has a number of system clock gating control registers. New bits have been added to many of the registers to add clock gating control bits for new modules that were not present on the Kinetis 100 MHz Rev 1.x devices. The clock gating registers are backwards compatible, so changes to the clock gating are only required to use new modules and/or new module instantiations. Code does not need to be modified to enable the clock gate for modules that were available on the Kinetis 100 MHz Rev. 1.x MCUs.

# 4.1.1.3 SIM CLKDIV register changes

The SIM module also adds clock dividers for new modules including the USB HS, LCDC, and NFC. The fields to control each these clock dividers can be found in SIM CLKDIVn registers. These fields are all associated with the addition of new modules, so the changes to these registers are only a concern if using one of the new modules.

The only previously existing module with new bits in the CLKDIV registers is the trace clock. Because of the higher CPU frequency, a trace clock divider has been added to the 120 MHz Kinetis devices. By default the trace clock will be divided by two.

### 4.1.1.4 SIM miscellaneous control register

The last register for the SIM module is the addition of a miscellaneous control register (MCR). This module has fields for:

- Trace clock enable/disable

- ULPI clock direction

- PDB loop mode

- LCD display start/stop

- · DDR RCR reset status

- DDR RCR reset request

- DDR pad configuration

- · DDR DOS enable

- · DDR I/O enable/disable

- · DDR self refresh status

- · DDR self refresh enable

### 4.1.2 Software impact

Because the SIM is responsible for control and configuration of many module features, many applications might be impacted by the changes to the SIM module. Although some applications might not require any software changes, the SIM is one of the areas most likely to require software updates. The exact changes needed will depend heavily on the modules that are being used and the desired configuration and clocking of those modules. In order to use new modules, initialization of the SIM clock gating and any other control fields associated with the new module will be required.

Operating the Kinetis MCU with DDR memory in low power modes, VLPS, VLPR, STOP, LLS and VLLSx requires SIM\_MCR and DDR memory controller settings to minimize the power being used by the DDR controller and memory. The bits in the SIM\_MCR register that control the pads and analog circuit configuration should be properly set to minimize leakage current while in the low power modes. The external DDR memory device should also be placed in a DDR low power mode as well. See the SIM\_MCR register description and the DDR memory controller section in the Reference Manual for details of these modes.

### 4.1.3 Hardware impact

The SIM isn't directly associated with external signals, so the SIM changes do not require hardware changes. However, some of the modules impacted by the SIM changes might require hardware updates.

# 4.2 Direct Memory Access Controller (eDMA)

#### 4.2.1 Features

The Kinetis 100 MHz devices support 16 channels on the EDMA. Due to the increased on-chip integration for the 120 MHz devices, the number of DMA channels has been increased to 32.

### 4.2.2 Impacted registers

In order to support the new DMA channels there are some changes to the eDMA's memory map. All of the changes are additions. Any of the existing bits that were previously in the 100 MHz Kinetis devices remain the same.

The table below shows the new eDMA transfer control descriptor (TCD) registers that have been added to the eDMA in order to support the increased number of channels. The following section lists register fields that have been added.

Table 10. Memory map comparison

| Register       | 16-channel eDMA Locations                                | 32-channel eDMA Locations                                |

|----------------|----------------------------------------------------------|----------------------------------------------------------|

| DMA_TCDn_SADDR | $0x4000_{9000} + (32d \times n)$ , where $n = 0d$ to 15d | $0x4000_{9000} + (32d \times n)$ , where $n = 0d$ to 31d |

| DMA_TCDn_SOFF  | $0x4000\_9004 + (32d \times n)$ , where $n = 0d$ to 15d  | $0x4000_{9004} + (32d \times n)$ , where $n = 0d$ to 31d |

Table continues on the next page...

#### שווענ Memory Access Controller (eDMA)

#### Table 10. Memory map comparison (continued)

| Register          | 16-channel eDMA Locations                                | 32-channel eDMA Locations                                |

|-------------------|----------------------------------------------------------|----------------------------------------------------------|

| DMA_TCDn_ATTR     | $0x4000\_9006 + (32d \times n)$ , where $n = 0d$ to 15d  | $0x4000\_9006 + (32d \times n)$ , where $n = 0d$ to 31d  |

| DMA_TCDn_NBYTES   | $0x4000\_9008 + (32d \times n)$ , where $n = 0d$ to 15d  | $0x4000\_9008 + (32d \times n)$ , where $n = 0d$ to 31d  |

| DMA_TCDn_SLAST    | $0x4000\_900C + (32d \times n)$ , where $n = 0d$ to 15d  | $0x4000\_900C + (32d \times n)$ , where $n = 0d$ to 31d  |

| DMA_TCDn_DADDR    | $0x4000_{9010} + (32d \times n)$ , where $n = 0d$ to 15d | $0x4000_{9010} + (32d \times n)$ , where $n = 0d$ to 31d |

| DMA_TCDn_DOFF     | $0x4000_{9014} + (32d \times n)$ , where $n = 0d$ to 15d | $0x4000_{9014} + (32d \times n)$ , where $n = 0d$ to 31d |

| DMA_TCDn_CITER    | $0x4000_{9016} + (32d \times n)$ , where $n = 0d$ to 15d | $0x4000_{9016} + (32d \times n)$ , where $n = 0d$ to 31d |

| DMA_TCDn_DLASTSGA | $0x4000_{9018} + (32d \times n)$ , where $n = 0d$ to 15d | $0x4000_{9018} + (32d \times n)$ , where $n = 0d$ to 31d |

| DMA_TCDn_CSR      | $0x4000_{901}C + (32d \times n)$ , where $n = 0d$ to 15d | $0x4000\_901C + (32d \times n)$ , where $n = 0d$ to 31d  |

| DMA_TCDn_BITER    | $0x4000\_901E + (32d \times n)$ , where $n = 0d$ to 15d  | $0x4000\_901E + (32d \times n)$ , where $n = 0d$ to 31d  |

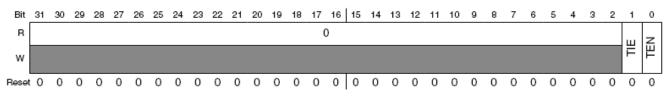

#### 4.2.2.1 DMA\_ERQ

Figure 74. DMA\_ERQ—Kinetis 120 MHz

#### New bits/fields added:

• ERQ31-ERQ16

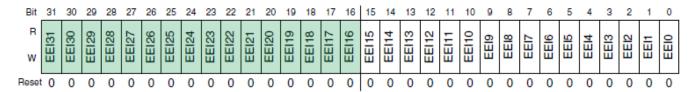

### 4.2.2.2 DMA\_EEI

Figure 75. DMA\_EEI—Kinetis 120 MHz

#### New bits/fields added:

• EEI31-EEI16

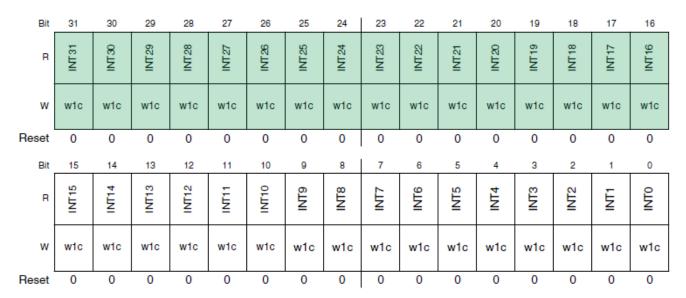

### 4.2.2.3 DMA\_INT

Figure 76. DMA\_INT—Kinetis 120 MHz

#### New bits/fields added:

• INT31-INT16

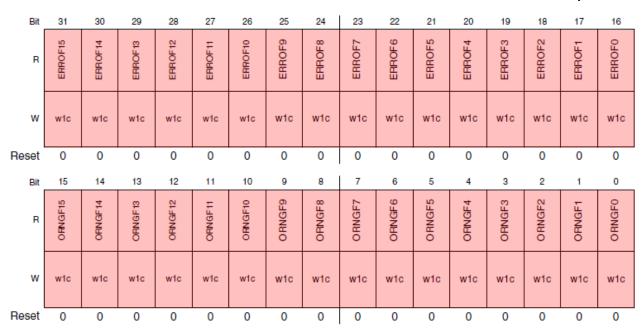

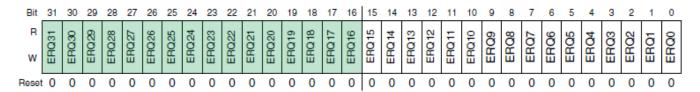

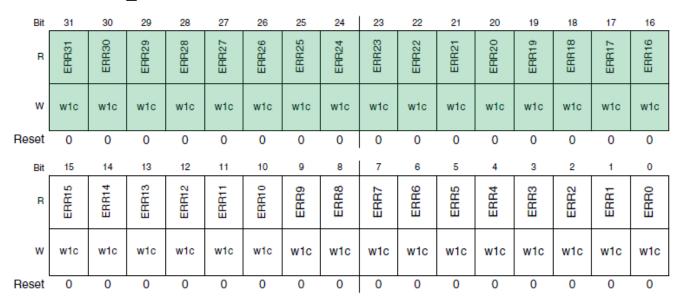

#### 4.2.2.4 DMA\_ERR

Figure 77. DMA\_ERR—Kinetis 120 MHz

#### New bits/fields added:

• ERR31-ERR16

wuu-Clock Generator (MCG)

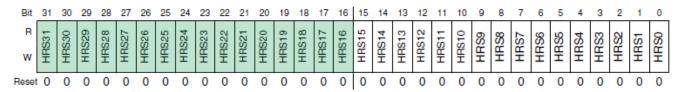

#### 4.2.2.5 DMA\_HRS

Figure 78. DMA\_HRS—Kinetis 120 MHz

#### New bits/fields added:

HRS31-HRS16

### 4.2.3 Software impact

Existing code will run on the eDMA with no changes. If you want to take advantage of the new channels, then software updates will be needed.

### 4.2.4 Hardware impact

No hardware impact.

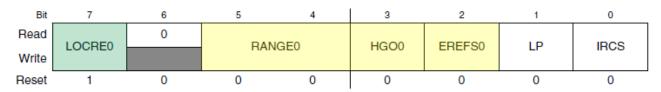

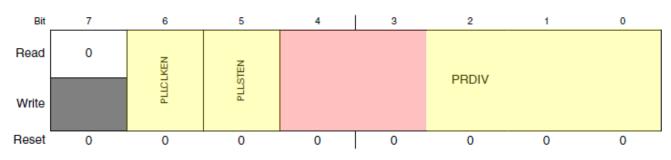

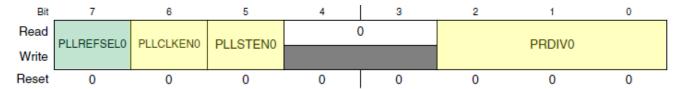

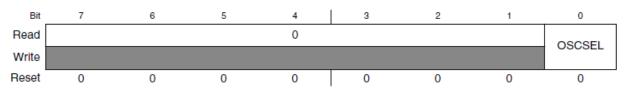

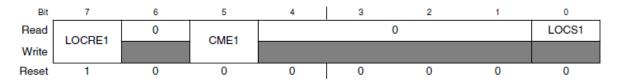

# 4.3 Multi-Clock Generator (MCG)

#### 4.3.1 Features

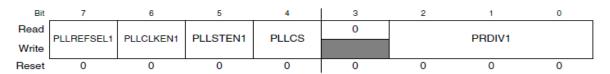

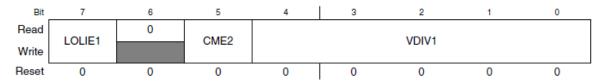

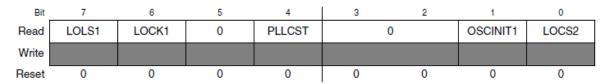

The MCG on the Kinetis 120 MHz products has a number of changes. Most importantly the PLL supports higher frequencies. There are also two PLLs included within the MCG instead of just one.

New features of the MCG include:

- Maximum PLL output frequency increases to 120MHz or 150MHz (max depends on part number speed grade)

- Second PLL has been added. Either PLL0 or PLL1 can provide the system level clocks (MCGOUTCLK).

- Only PLL1 can be used as the clock source for the DDR module.

- · A second OSC has been added

- Either of the OSCs can be the input to either of the PLLs

- Only OSC0 or the RTC OSC can be the input to the FLL

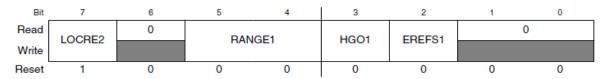

- Additional OSC control outputs have been added to the MCG for control of the second OSC (HGO1, RANGE1, EREFS1)

- PLL input reference range is now 8-16 MHz

- MCG registers can only be written when in privileged mode. Registers can be read in any mode.

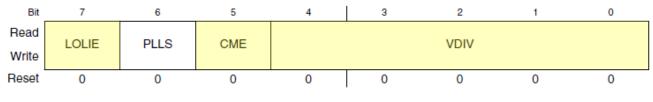

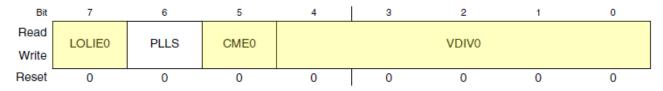

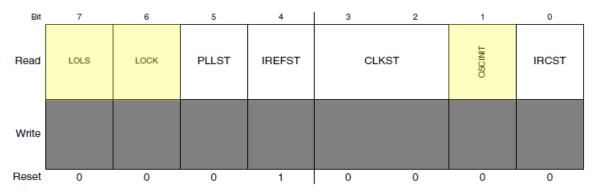

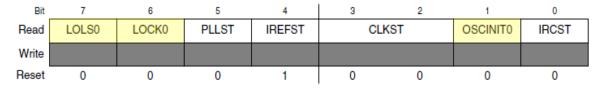

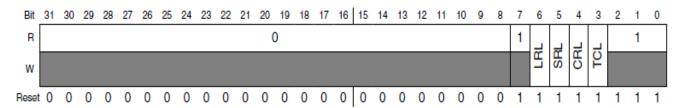

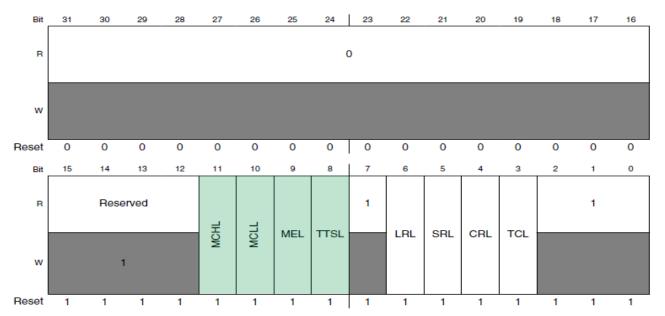

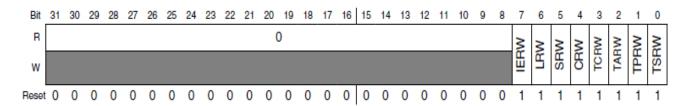

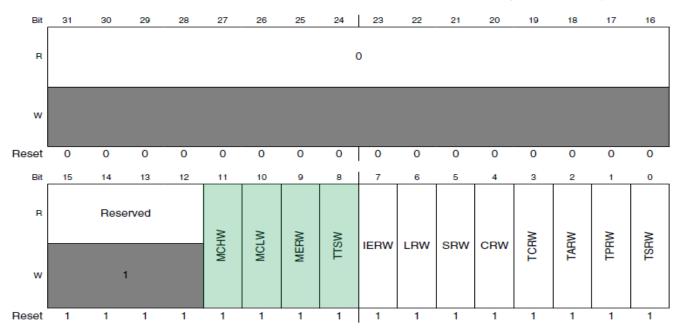

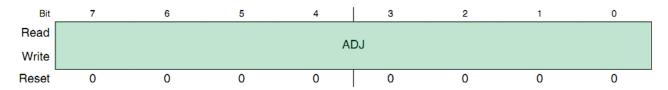

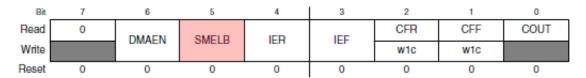

# 4.3.2 Impacted registers