# Freescale Semiconductor

**Application Note**

Document Number: AN4182 Rev. 0, 08/2010

# Different Display Configurations on the i.MX31 Linux PDK

by Multimedia Application Division Freescale Semiconductor, Inc. Austin, TX

This application note provides the necessary information, considerations, and procedures to add or adapt a new Liquid Crystal Display (LCD) panel to the Board Support Package (BSP) distribution for the i.MX31 Product Development Kit (PDK). The application note describes the general LCD panel information and generalities of the display controller module. The application note also describes the development process to adapt a new LCD panel to the BSP, considering that the framework driver structure is already provided by the operating system.

#### NOTE

This application note assumes that the reader is familiar with the Linux Target Image Builder (LTIB) and Linux device driver development concepts.

# 1 Introduction

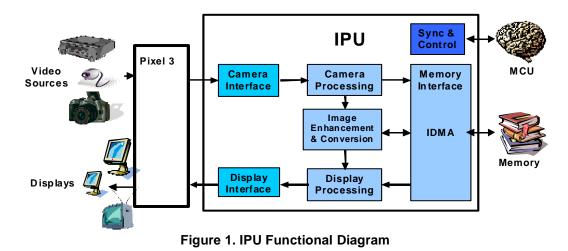

The i.MX31, which is a multimedia processor, supports several types of displays. The display devices are handled by a special module called the Image Processing Unit (IPU).

#### Contents

| l. | Introduction 1                    |

|----|-----------------------------------|

| 2. | LCD Generalities 3                |

| 3. | IPU-SDC Generalities 5            |

| 1. | Display Configuration in Linux 23 |

| 5. | References 50                     |

| 5. | Revision History 50               |

© 2010 Freescale Semiconductor, Inc. All rights reserved.

Introduction

The IPU module handles other graphic interfaces that include cameras and 2D graphics accelerators. These are the IPU submodules that are connected by a private DMA interface (IDMA) and is used by the IPU to transfer data among the modules and between the IPU and external memory.

Figure 1 shows the functional diagram of the IPU module.

The process of selecting an LCD for a mobile device involves several conflicts with respect to the requirements. Some of these conflicts are as follows:

- Large amount of data, implying high rate of data transfer and processing that requires significant resources

- Flexibility to support various use cases

- Size, cost, and power consumption

Freescale provides reference designs for the i.MX family where the functionalities of the LCD devices are demonstrated. However, developers find many reasons to replace the display in their products. Features such as screen size, resolution, weight, power consumption, and price are important in a commercial multimedia product. Also, many LCD displays become obsolete quickly and is difficult to find the same LCD panel that is included in the reference design. This application note is intended only for the dumb displays and displays that do not have the sharp synchronous interface. However, the application note also provides useful information about the smart displays.

#### NOTE

Do not confuse sharp LCDs with sharp interface. There are plenty of sharp panels that do not use sharp interface.

## 2 LCD Generalities

This section describes the principles of the LCD devices.

## 2.1 LCD Basics

LCDs are electronic devices that contain array of pixels. These pixels can be either color or monochrome and are created with a special material that changes the light characteristics that passes through them. These devices are not able to emit light, and therefore, the backlight unit is also shipped with the panel to create a full functional display device.

## 2.1.1 Resolution

In this application note, the term resolution refers to the number of pixels in an LCD array. The resolution has two dimensions—horizontal and vertical. Table 1 lists the most common video resolution standards available in the market.

| Video Name | Description                          | Width<br>(pixels) | Height<br>(pixels) | Aspect Ratio |

|------------|--------------------------------------|-------------------|--------------------|--------------|

| CGA        | Color Graphics Adapter               | 320               | 200                | 8:5          |

| QVGA       | Quarter VGA                          | 320               | 240                | 4:3          |

| VGA        | Video Graphics Array                 | 640               | 480                | 4:3          |

| NTSC       | National Television System Committee | _                 | _                  | —            |

| PAL        | Phase Alternating Line (TV)          | —                 | _                  | 4:3          |

| WVGA       | Wide VGA                             | 800               | 600                | 5:3          |

| SVGA       | Super VGA                            | 800               | 600                | 4:3          |

#### **Table 1. Video Resolution Standards**

#### NOTE

The maximum resolution supported by the i.MX31 processor is SVGA. Therefore, resolutions greater than SVGA are not included in Table 1.

The resolutions mentioned in Table 1 refer to the landscape orientation of the LCD panels. In the landscape orientation, the horizontal pixels are more than the vertical pixels. However, portrait orientated LCD panels are also available in the market with the same standard resolution where the horizontal and vertical sizes are inverted. Therefore, the portrait LCD panels have more vertical pixels than the horizontal pixels.

**LCD Generalities**

Figure 2 shows the portrait and landscape orientations in an LCD panel.

Figure 2. Portrait and Landscape Orientations

It is important to select a proper orientation for an LCD panel as both the electronic and optical features are optimized for the applications that use native orientation for the panel. Besides the optical characteristics, the dumb displays include an embedded LCD controller that draws the pixels from left to right and top to bottom. To show images or videos on the LCD panel using a non-native orientation, the display contents are processed to store the image in a buffer. The image is rewritten in a way that the LCD controller expects the pixel information to be sent. This operation is called rotation and the i.MX31 processor includes hardware to perform this operation.

## NOTE

It is recommended to select an LCD panel that uses native orientation to avoid additional image processing.

Figure 3 shows the non-native portrait and landscape orientations in an LCD panel.

Figure 3. Non-native Portrait and Landscape Orientations

## NOTE

In a non-native orientation, the rotation can be  $90^{\circ}$ ,  $180^{\circ}$ , or  $270^{\circ}$ . Also, the frame should be rotated before sending to the display.

## 2.1.2 Size

The size of an LCD panel is measured diagonally in inches. Since the size directly impacts the pixel width, it is common to assume that the size of a VGA ( $640 \times 480$ ) panel to be larger than a QVGA ( $320 \times 240$ ) panel as the VGA panel has greater number of pixels compared to QVGA. However, this is not always true. LCD manufacturing processes allow the size and resolution to be independent variables. It is difficult to determine the size of a panel from its resolution alone. Large screens tend to consume more power than the smaller ones and affect the size and weight of the final product. Also, higher resolutions on smaller LCD panels can complicate the visibility of on-screen objects for the final user. Therefore, based on the

information available in the data sheet, it is difficult to determine if a particular LCD panel fits the application. It is recommended to view the LCD in any other reference design or demo before selecting an LCD panel for any application.

## 2.1.3 Color Spaces

A color space is a way to represent colors. There are two main color spaces—RGB (RGB444, RGB565, RGB666, RGB888, and RGBA8888) and YUV (YUV 4:4:4, YUV 4:2:2, and YUV 4:2:0). The i.MX31 processor supports working with both the color spaces. However, the display panels can receive data only by using the RGB interface.

## 2.2 LCD Types

This section describes the different types of LCD displays.

## 2.2.1 Synchronous Panel (Dumb Display)

The dumb displays or synchronous displays are panels that require microprocessor to send data continually. In these panels, screen refresh is performed by sending the complete frame data continuously. In general, the smart displays are more expensive than the dumb displays, and this is one of the reasons for the common usage of synchronous panels in a final product. This application note focuses on Thin Film Transistor (TFT) LCD panels that belongs to a special group of synchronous panels.

## 2.2.2 Asynchronous Panel (Smart Display)

The advantage of smart displays is that the i.MX31 processor is required to send the display data only when the image is changed. In these panels, the images can be sent at any time and the screen refresh is handled by the embedded smart LCD display controller.

# 3 IPU-SDC Generalities

This section describes the IPU Synchronous Display Controller (SDC) generalities.

## 3.1 LCD Interfaces

This section describes the various LCD interfaces with examples.

## 3.1.1 Synchronous Display Interface

The i.MX31 SDC can be configured to handle four different types of devices—TFT monochrome, TFT color, YUV progressive, and YUV interlaced. However, this application note is focused only on the

synchronous TFT color interface. The i.MX31 processor provides a 22-line interface for the TFT color device and is described in Table 2.

| Signal          | IPU Signal        | Description                |

|-----------------|-------------------|----------------------------|

| HSYNC           | DISPB_D3_HSYNC    | horizontal synchronization |

| VSYNC           | DISPB_D3_VSYNC    | vertical synchronization   |

| DRDY            | DISPB_D3_DRDY     | data enable or data ready  |

| PIXCLK          | DISPB_D3_CLK      | pixel clock                |

| Red Data[5:0]   | DISPB_DATA[17:12] | pixel red component        |

| Green Data[5:0] | DISPB_DATA[11:6]  | pixel green component      |

| Blue Data[5:0]  | DISPB_DATA[5:0]   | pixel blue component       |

Table 2. Synchronous Display Interface Signals

The signals and interfaces in the synchronous display system are as follows:

| HSYNC    | Horizontal Synchronization (HSYNC) signal is also known as FPLINE or<br>LP. This signal indicates the end of a line and the following valid pixels<br>are part of the next line.                                                                                                                                                                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSYNC    | Vertical Synchronization (VSYNC) signal is also known as FPFRAME,<br>FLM, SPS, or TV. Active state of this signal indicates the end of the<br>current frame. The LCD display should then restart the line index to zero<br>to draw the next valid data in the first line of the panel.                                                                                                                                                          |

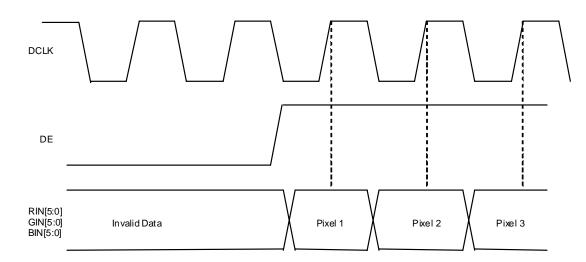

| DRDY     | The active state of the Data Ready (DRDY) or Data Enable (DE) signal<br>indicates the LCD device that the data in the RGB bus is valid and should<br>be latched using the Pixel Clock (PIXCLK) signal. When the DE signal is<br>active, a pixel corresponding to the color described in the RGB bus is<br>drawn with every PIXCLK pulse. This signal always has the value of the<br>screen width.                                               |

| PIXCLK   | The polarity of the PIXCLK signal specifies if the RGB data is placed on<br>the bus during the rising or falling edges. Based on the polarities, the<br>operations are performed in the following ways:                                                                                                                                                                                                                                         |

|          | <ul> <li>High polarity indicates that the data is written on the RGB bus during the falling edges and data is latched into the LCD panel during the rising edges. This is valid only when the DE signal is active.</li> <li>Low polarity indicates that the data is written on the RGB bus during the rising edges and data is latched into the LCD panel during the falling edges. This is valid only when the DE signal is active.</li> </ul> |

| RGB data | The RGB data is transferred to the display through the display interface.<br>Though the i.MX31 processor can internally use different types of bits per<br>pixel, such as RGB565, RGB666, RGB888, and RGBA8888, the display<br>interface is limited to 18 lines. Therefore, any image or video that contains<br>pixels more than 18 bits (RGB666) cannot be sent to the display. During                                                         |

the RGB to RGB conversion, the less significant bits are removed from the pixel and the remaining bits are directly sent to the display interface.

#### NOTE

Dithering or filtering actions are not performed in this process.

| Extra signals | There are also other signals that are included in the panel interface. These signals are not part of the display data interface but are required for a full functional module. For example, it is common that some panels require a reset signal and initialization commands. These commands are sent by a serial interface, such as $I^2C$ or Serial Peripheral Interface (SPI). Also, the embedded touch panel and backlight unit are shipped along with the module. |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPI interface | Some LCD displays require an initialization routine through a serial interface that can be 3-wire, 4-wire, or 5-wire. A serial interface (SD_D_CLK, LCS1, SD_D_IO, and SD_D_I) in the i.MX31 IPU is not used to send serial commands to the LCDs. This interface is not intended for a general purpose usage and is used only by the IPU when two or more asynchronous displays are configured to use the serial interface.                                            |

## 3.1.2 Examples of Synchronous Display Interfaces

This section describes a few synchronous display interfaces.

## 3.1.2.1 i.MX31 PDK Epson L4F00242T03 2.7" VGA LCD Interface

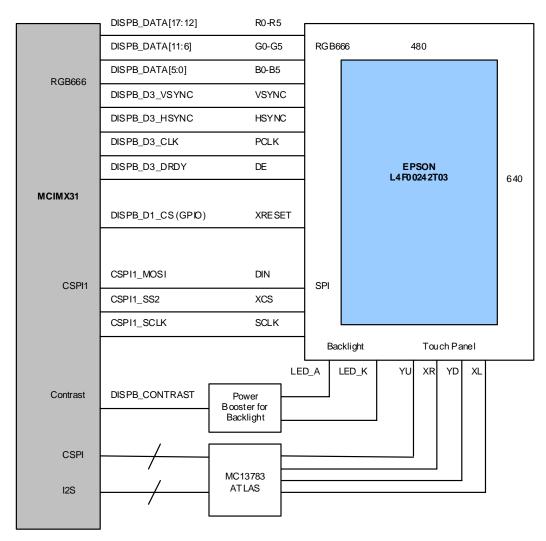

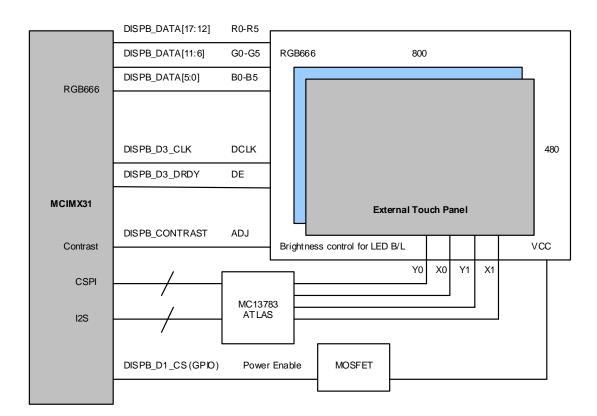

Figure 4 shows the interface between the i.MX31 processor and Epson L4F00242T03 VGA panel.

Figure 4. Interface between i.MX31 and Epson L4F00242T03 VGA Panel

The LCD panel is shipped with the i.MX31 PDK, and the panel requires the HSYNC, VSYNC, DE, and PIXCLK signals and complete RGB data interface (DISPB\_DATA[17:0]). Also, a reset signal and serial interface (SPI) are required for sending the initialization routine commands. The backlight unit is controlled by using a Pulse Width Modulated (PWM) signal (contrast signal) that is generated by the i.MX31 processor, and the touch panel interface is handled by the MC13783 Atlas<sup>TM</sup> chip.

Every panel has its own interface and requirements, but this example illustrates a typical synchronous panel interface. Therefore, consider the possibility shown in Figure 4 as the base for the panel interface. The idea of base interface is useful when there are many panels that do not use the complete interface. For example, some of the panels do not require the HSYNC, VSYNC, reset, or serial initialization routine to handle the display signals. These panels use only the DRDY, PIXCLK, and RGB data and expect the

microprocessor to accomplish with the waveforms as there is no way for the LCD panel to handle a different interface.

The only disadvantage with this interface is that the panel does not provide a backlight power booster and requires an external chip (MAX8595ZETA+T) to amplify the contrast signal.

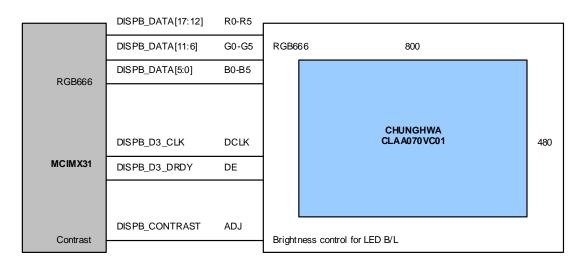

## 3.1.2.2 i.MX31 PDK Chunghwa CLAA070VC01 7" WVGA LCD Interface

Figure 4 shows the interface between the i.MX31 and Chunghwa CLAA070VC01 WVGA panel.

#### Figure 5. Interface between i.MX31 and Chunghwa CLAA070VC01 VWGA Panel

Figure 5 shows a simple display interface where the HSYNC and VSYNC signals are not used. Therefore, the DISPB\_D3\_VSYNC and DISPB\_D3\_HSYNC pins can be used for other purposes. Also, as the SPI interface is not required, it can be used as a chip select (CSPI1\_SS2) for the other devices. Additionally, the power booster for the backlight unit is included in the module, which means that the contrast signal is directly connected to the display connector.

Apart from these advantages, the WVGA panel has the following disadvantages:

- The display module does not include a touch panel. Therefore, an external LCD panel should be added to the display module.

- The LCD module does not have a reset signal or SPI interface. Therefore, the display cannot be turned OFF. This feature is important particularly for mobile devices where power consumption is an issue. Therefore, external circuits are required to control the energy consumption of the LCD.

Based on these observations, the complete LCD circuit with the external panel and power control circuitry is shown in Figure 6.

# Figure 6. Interface between i.MX31 and Chunghwa CLAA070VC01V WVGA Panel with Touch Panel and Power Control Circuitry

#### NOTE

These examples are helpful for selecting an LCD panel.

## 3.2 Synchronous Display Timing and Signals

This section focuses on the timing and signal waveforms and describes how to configure them in the LCD panel and i.MX31 display interface. The first step to select an LCD module is to refer to the corresponding LCD module data sheet. The data sheet shows the pin interfaces, initialization routines, and timing charts for the RGB and serial interfaces if required. An abridged version of the data sheet is also available where all this information is not included. It is advisable to use the fully documented data sheet. Though there is not much difference between the preliminary and final versions, it is always better to use the final version.

## 3.2.1 Timing Concepts

Some important concepts and considerations, which form the base for the LCD interface timing, are given in Table 3.

| Parameter                    | Description                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Horizontal Back Porch (HBP)  | Number of PIXCLK cycles between the HSYNC signal and first valid pixel data                                                                                                                                                                                                                                                                                            |

| Horizontal Front Porch (HFP) | Number of PIXCLK cycles between the last valid pixel data in the line and the next HSYNC pulse                                                                                                                                                                                                                                                                         |

| Vertical Back Porch (VBP)    | Number of lines (HSYNC pulses) between the asserted VSYNC signal and the next valid line                                                                                                                                                                                                                                                                               |

| Vertical Front Porch (VFP)   | Number of lines (HSYNC pulses) between the last valid line of the frame and the next VSYNC pulse                                                                                                                                                                                                                                                                       |

| VSYNC pulse width            | Number of lines (HSYNC pulses) between the last valid line of the frame and the next VSYNC pulse                                                                                                                                                                                                                                                                       |

| HSYNC pulse width            | Number of PIXCLK pulses when the HSYNC signal is active                                                                                                                                                                                                                                                                                                                |

| Active frame width           | Is the horizontal resolution, which is the number of pixels in a line. For a WVGA display of resolution, $800H \times 480V$ , the frame width is equal to 800 pixels.                                                                                                                                                                                                  |

| Active frame height          | Is equal to the vertical resolution of the LCD. For a WVGA display of resolution, $800H \times 480V$ , the value of the frame height is 480 lines.                                                                                                                                                                                                                     |

| Screen width                 | For the i.MX31 processor, screen width is the number of pixel clock periods between the last HSYNC and new HSYNC. This value not only includes the valid pixels but also the HBP and HFP. Note that this value is not equal to the horizontal resolution of the LCD panel (numbers of pixels in one line). Equation 1 gives the formula to calculate the screen width. |

|                              | SCREEN_WIDTH = ACTIVE_FRAME_WIDTH + HBP + HFP Eqn. 1                                                                                                                                                                                                                                                                                                                   |

| Screen height                | For the i.MX31 processor, screen height is the number of rows between the last VSYNC pulse and new VSYNC pulse. This value includes all the valid lines, VBP, and VFP. Equation 2 gives the formula to calculate the screen height.                                                                                                                                    |

|                              | SCREEN_HEIGHT = ACTIVE_FRAME_HEIGHT + VBP + VFP Eqn. 2                                                                                                                                                                                                                                                                                                                 |

| VSYNC polarity               | Is the value held by the VSYNC signal to indicate the beginning of a new frame. The VSYNC polarity can be active low or active high.                                                                                                                                                                                                                                   |

| HSYNC polarity               | Is the value held by the HSYNC signal to indicate the beginning of a new line. The HSYNC polarity can be active low or active high.                                                                                                                                                                                                                                    |

#### Table 3. Timing Concepts

## 3.2.2 Timing Charts

The following charts are reviewed to clarify the timing issues in an LCD interface:

- Vertical timing chart

- Horizontal timing chart

- Pixel clock chart

Additionally, if the display uses a serial interface, refer to another chart that describes the serial interface and reset. This information should be extracted from the data sheet when a support for a new LCD panel is added. This is described with the following example. Consider a VGA (480H × 680V) LCD panel that uses the EPSON L4F00242T03 panel interface, which is shown in Figure 4. This means that the display uses the RGB666, VSYNC, HSYNC, DE, pixel clock, and also requires a reset signal and serial interface.

## 3.2.2.1 Vertical Timing Charts

This section describes the VGA and WVGA vertical timing charts.

## **VGA Vertical Timing Chart**

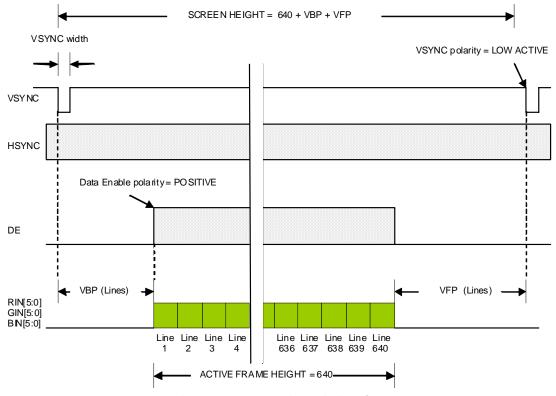

Figure 7 shows the vertical timing chart for a hypothetic synchronous VGA display ( $480H \times 680V$ ).

Figure 7. VGA Vertical Timing Chart

The vertical timing chart is analyzed in the following three stages:

• The beginning of a frame is indicated by the VSYNC signal (in this case, when the VSYNC signal goes low). The VSYNC period involves a complete frame cycle. During this period, all the pixels and lines in the frame are sent to the panel. When the VSYNC signal goes low (as the VSYNC signal is active low), the HSYNC signal immediately marks the beginning of the first line (in this case, the HSYNC signal goes low). However, to maintain the LCD timing, the first few lines are designated for the VBP. During the VBP, the DE signal is not present and the panel ignores the pixel data in the bus in all these lines.

- After the VBP, the DE signal appears in the boundaries of the HSYNC period (refer to Section 3.2.2.2, "Horizontal Timing Charts," for more information regarding the DE signal during the line cycle). Consequently, the DE signal appears during all the valid lines (with a vertical resolution of 640). During this time (ACTIVE FRAME HEIGHT), the LCD panel latches the RGB data on all the lines and draws them to the screen.

- During the VFP, extra lines (HSYNC cycles) appears. In this stage, the DE signal remains inactive and the panel discards any information in the RGB bus. The frame ends when the next VSYNC signal is asserted (goes low).

Table 4 gives the range of the timing features that is similar to the one provided the data sheet.

| Parameter                       | Symbol | Minimum | Typical | Maximum | Unit  |

|---------------------------------|--------|---------|---------|---------|-------|

| Screen Height or Vertical Cycle | VP     | _       | 665     | _       | Line  |

| VSYNC Pulse Width               | VSW    | 5       | 10      | 15      | Line  |

| Vertical Back Porch             | VBP    | 5       | 10      | 15      | Line  |

| Vertical Front Porch            | VFP    | 5       | 5       | 5       | Line  |

| Active Frame Height             | VDISP  | —       | 640     | _       | Line  |

| Vertical Refresh Rate           | FV     | —       | 60      |         | Hertz |

| Table | 4. \       | VGA | Vertical         | Timing |

|-------|------------|-----|------------------|--------|

| IUNIC | <b>-</b> . |     | <b>V</b> CI UCUI | 1 mmg  |

From Figure 7, the following features are verified:

- The VSYNC polarity is active low, which means that the vertical synchronization is normally in the high state and goes low to indicate the beginning of a new frame.

- The VSYNC pulse width (VSW) has certain flexibility. Therefore, the timing can be set using more than one value. It is recommended to use the typical values or values close to them. In this example, the typical value is taken as 10 lines.

- The VBP and VFP values are measured in lines as in HSYNC pulses. In this example, VBP is 10 lines and VFP is 5 lines width.

- The VSYNC width is included in the VBP stage, which means that the VBP starts when the VSYNC signal is asserted and not when the VSYNC signal returns to normal state.

Using these values, the screen height or vertical cycle (VP) is calculated as 665 lines. In some cases, the value of the VBP and VFP are not given in lines, but in nanoseconds (ns) or milliseconds (ms). In this case, additional calculations should be performed to find the number of lines required to accomplish the corresponding timings.

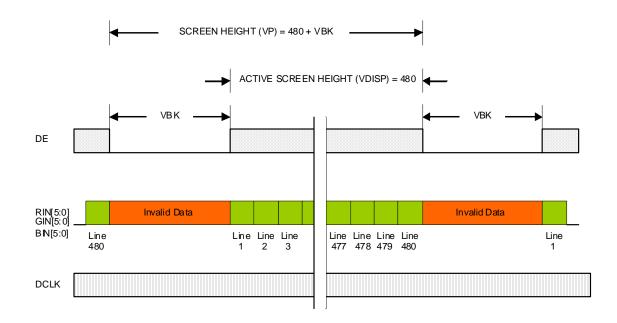

## WVGA Vertical Timing Chart

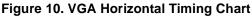

If an LCD panel, such as the hypothetical WVGA ( $800H \times 480V$ ), is used as described in Figure 5 and Figure 6, which does not use the HSYNC and VSYNC signals, the waveforms are analyzed in another perspective as shown in Figure 8.

#### Figure 8. WVGA Vertical Timing Chart

Table 5 gives the range of the timing features used in Figure 8.

Table 5. WVGA Vertical Timing

| Parameter                       | Symbol | Minimum | Typical | Maximum | Unit |

|---------------------------------|--------|---------|---------|---------|------|

| Screen Height or Vertical Cycle | VP     | 490     | 500     | 520     | Line |

| Vertical Blank                  | VBK    | 10      | 20      | 40      | Line |

| Active Screen Height            | VDISP  | 480     | 480     | 480     | Line |

| Vertical Refresh Rate           | FV     | 55      | 60      | 65      | Hz   |

In this cases, the VSYNC width, VSYNC polarity, VBP, and VFP are not exposed in the chart. Even if the VSYNC signal is not used, these values are required to configure the i.MX31 display interface. These waveforms are used to understand the vertical cycle behavior. For the i.MX31 processor, the sequence remains the same. That is, the vertical cycle starts with the VSYNC signal, then comes the VBP, followed by the active frame area and the VFP appears until the VSYNC signal is asserted again. The tip to find the VSYNC width, VBP, and VFP is based on the fact that these events happen during the vertical blank period.

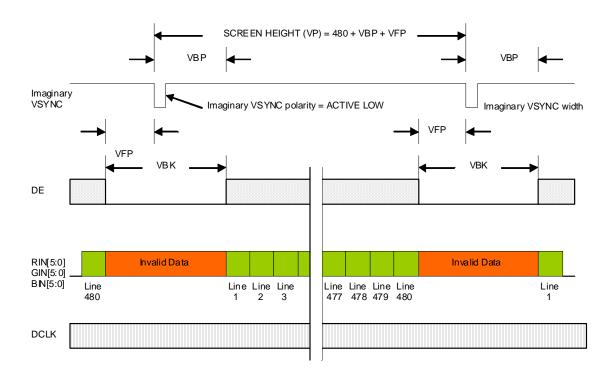

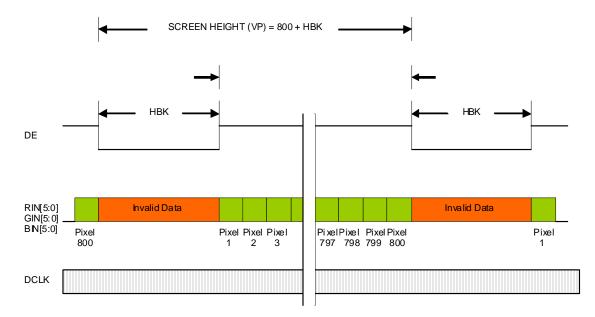

Figure 9 shows the WVGA vertical timing chart with the imaginary VSYNC signal.

Figure 9. WVGA Vertical Timing Chart with Imaginary VSYNC Signal

The VSYNC signal may not be mapped to any pin. This signal is used only as the base to calculate the VFP and VBP. As the VSYNC signal is not used, the signal can be set as active low or active high. However, it is recommend to set the VSYNC signal as active low. Though the VSYNC width is not a strict criterion, in these cases, the VSYNC width is taken as one line length (VSW = 1).

To find the VBP and VFP, the Vertical Blank (VBK) period is split into two parts—the first part is for the VFP before the VSYNC signal is asserted and the other part is for the VBP. The sum of these two values should fit in the VBK period. Though the VBK period can be split in any ratio, it is suggested to leave the imaginary VSYNC in the middle of the blank period, which means that the VBP and VFP values should be equal or almost equal.

Using this example, and considering that VBK is 20 lines (typical), the VBP and VFP values should be equal to 10 lines. Based on this information, the vertical timings are given in Table 6.

| Parameter                       | Symbol | Minimum | Typical | Maximum | Unit |

|---------------------------------|--------|---------|---------|---------|------|

| Screen Height or Vertical Cycle | VP     | 490     | 500     | 520     | Line |

| VSYNC Pulse Width               | VSW    | 1       | 1       | 1       | Line |

| Vertical Back Porch             | VBP    | 1       | 10      | 40      | Line |

| Vertical Front Porch            | VFP    | 0       | 10      | 39      | Line |

| Vertical Blank                  | VBK    | 10      | 20      | 40      | Line |

Table 6. WVGA Vertical Timing and Porches

| Parameter             | Symbol | Minimum | Typical | Maximum | Unit |

|-----------------------|--------|---------|---------|---------|------|

| Active frame height   | VDISP  | 480     | 480     | 480     | Line |

| Vertical refresh rate | FV     | 55      | 60      | 65      | Hz   |

## 3.2.2.2 Horizontal Timing Charts

This section describes the VGA and WVGA horizontal timing charts.

## **VGA Horizontal Timing Chart**

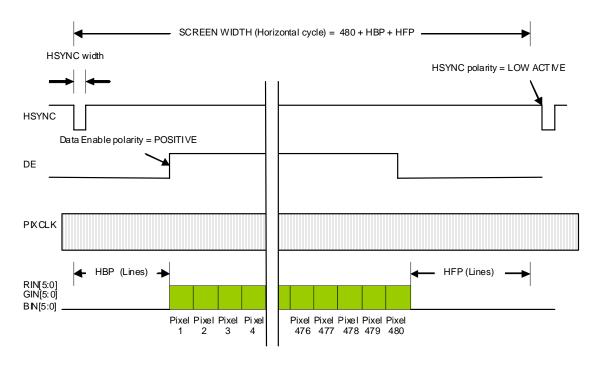

The data sheet also includes another chart that describes the line period and is shown in Figure 10.

This chart is analyzed in the following three stages:

- The line cycle begins when the HSYNC signal is asserted (in this case, when the signal goes low). Then, the HBP stage appears. During this time, the DE signal remains inactive.

- The horizontal active area (active frame width) begins when the DE (which is active high) signal is asserted. When the DE signal is active, the panel latches the RGB data placed in the bus and draws a new pixel on the screen for every PIXCLK pulse.

- The DE width is always equal to the horizontal resolution of the panel, (in this case, the DE width is 480 pixels length) and the active area ends when the DE signal is deasserted. After the active area, the HFP occurs and all the pixels in the line are drawn. The line cycle ends when the new HSYNC pulse is asserted.

The horizontal timings are given in Table 7.

| Parameter                        | Symbol | Minimum | Typical | Maximum | Unit   |

|----------------------------------|--------|---------|---------|---------|--------|

| Screen Width or Horizontal cycle | HP     | 495     | 601     | 741     | PIXCLK |

| HSYNC pulse width                | HSW    | 5       | 20      | 75      | PIXCLK |

| Horizontal back Porch            | HBP    | 5       | 60      | 75      | PIXCLK |

| Horizontal front porch           | HFP    | 5       | 41      | 75      | PIXCLK |

| Active Frame Width               | HDISP  | —       | 480     | 111     | PIXCLK |

Table 7. VGA Horizontal Timing

## WVGA Horizontal Timing Chart

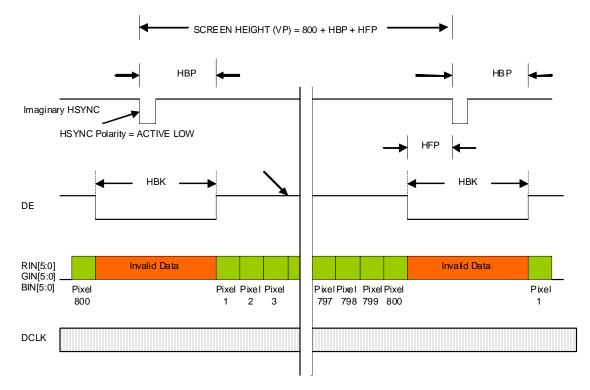

The WVGA horizontal timing chart and table in the data sheet are similar to the WVGA ( $800 \text{ H} \times 480 \text{ V}$ ) example shown in Figure 11 and Table 8, respectively.

#### Figure 11. WVGA Horizontal Timing Chart

| Table 8 | . WVGA | Horizontal | Timing |

|---------|--------|------------|--------|

|---------|--------|------------|--------|

| Parameter                        | Symbol | Minimum | Typical | Maximum | Unit   |

|----------------------------------|--------|---------|---------|---------|--------|

| Screen Width or Horizontal Cycle | HP     | 850     | 900     | 950     | PIXCLK |

| Horizontal Blank Period          | НВК    | 50      | 100     | 150     | PIXCLK |

| Active Frame Width               | HDISP  | 800     | 800     | 800     | PIXCLK |

The values of the HBP, HFP, and HSYNC width are calculated using the same procedure used in the Section, "WVGA Vertical Timing Chart."

The horizontal timing diagram with the imaginary HSYNC signal is shown in Figure 12.

#### Figure 12. WVGA Horizontal Timing Chart with Imaginary HSYNC Signal

Table 9 gives the range of the timing features used in Figure 12.

| Parameter                        | Symbol | Minimum | Typical | Maximum | Unit   |

|----------------------------------|--------|---------|---------|---------|--------|

| Screen width or Horizontal cycle | HP     | 850     | 900     | 950     | PIXCLK |

| HSYNC pulse width                | HSW    | 1       | 1       | 1       | PIXCLK |

| Horizontal back porch            | HBP    | 1       | 50      | 150     | PIXCLK |

| Horizontal front porch           | HFP    | 0       | 50      | 149     | PIXCLK |

| Horizontal blank period          | НВК    | 50      | 100     | 150     | PIXCLK |

| Active frame width               | HDISP  | 800     | 800     | 800     | PIXCLK |

## 3.2.2.3 Pixel Clock Timing Charts

This section describes the VGA and WVGA pixel clock timing charts.

#### **VGA Pixel Clock Timing Chart**

The waveform characteristics and table for the VGA pixel clock in the data sheet are similar to Figure 13 and Table 10, respectively.

#### Figure 13. VGA Pixel Clock Timing Chart

Table 10. VGA Pixel Clock Timing

| Parameter             | Symbol | Minimum | Typical | Maximum | Unit |

|-----------------------|--------|---------|---------|---------|------|

| Pixel clock frequency | PCLK   |         | 24      |         | MHz  |

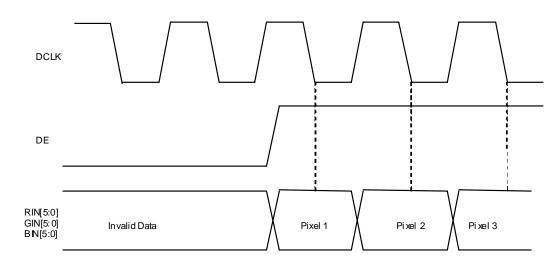

An important feature regarding the pixel clock (DCLK) is to understand when the LCD panel latches the RGB data. This characteristic is important because the i.MX31 processor must prepare the data one edge before the LCD latches the data into the bus. In this case, the data is latched by the LCD panel in DCLK rising edges. Therefore, the i.MX31 processor should be configured to write the RGB data into the bus during the DCLK falling edge. In this manner, the data is made ready and stable for the panel to read the data.

The clock polarity is set in the DI\_DISP\_SIG\_POL i.MX31 register, which is located under the D3\_CLK\_POL bit field. Figure 13 shows the typical inverse clock polarity. Also, the user should be aware that the maximal display clock rate cannot be greater than a quarter of the high speed processing clock rate. For example, the HSP\_CLK signal in the i.MX31 PDK BSP is 133 MHz. Therefore, the maximum pixel clock is 133 MHz  $\div$  4 = 33.25 MHz. However, most of the LCD displays work at a frequency lesser than the typical value.

## WVGA Pixel Clock Timing Chart

The waveform characteristics and table for the WVGA pixel clock in the data sheet is similar to Figure 14 and Table 11, respectively:

Figure 14. WVGA Pixel Clock Timing Chart

Table 11. WVGA Pixel Clock Timing

| Parameter             | Symbol | Minimum | Typical | Maximum | Unit |

|-----------------------|--------|---------|---------|---------|------|

| Pixel clock frequency | PCLK   | 25      | 27      | 32      | MHz  |

In contrast to the VGA panel, the WVGA latches the RGB in the falling edges of the DCLK signal. Therefore, the i.MX31 processor should be configured to write the RGB data into the bus during the DCLK rising edge. In this manner, the data is made ready and stable for the panel to read the data. Note that the waveform characteristics in Figure 14 shows the straight clock polarity.

## **Data Polarity**

Data polarity is the value of the signals in the RGB bus that the LCD recognizes as active. This can be described with an example where the i.MX31 processor tries to draw a red pixel (only the red component) by using an RGB565 interface with the following data polarity:

- If the LCD uses straight polarity, the value in the bus becomes 0xF8000, which means that all the RGB bits are high and the rest of the bits are low.

- If the LCD uses inverse data polarity, the value in the bus becomes 0x07FF, which means that the red bits are low and all other bits are high.

Both the values, 0xF8000 and 0x07FF, represent the red color, and the difference in the values is caused by the data polarity in the LCD panel. This feature is configured using the D3\_DATA\_POL bit field in the DI\_DISP\_SIG\_POL i.MX31 register.

## 3.2.3 Custom LCD Timing

This section describes the VGA and WVGA custom LCD timings.

## 3.2.3.1 VGA Custom LCD Timing

This section describes the reset signal and serial command interface.

#### Reset

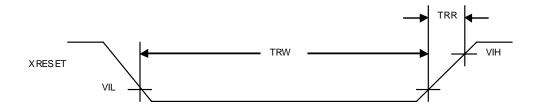

Many LCD panels include an LCD controller that requires an external system reset. If the LCD mentions the usage of this signal, then the user should find the timing regarding this pulse.

The reset signal and its timing are shown in Figure 15 and Table 12, respectively.

Figure 15. Reset Signal

Table 12. Reset Signal Timings

| Parameter         | Symbol | Minimum | Typical | Maximum | Unit |

|-------------------|--------|---------|---------|---------|------|

| Reset width       | TRW    | 15      | _       | _       | ns   |

| Reset rising time | TRR    | _       | _       | 10      | ns   |

From Figure 15, it can be observed that the reset signal is active low. This means that reset signal is high during normal operations. The reset signal should be low for at least 15 ns for it to be considered as a valid reset. Also, the rise time of the reset signal is restricted to 10 ns. Generally, the reset pin is controlled by the General Purpose Input Output (GPIO) in the i.MX31 processor.

## NOTE

It is recommended not to use the RC circuit to generate the reset signal as it restricts the rise time of the signal to 10 ns.

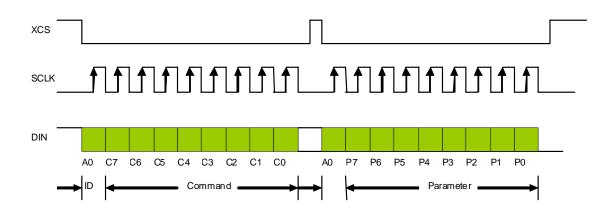

## **Serial Command Interface**

If the LCD panel has a serial command interface, a chart similar to Figure 16 is included in the data sheet.

Figure 16. SPI Command Interface Signals

This application note does not review all the serial interfaces of an LCD. The protocols and data formats are described in the data sheet, and the user should have knowledge about the synchronous serial interfaces to program the serial interface settings. For more information, refer to the Configurable Serial Peripheral Interface (CSPI) chapter in the *MCIMX31 and MCIMX31L Applications Processors Reference Manual* (MCIX31RM)

## 3.2.3.2 WVGA Custom LCD Timing

There are no custom signals regarding the panel interface as the WVGA panel does not require any reset or initialization.

## 3.3 LCD Panels Supported by i.MX31

The i.MX31 processor can support up to four displays simultaneously. Table 13 lists the various types of displays that are handled by the display controllers.

| Display | Display Type | Interface                                          |

|---------|--------------|----------------------------------------------------|

| DISP0   | Asynchronous | Parallel interface only                            |

| DISP1   | Asynchronous | Serial and parallel interface                      |

| DISP2   | Asynchronous | Serial and parallel interface                      |

| DISP3   | Synchronous  | RGB interface (HSYNC, VSYNC, PIXCLK, up to RGB666) |

| Table 13. Displays | Supported | by | i.MX31 |

|--------------------|-----------|----|--------|

|--------------------|-----------|----|--------|

Only one of the LCD display controllers in the i.MX31 processor is synchronous (dumb display). Therefore, the application note focuses on the DISP3 controller. The DISP3 RGB interface is multiplexed with all the other asynchronous parallel interfaces. This means that the data cannot be sent to the

synchronous display (DISP3) and another parallel device at the same time. Instead, the i.MX31 processor sends data to the asynchronous panel (smart display) when the synchronous interface is inactive (during HFP, HBP, VFP, and VBP). This is the reason for the frame rate in smart displays gets affected when multiple displays are attached to the i.MX31 processor.

The synchronous LCD interface in the i.MX31 processor is flexible and handles various types of LCD devices with the following characteristics:

- Synchronous display (dumb display)

- RGB interface (RGB666 maximum)

- Resolution not greater than SVGA

- Utilizes at least the DE and pixel clock signals to latch the RGB data (some LCDs require the HSYNC and VSYNC signals, which are also supported by the i.MX31 processor)

- Pixel clock frequency lower than 33.25 MHz

Also, the i.MX31 processor can handle dump displays with the sharp interface. However, this support is limited to certain models only. For more information regarding the timing restrictions, refer to the Interface to Sharp HR-TFT Panels section in the *MCIMX31 and MCIMX31L Multimedia Applications Processors* (MCIMX31\_5).

# 4 Display Configuration in Linux

The following sections describe how to add a new panel to the operating system. This includes the general display infrastructure in Linux, implementation of the display infrastructure in the i.MX family, and a few examples.

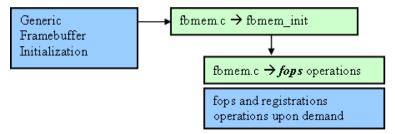

## 4.1 Linux Framebuffer Overview

This section describes the basic concepts and structures used in the Linux framebuffer.

## 4.1.1 Definition and Concept

Framebuffer concept is related to the graphics display video controller. Framebuffer can be viewed as a memory buffer for the video controller that contains a full frame of data. This frame of data becomes the information, which is shown on the display. The information provided to the frame consists of color values for each pixel.

In Linux, the framebuffer is implemented as a char device. An accurate definition for the Linux framebuffer implementation is provided by Geert Uytterhoeven in the kernel package document, —../linux-2.6.xx/Documentation/fb/framebuffer, and is as follows:

The framebuffer device provides an abstraction for the graphics driver. It represents the framebuffer of some video hardware and allows application software to access the graphic hardware through a well-defined interface. Therefore, the software is not required to know anything about the low-level interfaces.

The framebuffer infrastructure is easy to use and provides freedom for the user applications to access the video memory directly (by using the mmap() function). As the framebuffer is implemented as a char device,

the user applications can interface with the device by using the common system calls such as open(), read(), write(), ioctl(), and so on (these functions are part of the file operation interface that every char device should have). The mmap() function maps files or devices into the program memory. In this case, the video buffer area is resource mapped. Therefore, with the usage of the mmap() function, the function gets access to the user space memory, which is equivalent to the hardware video framebuffer. As a result, the user gets a pointer to the framebuffer memory and the changes can be made directly in this memory that gets reflected on the display. A similar procedure can be done using the write() and seek() operations. However, the operations performed by these functions are time consuming as they are required to be called several times to perform or cover a determined area in the framebuffer. These operations include change in a particular section of the framebuffer, change in the display area, and so on.

## 4.1.2 Linux Framebuffer Structures

The framebuffer in Linux provides a set of structures that are employed for user-space applications. These are the most important elements that should be considered when a new panel driver is developed.

The most important data structures in the Linux framebuffer are described as follows:

#### NOTE

For more information and full definition of each structure, refer to the .../include/linux/fb.h file.

• struct fb\_fix\_screeninfo—contains fixed parameters for the graphics card and its controller. An

example of a similar parameter is unsigned long smem\_start (used at start of the framebuffer

memory). This structure can be used in the user applications.

Some of the other important parameters that are used in the structure are as follows:

- \_\_u32 smem\_len—refers to the length of the framebuffer memory

- \_\_u32 type—refers to the pixel format

- struct fb\_var\_screeninfo—contains variables or alterable parameters for the graphics card/controller. These parameters refer to the features such as resolution and number of bits per pixel (\_u32 bits\_per\_pixel) that are configured by the user. These parameters also contain structures that define the length and bit offset for each colors (for example, struct fb\_bitfield). The fb\_var\_screeninfo structure can be used in the user applications.

Some of the other important parameters that are used in the structure are as follows:

- \_\_u32 xres—visible resolution along the x axis

- \_\_u32 yres—visible resolution along the y axis

- \_\_u32 xoffset—offset from virtual to visible resolution along the x axis

- struct fb\_bitfield—contains the detailed information of each color in a pixel (blue, green, and red). The fields of this structure include \_\_u32 offset (refers to beginning of the bit field),

- \_\_u32 length (refers to the length of the bit field), and the most significant bit flag. The

fb\_var\_screeninfo structure contains one structure for each color (red, green, and blue).

The fb\_bitfield structure is as follows:

```

struct fb_bitfield {

__u32 offset;/* beginning of bitfield*/

u32 length;/* length of bitfield*/

```

};

```

__u32 msb_right; /* != 0 : Most significant bit is */

/* right */

```

An example for the structure fields that contains the detailed information of each color in a pixel is as follows:

Consider a case in a configuration where the mode is RGB888 with a pixel width of 3 bytes. Then, the structure parameters takes the following values:

```

red.length= 8 Jred.offset= 24

green.length= 8 ' green.offset = 16

blue.length= 8 ' blue.offset = 8

```

• struct fb\_ops—contains function pointers to the framebuffer operations. These operations are from the basic or common driver functions such as the open and release function operations that are oriented to the parameter settings or ioctl() calls. Some of these functions are as follows:

- int (\*fb\_open)(struct fb\_info \*info, int user)—opens the fb device and passes the fb info structure pointer as the argument

- int (\*fb\_set\_par) (struct fb\_info \*info)—sets the video mode and other parameters according to the contents of the var (fb\_var\_screeninfo) element, which is located in the fb info structure pointer. This structure pointer is passed as an argument in this function

- int (\*fb\_blank) (int blank, struct fb\_info \*info)—operates to blank the display by using the fb\_info structure pointer as an argument

- int (\*fb\_ioctl) (struct fb\_info \*info, unsigned int cmd, unsigned long arg)—performs the input/output operations such as sending request for the structure values or configuring structure values by passing the fb\_info structure pointer as the argument

- int (\*fb\_mmap(struct fb\_info \*info, struct vm\_area\_struct \*vma)—executes the mmap instructions by passing the fb\_info structure and virtual memory area structure pointers as the arguments

- struct fb\_videomode—is used when the user requires to add support for a new panel. Various information about the new panel such as the name, resolution, pixel clock, synchronization timings, and margins are referred in this structure. For more information about this structure, refer to Section 4.3.1.2, "Panel Configuration."

The fb\_videomode structure is as follows:

```

struct fb videomode {

const char *name;/* optional */

u32 refresh;/* optional */

u32 xres;

u32 yres;

u32 pixclock;

u32 left margin;

u32 right_margin;

u32 upper_margin;

u32 lower margin;

u32 hsync len;

u32 vsync len;

u32 sync;

u32 vmode;

u32 flag;

};

```

• struct fb\_info—is the most important structure in the framebuffer framework. The fb\_fix\_screeninfo, fb\_var\_screeninfo, fb\_bitfield, fb\_ops, and fb\_videomode structures are declared in this structure. Many structures and elements such as pointers to devices, event queue, or monitor specifications are declared in this structure. The structure also contains structures that are enabled depending on the conditional building such as if the support for backlight is enabled.

When a framebuffer driver gets registered to the kernel, the framebuffer driver uses a pointer to the structures that contain information (into several different structures) about the specific hardware panel, which is in use. This structure is visible only to the kernel and is as follows:

```

struct fb info {

....

....

struct fb var screeninfo var;/* Current var */

struct fb fix screeninfo fix; /* Current fix */

struct fb monspecs monspecs; /* Current Monitor specs */

struct work struct queue; /* Framebuffer event queue */

struct fb cmap cmap;

/* Current cmap */

•••

struct fb videomode *mode;/* current mode */

•••

struct fb ops *fbops;

/* This is the parent */

struct device *device;

/* This is this fb device */

struct device *dev:

};

```

Important points about the framebuffer framework are as follows:

- The framebuffer device is similar to the /dev/mem char device (or /dev/fb\* char device) when the device is used in a user-space. In this case, the file operations performed in any char device (open, read, write, and mmap) can be performed in the framebuffer device.

- A good example for a framebuffer driver is the virtual framebuffer that is located in the .../drivers/video/vfb.c file. This implementation requires some actions that should be followed for the development of any framebuffer driver. These actions are as follows:

- Filling the fix and var structures in the fb\_info structure that is targeted to the panel in use.

- Filling the file operation structures and the driver information for the fb\_info structure. This action initializes the hardware and memory area and registers the framebuffer driver using a pointer to the fb\_info structure.

## 4.2 Linux Framebuffer for i.MX

This section accounts the implementation side that describes the framebuffer main file (.../drivers/video/fbmem.c) and all the i.MX framebuffer implementation sources. These implementation sources provide information about the most important functions, structures, and a general flow chart for the initialization process.

The LCD driver and framebuffer implementation in the i.MX family uses the framebuffer framework for the hardware accessibility. Once the LCD driver is loaded (the LCD driver is selected in the kernel configuration screen for the graphics support while the kernel is configured), the hardware can be accessed

using the special node, fb\*, (which is like any other char device—refer to Section 4.1.2, "Linux Framebuffer Structures,") that is located in the /dev directory. This directory resides in the downloadable Linux image.

The usage of the /dev/fb\* node as an access mechanism allows some of the ioctl functions to interact, set, or get information from the device. Therefore, creation of a software abstraction layer helps the user to operate without the low-level knowledge.

The ioctl function performs the following operations:

- Requests information such as name, organization, addresses, and length

- Requests and changes the variable information about the hardware such as geometry, depth, color, and timing

- Obtains and sets the color map parts

The i.MX framebuffer implementation interacts with the generic framebuffer driver and is described in Section 4.2.1, "Initialization Process." This section provides a general description of the initialization process with a descriptive flow chart that shows the different stages of the framebuffer implementation.

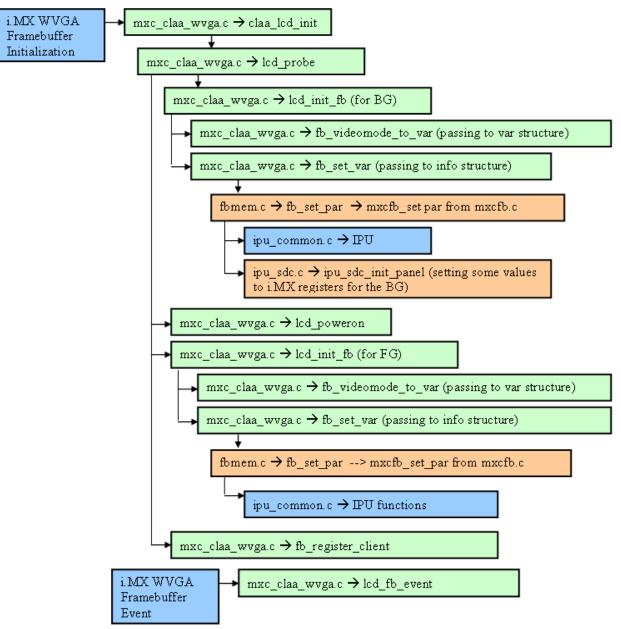

## 4.2.1 Initialization Process

This section describes the initialization flow for an LCD panel, which includes graphics element reviews for the framebuffer implementation. This section also describes files that are important for the framebuffer implementation.

The framebuffer initialization process contains several steps where specific functions for resource initialization and hardware probing or testing are called. Most of the files that take an important part in the framebuffer startup should be initialized and passed through the binding process. Therefore, functions such as init() and probe() are constantly described since these take an most part of the initialization startup.

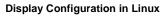

The steps for the framebuffer initialization are as follows:

- 1. Kernel startup—the framebuffer initialization process, which is performed in the mx3\_3stack.c file, starts when the kernel calls the functions associated with the board configuration (in this case, with the i.MX31 3-Stack board). The mxc\_board\_init() function does the initialization of the most important systems on the board. Among these systems, the framebuffer is started by registering a platform device.

- 2. Framebuffer initialization—is performed in the fbmem.c file, and the framebuffer driver initialization is done in this phase. However, the framebuffer driver is not attached to a specific platform in this phase. The framebuffer driver starts the resources and important structures (most of the structures are described in Section 4.1.2, "Linux Framebuffer Structures,") using the fbmem\_init function (that registers the device).

- 3. IPU initialization—is performed in the ipu\_common.c file. In this stage, the IPU modules are set up that includes the following:

- Registration of the IPU modules as a device in the system

- Initial configuration of the IPU modules and processes dedicated to attend the IPU tasks, such as the camera and LCD event handling

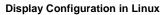

4. i.MX framebuffer initialization—is performed in the mxcfb.c file. In this phase, the next software layer, which is related to the framebuffer implementation in the i.MX family, is initialized and tested with all the components of that layer. This initialization process as well as most of the activities performed by the framebuffer calls to the IPU functions. The initialization process includes the registration of the framebuffer for the i.MX as a platform driver. However, most of the process is covered by the probe function where the framebuffer gets registered among the other resource settings. The framebuffer probe function executes the tests related to the IPU, such as initializing modes for the SDC module, executing tests for IPU\_IRQ, enabling channels, disabling channels, and registering the framebuffer.

For new LCD panels, a specific panel driver, which is similar to the mxcfb.c file, is made and is described as follows:

Specific panel driver (mxc\_claa\_wvga.c or mxc\_epson\_vga.c)—The driver for the i.MX platform can be seen as a generic driver that works for several panels (see the mxc\_modedb.c file). As the new panel has a different interface, a specific driver should be made for this type. In this case, the driver should be similar to the mxcfb.c file. However, the new driver should be more specific. Therefore, the usage of the initialization and probe functions are similar in this new driver. However, this driver does not replace the mxcfb.c file, but is complementary to this file. Therefore, to enable the panel for the proper functionality, both the drivers should be enabled.

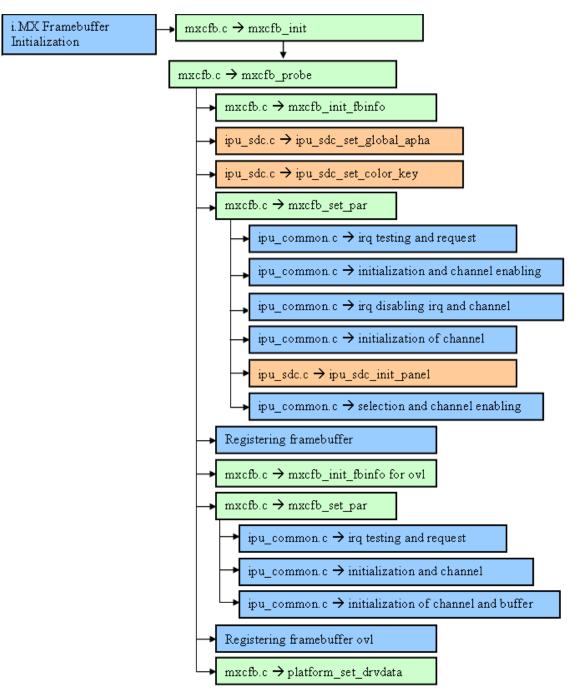

5. Video4Linux (v4l) initialization—is performed in the mxc\_v4l2\_output.c file. At this point, all the elements to set up the framebuffer and display are set. However, to use the video, an extra step is required. The packages that contain the generic drivers follow the v4l2 standard. This driver can be used for signal capturing as well as for the output. The driver is loaded after setting up the framebuffer and IPU. The output driver makes use of the IPU post-processing functions for its usage. This driver also contains the initialization and probe routines.

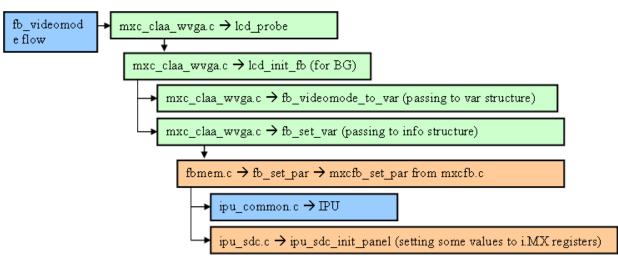

Figure 17 shows the initialization flow chart for an LCD panel.

Figure 17. Initialization Flow Chart

## 4.2.2 Files and Important Elements

This section describes the files mentioned in Section 4.1.1, "Definition and Concept," and Section 4.2.1, "Initialization Process," and the files that provide important information about the framebuffer infrastructure. These files are as follows:

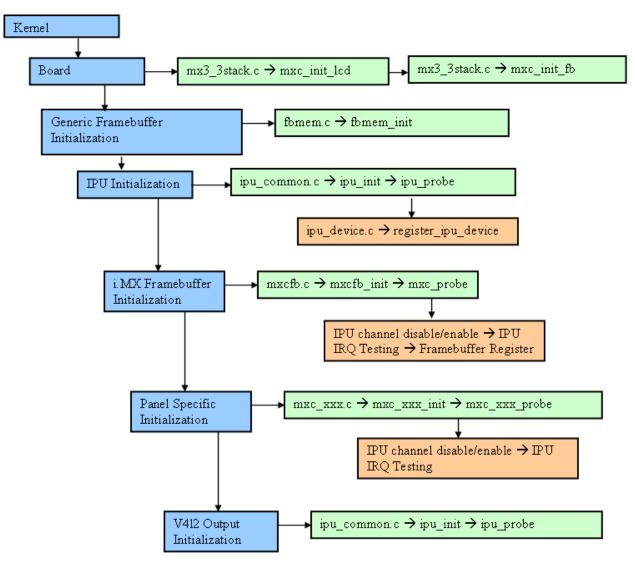

• /arch/arm/mach-mx3/mx3\_3stack.c:

This file contains the initialization and set up routines for the i.MX31 3-Stack board. These routines are called at the time of the kernel startup. The most important routine in this file is  $mxc_board_init$ . This routine calls several module specific routines, which includes the  $mxc_init_fb$  routine that registers a platform device for the framebuffer. Information such as name, DMA mask, and some platform data (a char variable of type, panel) are provided to this routine.

The  $mxc\_board\_init$  routine is set among the clock, GPIO modules, Power Management IC (PMIC), and so on. Also, there is a small LCD structure initialization in the  $mxc\_init\_lcd$  function. This registers the platform device structure for the LCD.

The mx3\_3stack.c file is as follows:

```

#if defined(CONFIG_FB_MXC_SYNC_PANEL) || defined(CONFIG_FB_MXC_SYNC_PANEL_MODULE)

static const char fb_default_mode[] = "Epson-VGA";

/* mxc lcd driver */

static struct platform_device mxc_fb_device = {

.name = "mxc_sdc_fb",

.id = 0,

.dev = {

.release = mxc nop release,

.platform data = &fb default mode,

.coherent_dma_mask = 0xFFFFFFFF,

},

};

static void mxc init fb(void)

(void)platform_device_register(&mxc_fb_device);

}

static struct platform device lcd dev = {

.name = "lcd claa",

.id = 0,

.dev = {

.release = mxc_nop_release,

.platform_data = (void*)&lcd_data,

},

};

static void mxc_init_lcd(void)

platform_device_register(&lcd_dev);

Figure 18 shows the flow chart of the mx3 3stack.c file.

```

Figure 18. mx3\_3stack Flow Chart

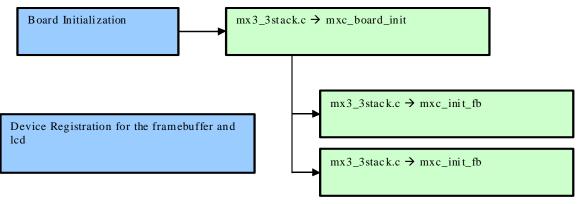

• /drivers/video/fbmem.c:

This file includes the following:

- Framebuffer subsystem initialization for the Linux

- All the file operations (fops) that are common for a char device

- mmap() memory map function that is widely used in this case (not always used in regular char devices)

- Panel framebuffer driver routines for the registered and unregistered framebuffer devices

- Functions related to the display of logos

Important functions and structures in the fbmem.c file are described as follows:

Module definition and registering functions:

- struct fb\_info \*registered\_fb[FB\_MAX] \_\_read\_mostly—is the global fb\_info structure

for the framebuffer system

- int num\_registered\_fb \_\_read\_mostly—is an int variable and holds the quantity of framebuffers that are registered in the system

- static int \_\_init fbmem\_init (void) —initializes the framebuffer subsystem as a char driver that is passed as a parameter into the fops table. These parameters are passed with the pointers to each fops function. This function also creates a class for the graphics.

- static void \_\_exit fbmem\_exit(void) terminates the char driver and deletes the graphics class

- int register\_framebuffer(struct fb\_info \*fb\_info)—registers the framebuffer device by using the fb\_info structure as the argument

- int unregister\_framebuffer(struct fb\_info \*fb\_info)—unregisters the framebuffer device by using the fb\_info structure as the argument

- fops:

- file\_operations fb\_fops—is a structure that contains the fops for the framebuffer subsystem, which is implemented as a char driver. The common read, write, open, and ioctl operations are declared in this structure. The mmap operation is also an important member in this structure.

The file operations fb fops structure is as follows:

| <pre>static const struct file_operations fb_fops = {     .owner =     .read =     .write =     .ioctl =</pre> | THIS_MODULE,<br>fb_read,<br>fb_write,<br>fb_ioctl, |

|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| <pre>#ifdef CONFIG_COMPAT    .compat_ioctl = fb_compat_ioctl, #endif</pre>                                    | 15_10001,                                          |

| .mmap =<br>.open =<br>.release =                                                                              | fb_mmap,<br>fb_open,<br>fb_release,                |

| <pre>#ifdef HAVE_ARCH_FB_UNMAPPED_AREA   .get_unmapped_area = get_fb_unmapped_area,</pre>                     |                                                    |

```

#endif

#ifdef CONFIG_FB_DEFERRED_IO

.fsync = fb_deferred_io_fsync,

#endif

};

- static int fb ioctl(struct inode *inode, struct file *file, unsigned int

```

- cmd, unsigned long arg)—is a regular ioctl function for the char devices. In this function, the command to be executed is passed as an argument and acts depending on the selected case. The cases—FBIOGET\_VSCREENINFO and FBIOGET\_FSCREENINFO—are used to get the information about the variable or fixed values in the fb\_information structure.

- static int fb\_mmap(struct file \*file, struct vm\_area\_struct \* vma)—is a function that performs the mmap implementation for the framebuffer char driver

Figure 19 shows the flow chart of the fbmem.c file.

Figure 19. fbmem Flow Chart

The IPU files are as follows:

• drivers/mxc/ipu/ipu\_common.c:

This file contains the common software routines—channel, buffer, and Interrupt Request (IRQ) management—that are required for the IPU functionality. The file also contains the platform\_driver structure that is implemented for the IPU and the init and exit functions for the module.

Important functions and structures in the ipu\_common.c file are as follows:

- Module definition and registering functions:

- platform\_driver mxcipu\_driver—is a structure that contains the power management pointers to the routines that are used for testing the platform driver behavior in low-power modes. The platform\_driver mxcipu\_driver structure is as follows:

```

static struct platform_driver mxcipu_driver = {

.driver = {

.name = "mxc_ipu",

},

.probe = ipu_probe,

.suspend = ipu_suspend,

.resume = ipu_resume,

};

```

- int32\_t \_\_init ipu\_gen\_init(void)—is the initialization routine for the IPU platform driver. This routine registers the mxcipu\_driver structure.

- static void \_\_exit ipu\_gen\_uninit (void) is the exit routine for the IPU platform driver. This routine frees the IPU IRQs and unregisters the mxcipu driver structure.

- static int ipu\_probe(struct platform\_device \*pdev)—is the probe function for the mxcipu\_driver structure and the function is called when the registration is performed. This function sets the IRQ request and clocks for the IPU and also registers the IPU device (see the ipu\_device.c file for more information)

- Common IPU functions:

- ipu\_request\_irq—registers an interrupt handler for the specified interrupt line. This

interrupt line is defined in the ipu\_irq\_line enumeration that is located in the ipu.h file.

- ipu\_disable\_irq—disables the interrupt for the specified interrupt line.

- ipu enable irq—enables the interrupt for the specified interrupt line.

- ipu\_init\_channel\_buffer—initializes a buffer for the logical IPU channel. The function

parameters include the physical addresses for the buffers, such as the buffer type, logical

channel ID, width and height in pixels, and so on.

- ipu\_select\_buffer—sets the channel buffers as ready. The parameters for this function are the logical channel ID and buffer type.

- ipu\_init\_channel—initializes logical IPU channel. The function parameters include the logical channel ID and a union, along with the channel initialization parameters (the channel initialization parameter, ipu\_channel\_params\_t, is included in the ipu.h file).

- ipu\_uninit\_channel—uninitializes the logical IPU channel.

- ipu\_link\_channels—links two channels together for automatic frame synchronization. This function has two parameters—the source logical channel ID and destination logical channel ID. The source channel output is linked to the destination channel input.

- ipu\_unlink\_channels—unlinks the two channels that is set up for the automatic frame synchronization and also disables the automatic frame synchronization.

- ipu\_enable\_channel—enables the logical channel corresponding to the channel ID, which is sent as the input parameter.

- ipu\_disable\_channel—disables the logical channel corresponding to the channel ID, which is sent as the input parameter.

Figure 20 shows the flow chart for the ipu\_common.c file.

Figure 20. ipu\_common Flow Chart

drivers/mxc/ipu/ipu\_device.c:

This file contains structures and functions for the fops operations that are related to the mxc\_ipu device. The file also contains a generic interrupt handler for the IPU related IRQs.

Important functions and structures in the ipu\_device.c file are as follows:

- Registering and other important functions:

- int register\_ipu\_device()—registers mxc\_ipu as a char device and provides the fops table and name. The function also creates a class in the device model structure. This function is called using the probe() function, which is located in the ipu\_common.c file.

- static irqreturn\_t mxc\_ipu\_generic\_handler(int irq, void \*dev\_id)—is a generic handler for any IRQ that the IPU should process.

- fops:

- file\_operations mxc\_ipu\_fops—is a structure that contains the fops for the mxc\_ipu device. The file\_operations mxc\_ipu\_fops structure is as follows:

```

static struct file_operations mxc_ipu_fops = {

.owner = THIS_MODULE,

.open = mxc_ipu_open,

.release = mxc_ipu_release,

.ioctl = mxc_ipu_ioctl

};

```

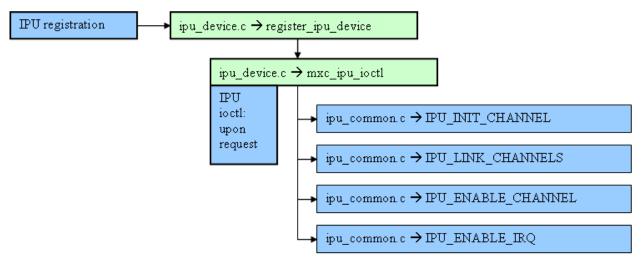

- static int mxc\_ipu\_ioctl(struct inode \*inode, struct file \*file, unsigned int cmd, unsigned long arg)—is the ioctl function for the mxc\_ipu device. In this function, the commands are passed as arguments. Most of these commands—IPU\_INIT\_CHANNEL, IPU LINK CHANNELS, and so on—are described in the ipu common.c file.

Figure 21 shows the ipu\_device.c flow chart.

Figure 21. ipu\_device Flow Chart

drivers/mxc/ipu/ipu\_sdc.c:

This file contains routines that are related to the SDC module that is located in the IPU module. The set of routines ranges from sdc\_init to the routines that are used for setting the alpha blending modes or color keys in the SDC plane.

drivers/mxc/ipu/ipu\_ic.c:

This file contains routines that does the color conversion and resizes all the IPU submodules.

drivers/video/mxc/mxcfb\_modedb.c:

This file contains an array of fb\_videomode structure declarations that are related to the MXC framebuffer implementation. These structures include the Sharp-VGA, NEC-VGA, TV out modes, and so on. The data in each structure refers to the most important elements—resolution, size, timing delays, and so on—that describe the panel. More information about the structure parameters are available in the include/linux/fb.h file.

drivers/video/mxc/mxcfb.c:

This driver contains the registering and initialization routines for the framebuffer implementation that are oriented to the i.MX family. The mxcfb.c file initializes the following:

- Most important structures that are related to the framebuffer

- Functions for registering the driver and setting up the framebuffer system for the normal framebuffer data structures as well as for the overlay, if the overlay is enabled

Important functions and structures in the mxcfb.c file are as follows:

- Module definition and registering functions:

- platform\_driver mxcfb\_driver—this structure is created for the framebuffer driver implementation. The structure consists of pointers to the functions that are related to power management callbacks, such as probe and suspend. The platform\_driver mxcfb\_driver structure is as follows:

```

static struct platform_driver mxcfb_driver = {

.driver = {

.name = MXCFB_NAME,

},

.probe = mxcfb_probe,

.suspend = mxcfb_suspend,

.resume = mxcfb_resume,

};

```

- mxcfb\_data—encapsulates the two fb\_info structures, in which one acts for the normal framebuffer and the other for the overlay. The mxcfb\_data structure also includes flags. The mxcfb\_data structure is as follows:

```

struct mxcfb_data {

struct fb_info *fbi;

struct fb_info *fbi_ovl;

volatile int32_t vsync_flag;

wait_queue_head_t vsync_wq;

wait_queue_head_t suspend_wq;

bool suspended;

int backlight_level;

};

```

- int \_\_init mxcfb\_init (void) is the entry function for the framebuffer. This function registers the platform driver structure that contains callback functions for the power management and shutdown conditions.

- void mxcfb\_exit (void)—is the exit function for the framebuffer. This function unmaps the video memory for the framebuffer structures, unregisters the fb\_info structure from the framebuffer and overlay devices (these devices are unregistered), and unregisters the platform driver structure for the framebuffer.

- static int mxcfb\_probe(struct platform\_device \*pdev)—is a function member of the platform driver structure pointers. This probe function verifies if the specified device hardware exists and executes several processes such as framebuffer initialization, memory allocation, and framebuffer registration (fb\_info structures for the normal and overlay structures). This function also performs the IPU initialization that involves transparent color key setting for the SDC graphic plane and foreground/background alpha blending modes.

- static struct fb\_info \*mxcfb\_init\_fbinfo(struct device \*dev, struct fb\_ops \*ops)—is a function that is called by the mxc\_probe() function and performs functions that include the memory allocation for the fb\_info structure and filling the fields related to this structure with information such as color maps, bits per pixel, and so on.

- platform\_set\_drvdata(pdev, &mxcfb\_drv\_data)—is a function that passes address, which is obtained from the information in the mxcfb\_drv\_data structure, to the platform device.

- fops:

- fb\_ops mxcfb\_ops—is a structure that contains pointers to the functions that are used by the framebuffer driver to perform functions such as rectangle filling, cursor definitions, and so on. This structure is used for normal framebuffer implementation and is as follows:

```

static struct fb_ops mxcfb_ops = {

.owner = THIS_MODULE,

.fb_set_par = mxcfb_set_par,

.fb_check_var = mxcfb_check_var,

.fb_setcolreg = mxcfb_setcolreg,

.fb_pan_display = mxcfb_pan_display,

.fb_ioctl = mxcfb_ioctl,

.fb_fillrect = cfb_fillrect,

.fb_copyarea = cfb_copyarea,

.fb_imageblit = cfb_imageblit,

.fb_blank = mxcfb_blank,

};

```

fb\_ops mxcfb\_ovl\_ops—is a structure that contains pointers to the functions that are used by the framebuffer driver to perform functions such as rectangle filling, cursor definitions, and so on. This structure is used for overlay framebuffer implementation and is as follows:

```

static struct fb_ops mxcfb_ovl_ops = {

.owner = THIS_MODULE,

.fb_set_par = mxcfb_set_par,

.fb_check_var = mxcfb_check_var,

.fb_setcolreg = mxcfb_setcolreg,

.fb_pan_display = mxcfb_pan_display,

.fb_ioctl = mxcfb_ioctl_ovl,

.fb_fillrect = cfb_fillrect,

.fb_copyarea = cfb_copyarea,

.fb_imageblit = cfb_imageblit,

.fb_blank = mxcfb_blank_ovl,

};

```

- static int mxcfb\_mmap(struct fb\_info \*fbi, struct vm\_area\_struct \*vma)—is a function that handles the mmap function for the MXC framebuffer.

- static int mxcfb\_ioctl\_ovl(struct fb\_info \*fbi, unsigned int cmd, unsigned long arg)—is a function that handles the ioctl commands for the framebuffer and is used for the overlay framebuffer structure.

- static int mxcfb\_ioctl(struct fb\_info \*fbi, unsigned int cmd, unsigned long arg)—is a function that handles the ioctl commands for the framebuffer and is used for the normal framebuffer structure.

- static int mxcfb\_set\_par(struct fb\_info \*fbi)—is a function that sets the parameter (most of the parameters are from the videomode structure) to the processor registers by calling the ipu\_sdc\_init\_panel() function. This function also changes the operating mode.

Figure 22 shows the flow chart for the mxcfb.c file.

Figure 22. mxcfb Flow Chart

drivers/media/video/mxc/output/mxc\_v4l2\_output.c:

This file implements the v4l2 standard for the output devices that are targeted to the i.MX family. This file includes the following:

Common char driver infrastructure, which includes the initialization routine for the drivers that are registered

- Probe function and standard fops that are related to the v412 implementation

- Functions that enable or disable the playback of video

Important functions and structures in the mxc\_v4l2\_output.c file are as follows:

- Module definition and registering functions: