# **Freescale Semiconductor**

**Application Note**

Document Number: AN4016 Rev. 0, 03/2010

# Interfacing and Configuring the i.MX25 Flash Devices

Multimedia Applications Division bv Freescale Semiconductor, Inc. Austin, TX

This application note explains the various Flash devices that can interface with the i.MX25. It also explains how to interface and configure the Flash devices.

#### Contents

| 1. Boot Mode and Memory Interfaces       | 2 |

|------------------------------------------|---|

| 2. Flash Devices and Connection Diagrams | 2 |

| 2.1. NAND Flash                          | 2 |

| 2.2. I <sup>2</sup> CEEPROM              | 3 |

| 2.3. SPIFlash                            | 5 |

| 2.4. SD/MMC Card                         | 6 |

| 2.5. NOR Flash                           | 7 |

| 3. Revision History                      | 9 |

|                                          |   |

© 2010 Freescale Semiconductor, Inc. All rights reserved.

Boot Mode and Memory Interfaces

## **1** Boot Mode and Memory Interfaces

The i.MX25 can boot from an external device. It can also download from the Flash memory using the serial full-speed Universal Serial Bus (USB), USB On-The-Go (OTG), or Universal Asynchronous Receiver/Transmitter (UART) connection. See *i.MX25 Boot Options* (AN3684), for information on the boot modes and eFUSEs.

The i.MX25 can interface to the following memories:

- NAND FLASH by the Near Field Communication (NFC)

- NOR FLASH / PSRAM by the WEIM

- SD / MCC by eSDHC

- EEPROM / Serial FLASH by the SPI interface

- EEPROM by the I<sup>2</sup>C Interface

Before customizing the Advanced Tool Kit (ATK), check if the hardware support is available in the latest ATK tool release. See the *ATK User Guide Standard Version* document for a list of supported i.MX platforms and hardwares.

## 2 Flash Devices and Connection Diagrams

The various Flash devices and their connection diagrams are described in the following sections.

### 2.1 NAND Flash

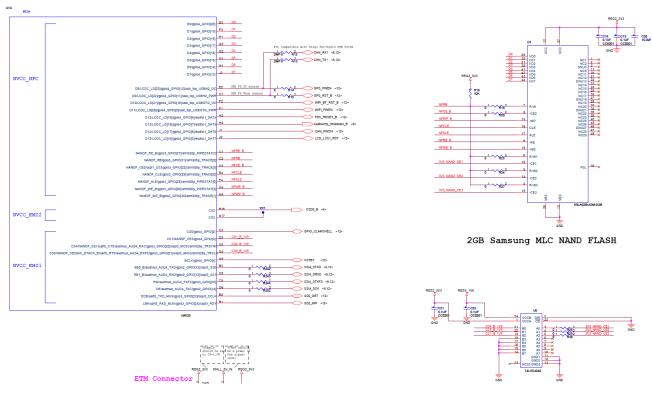

The i.MX25 supports single-level cell (SLC) and multi-level cell (MLC) NAND Flash products of up to 64 Kbyte blocks.

- SLC—512 bytes per page, 16 Kbytes per block and memory size up to 8 Gbits

- SLC—2 Kbytes per page, 128 Kbytes per block and memory size up to 64 Gbits

- MLC— 4 Kbytes per page, 512 Kbytes per block and memory size up to 256 Gbits

The size of spare bytes for the 4 Kbytes page size NAND can be 128 or 218 bytes for booting. The NAND bus can be 8 or 16-bits. Also, the i.MX25 supports Open NAND Flash Interface (ONFI) 1.0 devices.

The i.MX25 PDK implementation uses an SLC or MLC with an 8-bit data bus. By default, PDK uses the SLC K9LAG08UOM-2 Gbyte Samsung device. If MLC is to be used, when the PDK is connected to the signals for that option, then a level shifter or a transceiver is required for the clock enable (CE) signals to meet the voltage level of the memory. The CE1, CE2, and CE3 signals belong to a different power rail from the DATA and command signals from the NFC that are listed below:

- NVCC\_NFC: 3.3 V

- NVCC\_EM1: 1.8 V

Figure 1 shows the NAND interface connection diagram.

Figure 1. NAND Interface

## 2.2 I<sup>2</sup>C EEPROM

The I<sup>2</sup>C interface operates at a speed of up to 400 kbps, but it depends on the pin loading and the timing characteristics. See *Philips I2C Bus Specification, Version 2.1*, for pin requirement details.

The i.MX25 has three I<sup>2</sup>C ports that can be used for booting. The i.MX25 boot ROM code uses the 2-Address bytes protocol for accessing. Other types of I<sup>2</sup>C devices are not supported. Using the 2-Address words, defines the size of  $512 \le \text{Size} \le 64$  Kbytes (2<sup>16</sup>).

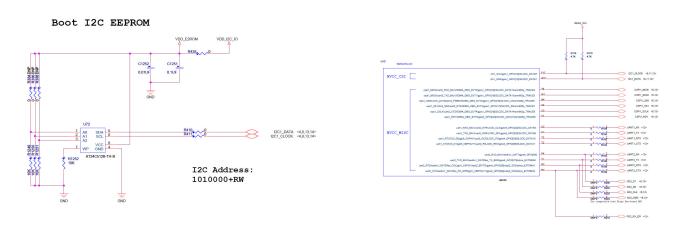

Figure 2 shows the  $I^2C$  EEPROM interface diagram.

#### Figure 2. I<sup>2</sup>C EEPROM Interface

The  $I^2C$  interface from the i.MX25 can operate at 3.3 V and 1.8 V.

The PDK device AT24C512B, has 3.3 V option. The SDA and SCL signals require external pull-up resistors. The PDK design uses a 4.7 K $\Omega$  resistor on the CPU board. The I<sup>2</sup>C bus specification provides the maximum and minimum values of pull-up resistors.

Also, it is important to configure the address for the  $I^2C$  EEPROM. The design has pull-up and pull-down option resistors to set the address. By default, the signals for A0 to A2 are connected to the ground.

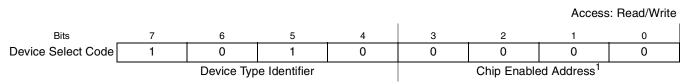

Table 1 gives the default address during the boot up operation.

#### Table 1. Default Address

<sup>1</sup> These address bits should be configured in the memory device to match the 000 value.

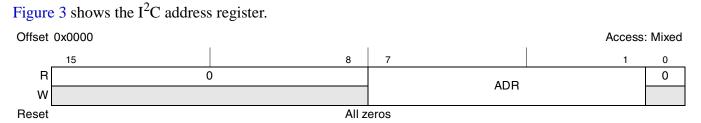

If the device address has to be changed because the design is not using the boot mode, then change the  $I^2C$  address register.

Flash Devices and Connection Diagrams

Figure 3. I<sup>2</sup>C Address Register

Table 2 gives the field descriptions for the  $I^2C$  address register.

#### Table 2. Memory Initialization File Format

| Field Description | Description                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–8              | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7–1 ADR           | Slave address. These fields contains the specific slave address to be used by the I <sup>2</sup> C module. Slave mode is the default I <sup>2</sup> C mode for an address match on the bus.<br><b>Note:</b> The IADR holds the address. The I <sup>2</sup> C responds when it is addressed as a slave. The slave address is not sent on the bus during the address transfer. The register is not reset by a software reset. |

| 0                 | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                    |

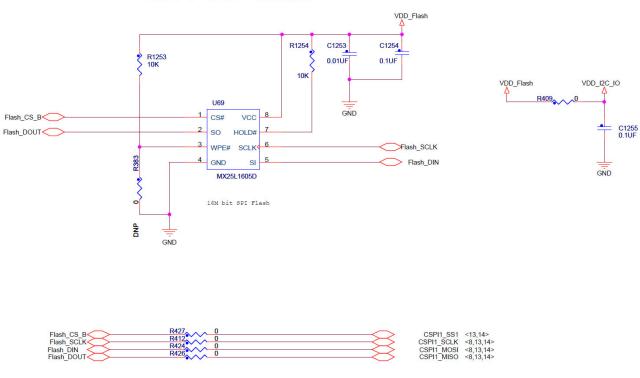

### 2.3 SPI Flash

The i.MX25 has three configurable serial peripheral interface (CSPI) ports. The CSPI module is a full-duplex, synchronous, four-wire serial communication module. It contains an 8×32 receive buffer (RXFIFO) and an 8×32 transmit buffer (TXFIFO).

Any CSPI module can be used for booting. These modules can read the data from devices in 2 or 3 byte addressing and the burst length is 32 bytes. The Serial ROM should reside on Chip Select #1 of the CSPI module. The serial device is connected as SPI slave interface.

According to the i.MX25 datasheet, the maximum speed for the Master/slave SPI clock is 16.6 MHz. The PDK application uses the CSPI1 and the voltage is 3.3 V as the power rail is NVCC\_MISC. If the SPI modules are to be used, then ensure that the correct voltage is used for the memory, because the voltage is supplied by another power rail and a level shifter has to be added.

Flash Devices and Connection Diagrams

Figure 4 shows the SPI interface diagram.

Boot SPI Flash

Figure 4. SPI Interface

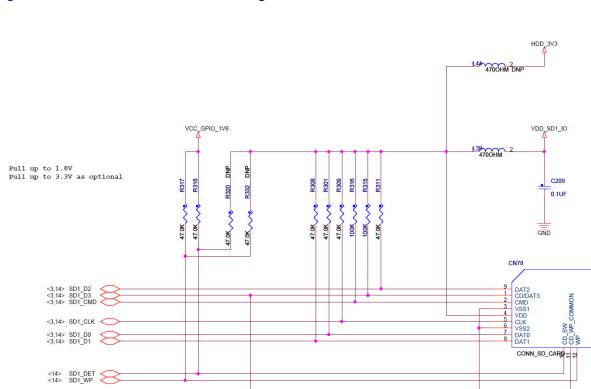

### 2.4 SD/MMC Card

The i.MX25 has two enhanced security digital host controller (eSDHC) interfaces and supports the following:

- High capacity SD, eSD (Embedded SD, versions 2.0 and 2.1 Draft Rev. 0.3)

- MMC/eMMC (version 4.3 (MoviNAND), JEDSD84-A43) cards

The SD/MMC interface can operate with low voltage devices. On the PDK board, the interface is connected at 3.3 V power rail and it is supplied by the HDD\_3V3 or VDD\_SD1\_IO voltages. VDD\_SD1\_IO is the default option.

Also, the PDK has resistor options for two signals: SD1\_DET and SD\_WP. These are connected to 1.8 V, because they are part of the NVVC\_EMI power rail and they are general purpose input/output (GPIO) used for Write Protection (WP) and Detection (DET) functions.

16 15

GND

<del>α</del> 4

GND

GND

GND

R319

100K

GND

Figure 5 shows the SD Card interface diagram.

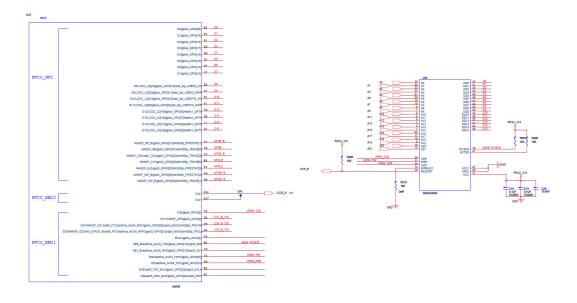

### 2.5 NOR Flash

The i.MX25 microprocessor interfaces NOR Flash and OneNAND devices through the WEIM. For NOR Flash booting, use the chip select 0 (CS0). The NOR Flash interface operates in asynchronous mode, and supports 16-bit muxed Address/Data and non-muxed schemes, based on the fuse settings. Also the 24-bit address option is available for booting. The OneNAND Flash devices are available only with 16-bit interface. By default, the Input/Output Multiplexer (IOMUX) settings at power-on reset (POR) supports NOR boot.

By default, the PDK does not show the NOR Flash implementation. It has the option in the Debug Board.

#### Flash Devices and Connection Diagrams

Figure 6 shows NOR Flash interface with the i.MX25. The interface connects the Address signals that are shared with the double data rate (DDR) interface. The data bus is shared with the NFC and the control signals of the WEIM as follows:

- Address bus: A0–A21

- Data Bus: D0–D15

- Control Signals: WEIM\_CS0,WEIM\_RW,WEIM\_OE# and WEIM\_RY/BY#

#### Figure 6. NOR Interface

The device is S29GL064N and the operating voltage is 3.3 V. Ensure that data signals are part of the NVCC\_NFC voltage rail and the address bus is attached to the NVCC\_EMI. So, if a DDR is used at 1.8 V, then a buffer or a level shifter is required to change the NOR Flash voltage.

The Registers required to configure the WEIM are CSCR0U, CSCR0L, CSCR0A, and WCR. The values after reset are as follows:

- CSCR0U: 0x0000\_1E00

- CSCR0L: 0xA000\_0841

- CSCR0A: 0x0000\_5000

- WCR: 0x0000\_0100

## 3 Revision History

Table 3 provides a revision history for this application note.

#### Table 3. Document Revision History

| Rev.<br>Number | Date    | Substantive Change(s) |

|----------------|---------|-----------------------|

| 0              | 03/2010 | Initial release.      |

Interfacing and Configuring the i.MX25 Flash Devices, Rev. 0

**Revision History**

#### THIS PAGE INTENTIONALLY LEFT BLANK

**Revision History**

#### THIS PAGE INTENTIONALLY LEFT BLANK

#### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center 1-800 441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale, the Freescale logo, CodeWarrior, ColdFire, PowerQUICC, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc. Reg. U.S. Pat. & Tm. Off. CoreNet, QorlQ, QUICC Engine, and VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. ARM is the registered trademark of ARM Limited. ARMnnn is the trademark of ARM Limited. © 2010 Freescale Semiconductor, Inc.

Document Number: AN4016 Rev. 0 03/2010