# Freescale Semiconductor Application Note

AN3361 Rev.5, 01/2015

# MPC8321E/MPC8323E PowerQUICC™ II Pro Design Checklist

Freescale Semiconductor, Inc.

This application note describes the generally recommended connections for new designs based on the Freescale PowerQUICC<sup>TM</sup> II Pro MPC8323E processor family. These devices include the following:

- MPC8321/MPC8321E

- MPC8323/MPC8323E

The design checklist may also apply to bus- or footprint-compatible processors introduced in the future. In addition, it can serve as a useful guide to debugging a newly-designed system by highlighting those areas of a design that merit special attention during initial system startup.

To locate any published errata or updates for this document, refer to the Freescale web site listed on the back cover of this document.

### 1 Introduction

This section outlines recommendations to simplify the first phase of design. Before designing a system with a PowerQUICC II Pro device, it is recommended that the designer be familiar with the available documentation, software, models, and tools.

#### Contents

| 1. | Introduction                               |

|----|--------------------------------------------|

| 2. | Power 4                                    |

| 3. | Clocking 8                                 |

| 4. | Power-On Reset and Reset Configurations 11 |

| 5. | JTAG and Debug                             |

| 6. | Functional Blocks                          |

| 7. | Revision history                           |

### 1.1 References

Some of the following reference documents may be available only under a nondisclosure agreement (NDA). Contact your local field applications engineer or sales representative to obtain a copy:

- Collateral

- MPC8323E PowerQUICC™ II Pro Integrated Host processor Family Reference Manual (MPC8323ERM)

- *MPC8323E PowerQUICC*™ *II Pro Family Device Errata* (MPC8323ECE)

- MPC8323E Integrated Host Processor Hardware Specifications (MPC8323EEC)

- Available Tools

- QE Utility Tool

- UPM Programming Tool

- Models

- IBIS

- BSDL

### 1.2 Device Errata

The device errata documents (MPC8323ECE) describe the latest fixes and workarounds for the MPC8323E family of devices. Before you start a design, be sure to research the most recent errata documents thoroughly.

### 1.3 QUICC Engine Utility Tool

The QE Utility Tool includes the Pin Mux Tool, QE Driver API Tool, and QE Performance Calculator (license required).

### 1.4 UPM Programming Tool

The UPM Programming Tool features a GUI for a user-friendly programming interface for programming all three PowerQUICC II Pro UPM machines. The GUI consists of a wave editor, table editor, and report generator. The user can directly edit the waveform or the RAM array. The report generator prints out the UPM RAM array for use in a C program after programming is complete. The UPM Programming Tool is available on the MPC8323E and MPC8321E device product pages of the Freescale web site.

### 1.5 Available Training

Our third-party partners are part of an extensive Design Alliance Program. Our current training partners are listed on our web site under the Design Alliance Program. Also available are training materials from past Smart Network Developer's Forums and Freescale Technology Forums. These training documents are a valuable resource in understanding the PowerQUICC II Pro.

Power

### 1.6 Product Revisions

Table 1 lists the product revisions.

**Table 1. Product Revisions**

| Device   | Package | SVR (Rev 1.1, Rev 1.3) | PVR (Rev 1.1, Rev 1.3) |

|----------|---------|------------------------|------------------------|

| MPC8323E | PBGA    | 0x8062_0011            |                        |

| MPC8323  | PBGA    | 0x8063_0011            | 0x8084_0010            |

| MPC8321E | PBGA    | 0x8066_0011            |                        |

| MPC8321  | PBGA    | 0x8067_0011            |                        |

### 2 Power

This section provides design considerations for the MPC8323E power supplies, as well as power sequencing. For information on MPC8323E AC and DC electrical specifications and thermal characteristics, refer to the MPC8323E hardware specification (MPC8323EEC). For power sequencing recommendations, refer to Section 2.3, "Power Sequencing."

### 2.1 Power Supply

The MPC8323EEC lists the recommended and maximum range for each power supply listed in Table 2.  $OV_{DD}$  has a noise margin of 300 mV. All other power supplies have a 5 percent margin. No external signals on the MPC8323E are 5-V-tolerant. Note that absolute maximum ratings are stress ratings only. The functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or permanently damage the device.

**Table 2. Clock Signal Pin Listing**

| Туре | Name              | Block                                                                                      |

|------|-------------------|--------------------------------------------------------------------------------------------|

| Core | $V_{DD}$          | e300 core voltage                                                                          |

| PLL  | AV <sub>DDn</sub> | QUICC Engine PLL power supply e300 PLL power supply System PLL power supply                |

| I/O  | GV <sub>DD</sub>  | DDR DRAM I/O supply voltage DDR2 DRAM I/O supply voltage                                   |

| I/O  | OV <sub>DD0</sub> | PCI, local bus, DUART, system control and power management, I2C, SPI, and JTAG I/O voltage |

### 2.2 Power Dissipation

The MPC8323E hardware specification provides the power dissipation of  $V_{DD}$  for various configurations of the coherent system bus (CSB), QUICC Engine block, and the e300 core frequencies. The hardware specification also estimates power dissipation for all the I/O power rails. I/O power highly depends on the application and is an estimate. A full analysis of your board implementation is required to define your I/O power supply needs. The typical  $V_{DD}$  power plus I/O power should be used for the thermal solution design.

The junction temperature must not exceed the maximum specified value. The maximum  $V_{DD}$  power is the worst case power consumption and should be used for the core power supply design.

### 2.3 Power Sequencing

One consequence of multiple power supplies is that when power is initially applied, the voltage rails ramp up at different rates. These rates depend on the power supply, the type of load on each power supply, and the way different voltages are derived.

From a system standpoint, if the I/O power supplies ramp before the  $V_{DD}$  core supply stabilizes, there may be a period of time before all voltages stabilize when all functional pins, including pure input pins, are driven to a random logic-one or logic-zero state, with possible adverse effects on externally-connected logic. However, after the power is stable, and as long as  $\overline{PORESET}$  is asserted, most I/O pins are tri-stated. To minimize the time that I/O pins are actively driven, apply core voltage before I/O voltage and assert  $\overline{PORESET}$  before the power supplies fully ramp up. The core voltage (Vdd) should reach its nominal level before the I/O voltage (OVdd and GVdd) reaches 0.7 V. In addition, the IO voltage should reach its nominal level within 100 microseconds after the core voltage reaches its nominal level. Excessive current consumption may be observed if these recommendations are not followed.

The hardware specification shows the current maximum ratings for the power supplies. Supplies must not exceed these absolute maximum ratings. However, during normal operation, use the recommended operating conditions tables in the hardware specification.

### 2.4 Power Planes

Each  $V_{DD}$  pin should be provided with a low-impedance path to the board power supply. Similarly, each ground pin should be provided with a low-impedance path to ground. The power supply pins drive distinct groups of logic on-chip. The capacitor leads and associated printed circuit traces connecting to chip  $V_{DD}$  and ground should be kept to less than half an inch per capacitor lead.

### 2.5 Decoupling

Due to large address and data buses and high operating frequencies, the PowerQUICC II Pro can generate transient power surges and high-frequency noise in its power supply, especially while driving large capacitive loads. This noise must be prevented from reaching other components in the PowerQUICC II Pro system, and the PowerQUICC II Pro itself requires a clean, tightly regulated source of power. Therefore, it is recommended that the system designer place at least one decoupling capacitor at each  $V_{DD}$ ,  $GV_{DD}$ , and GND power planes in the PCB, using short traces to minimize inductance. Capacitors can be placed directly under the device on the other side of the board using a standard escape pattern. Others may surround the part on both top and bottom sides of the board.

These capacitors should have a value of 0.01 or 0.1  $\mu$ F. Only ceramic surface mount technology (SMT) capacitors should be used to minimize lead inductance, preferably 0402 or 0603 sizes. In addition, several bulk storage capacitors should be distributed around the PCB, feeding the  $V_{DD}$ ,  $GV_{DD}$ , and  $GV_{DD}$  planes, to enable quick recharging of the smaller chip capacitors. These bulk capacitors should have a low equivalent series resistance (ESR) rating to ensure the quick response time necessary. They should also be connected to the power and ground planes through two vias to minimize inductance. Suggested bulk

MPC8321E/MPC8323E PowerQUICC™ II Pro Design Checklist, Rev.5

#### Power

capacitors:  $100-300 \,\mu\text{F}$  (AVX TPS tantalum or Sanyo OSCON). Simulation is strongly recommended to minimize noise on the power supplies before proceeding into the PCB design and manufacturing stage of development.

### 2.6 PLL Power Supply Filtering

Each PowerQUICC II Pro PLL is provided with power through independent power supply pins ( $AV_{DDn}$ ). The  $AV_{DD}$  level should always be equivalent to  $V_{DD}$ , and preferably these voltages are derived directly from  $V_{DD}$  through a low frequency filter scheme.

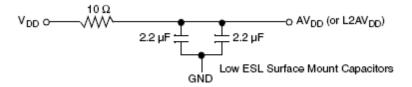

There are several ways to provide power reliably to the PLLs, but the recommended solution is four independent filter circuits as illustrated in Figure 1, one to each of the four AV<sub>DD</sub> pins. Providing independent filters to each PLL reduces the opportunity to cause noise injection from one PLL to the other. This circuit is intended to filter noise in the PLLs resonant frequency range from a 500 kHz to 10 MHz range. It should be built with surface mount capacitors with minimum effective series inductance (ESL). Consistent with the recommendations of Dr. Howard Johnson in *High Speed Digital Design: A Handbook of Black Magic* (Prentice Hall, 1993), multiple small capacitors of equal value are recommended over a single large value capacitor.

To minimize noise coupled from nearby circuits, each circuit should be placed as closely as possible to the specific  $AV_{DD}$  pin being supplied. It should be possible to route directly from the capacitors to the  $AV_{DD}$  pin, which is on the periphery of package, without the inductance of vias. Figure 1 shows the PLL power supply filter circuit.

Figure 1. PLL Power Supply Filter Circuit

### 2.7 Pin Listing and Connections

Table 3 lists the power signal pin connections.

**Table 3. Power Signal Pin Listing**

| Signal            | Connection                    | Notes                              |

|-------------------|-------------------------------|------------------------------------|

| AV <sub>DD1</sub> | 1.0 V ± 50 mV                 | Power for the QUICC Engine PLL     |

| AV <sub>DD2</sub> | 1.0 V ± 50 mV                 | Power for the System PLL           |

| AV <sub>DD3</sub> | 1.0 V ± 50 mV                 | Power for the e300 PLL             |

| AV <sub>DD4</sub> | 1.0 V ± 50 mV                 | _                                  |

| GV <sub>DD</sub>  | 2.5 V ± 125 mV<br>1.8 ± 90 mV | Power for DDR and DDR2 I/O voltage |

### **Table 3. Power Signal Pin Listing (continued)**

| Signal          | Connection                                         | Notes                                                                                    |

|-----------------|----------------------------------------------------|------------------------------------------------------------------------------------------|

| V <sub>DD</sub> | 1.0 V ± 50 mV                                      | Power for the core                                                                       |

| $OV_DD$         | 3.3 V ± 330 mV                                     | Power for PCI, local bus, DUART, system control, I2C, QUICC Engine, and JTAG I/O voltage |

| MVREF[1:2]      | 0.49 x GV <sub>DD</sub> to 0.51 x GV <sub>DD</sub> | DDR I/O reference voltage                                                                |

Clocking

# 3 Clocking

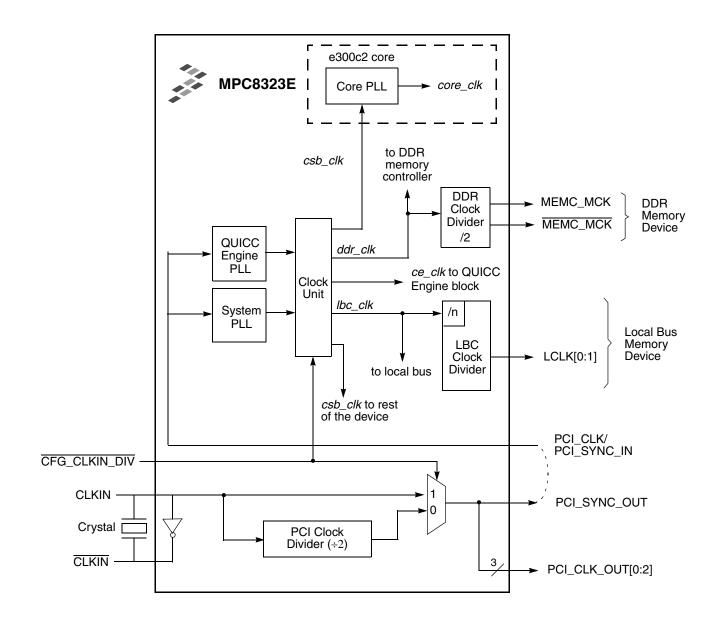

Figure 2 shows the internal distribution of clocks within the MPC8323E. The primary clock source for the MPC8323E can be one of two inputs, CLKIN or PCI\_CLK, depending on whether the device is configured in PCI host, PCI agent, or PCI disabled mode.

Figure 2. MPC8323E Clock Subsystem

### 3.1 System Clock in PCI Host Mode

When the MPC8323E is configured as a PCI host device (RCWH[PCIHOST] = 1), CLKIN is its primary input clock. CLKIN feeds the PCI clock divider (÷2) and the PCI\_SYNC\_OUT and PCI\_CLK\_OUT multiplexers. PCI\_SYNC\_OUT is connected externally to PCI\_SYNC\_IN to allow the internal PCI

MPC8321E/MPC8323E PowerQUICC™ II Pro Design Checklist, Rev.5

controller clock to synchronize with the external PCI agent clocks. PCI\_SYNC\_OUT must be connected properly to PCI\_SYNC\_IN, with equal delay to all PCI agent devices in the system.

The individual PCI\_CLK\_OUT[0:2] can be disabled by clearing the OCCR[PCICOEn] bit. For example, if only one PCI clock is needed, then configure OCCR[0:2] = 3'b100.  $\overline{CFG}$ \_CLKIN\_DIV selects whether CLKIN or CLKIN  $\div$  2 is driven out on the PCI\_SYNC\_OUT and PCI\_CLK\_OUT[0:2] signals. If  $\overline{CFG}$ \_CLKIN\_DIV = 0, then the PCI interface runs at half the CLKIN speed.

### 3.2 System Clock in PCI Agent Mode

When the MPC8323E is configured as a PCI agent device, PCI\_CLK is the primary input clock. In agent mode, the CLKIN signal should be pulled down with a  $1-4.7 \text{ k}\Omega$  resistor. PCI\_CLK\_OUT*n* and PCI\_SYNC\_OUT are not used. In agent mode, the  $\overline{\text{CFG\_CLKIN\_DIV}}$  configuration input can be used to double the internal clock frequencies.

$$CSB \ clock = PCI \ CLK \times (1 + \sim \overline{CFG \ CLKIN \ DIV}) \times RCWH[SPMF]$$

This feature is useful if a fixed internal frequency is desired, regardless of whether the PCI clock runs at 33 or 66 MHz. PCI specifications requires the PCI clock frequency information to be provided by the M66EN signal. If CFG\_CLKIN\_DIV = M66EN and PCI\_CLK is 33 MHz, then CSB speed is doubled.

### 3.3 System Clock if PCI is Disabled

If the PCI interface is not used, PCI\_CLK is the primary input clock. CLKIN should be tied to GND, and CFG\_CLKIN\_DIV should be tied high. Table 4 summarizes the clock signal pins.

| Signal                  | Pin  | Connection                                          |                                                                 | Notes                                                                                                                                                                                                                                                                                                                                            |

|-------------------------|------|-----------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal                  | Туре | If Used                                             | If Not Used                                                     | NOICS                                                                                                                                                                                                                                                                                                                                            |

| PCI_CLK_OUT[0:2]        | 0    | As needed <sup>1</sup>                              | Open                                                            | Device as PCI Host: Functions as PCI output clock banks. Program the Output Clock Control Register (OCCR) to enable only the output clocks needed and disable unused clocks in order to reduce EMI.      Device as PCI Agent or PCI Disabled: These signals are not used.                                                                        |

| PCI_SYNC_IN/<br>PCI_CLK | I    | Connect to<br>PCI_SYNC_OUT<br>or<br>25–66 MHz clock | Not applicable. This pin should always be connected, see Notes. | Device as PCI Host (PCI_CLK_OUTx signals driven): Functions as PCI_SYNC_IN. Connect externally to PCI_SYNC_OUT     Device as PCI Host (PCI_CLK_OUTx signals not driven), PCI Agent, or PCI Disabled:     Functions as PCI_CLK (primary input clock to the device). A valid 25-66MHz clock signal (at OVDD level) must be applied to this signal. |

**Table 4. Clock Signal Pin Listing**

#### Clocking

Table 4. Clock Signal Pin Listing (continued)

| Signal       | Signal Pin<br>Type | Connection                           |                       | Notes                                                                                                                                                                                                                                                                                                             |

|--------------|--------------------|--------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal       |                    | If Used                              | If Not Used           | NOIGS                                                                                                                                                                                                                                                                                                             |

| PCI_SYNC_OUT | 0                  | Connect to PCI_SYNC_IN               | Open                  | Device as PCI Host (PCI_CLK_OUTx signals driven): Connect externally to PCI_SYNC_IN signal for de-skewing of external PCI clock routing. Loop trace should match with PCI_CLK_OUTx signal traces.      Device as PCI Host (PCI_CLK_OUTx signals not driven), PCI Agent, or PCI Disabled: This signal is not used. |

| CLKIN        | I                  | Connect to 25–66<br>MHz clock signal | 1 k-4.7 k Ω to<br>GND | <ul> <li>Device as PCI Host: Functions as primary input clock. A valid 25-66 MHz clock signal (at OV<sub>DD</sub> level) must be applied to this signal.</li> <li>Device as PCI Host (PCI_CLK_OUTx signals not driven), Device as PCI Agent or PCI Disabled: This signal is not used.</li> </ul>                  |

#### Note:

<sup>1. &</sup>quot;As needed" terminology is used throughout this document to indicate that the pin should be connected to other devices on the board as required for the application.

# 4 Power-On Reset and Reset Configurations

A detailed power-on reset flow is described in the "Reset, Clocking, and Initialization" chapter of the MPC8323E PowerQUICC<sup>TM</sup> II Pro Integrated Communications Processor Family Reference Manual.

### 4.1 Reset Configuration Signals

Various device functions of the MPC8323E are initialized by sampling certain signals during the assertion of the PORESET signal after a stable clock is supplied. These inputs are either pulled high or low during this period. While these pins are generally output pins during normal operation, they are treated as inputs while PORESET is asserted. See Table 5 for termination recommendations for the reset configuration pins.

**Signal** Pin Type **Termination** PORESET ı Driven actively by the external reset logic **HRESET** I/O Pullup with 1  $k\Omega$  to  $OV_{DD}$ **SRESET** I/O Pullup with 2 - 10 k $\Omega$  to OV<sub>DD</sub> I/O Pull-up with  $4.7k\Omega$  to  $OV_{DD}$  or pulldown with  $1k\Omega$  to GND as desired, see Table 6 LGPL0/ CFG\_RESET\_SOURCE[0] Driven by FPGA as needed during HRESET assertion and tri-state after LGPL1/ I/O HRESET negation CFG\_RESET\_SOURCE[1] LGPL3/ I/O CFG\_RESET\_SOURCE[2] CFG CLKIN DIV I Pull-up with 4.7 k $\Omega$  to OV<sub>DD</sub> or pull down with 1k $\Omega$  to GND as desired Note: For more information, see Table 7.

**Table 5. Reset Configuration Pin Listing**

The CFG\_RESET\_SOURCE[0:2] input signals are sampled during the assertion of PORESET to specify the interface from which the device is to load the reset configurations words. The words can be loaded from the I<sup>2</sup>C interface, from a device on the local bus (CPLD, EEPROM, or FLASH), or from an internally defined word value. Table 6 describes the RCW options. For details, see the *MPC8323E PowerQUICC*<sup>TM</sup> *II Pro Integrated Communications Processor Family Reference Manual* (MPC8323ERM).

| CFG_RESET_SOURCE[0:2] Value (Binary) | Description                                                                                                               |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| 000                                  | Reset configuration words are loaded from a device on the local bus                                                       |

| 001                                  | Reserved configuration, should not be used.                                                                               |

| 010                                  | Reset configuration word is loaded from a device on I <sup>2</sup> C. PCI_CLK/PCI_SYNC_IN is in the range of 24-66.67MHz. |

| 011 - 111                            | Hard coded options 0-4.                                                                                                   |

**Table 6. Reset Configuration Word Source**

#### **Power-On Reset and Reset Configurations**

The CFG\_CLKIN\_DIV input signal is also sampled during the assertion of PORESET to determine the relationship between CLKIN and PCI\_SYNC\_IN. See Table 7. Notice that the configuration pins are multiplexed with the local bus GPLx signals.

Table 7. CLKIN Divisor Recommendations

| CFG_CLKIN_DIV Value (Binary) | Description                                                                                                                                                                                             |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                            | In PCI host mode:  • PCI runs at CLKIN speed  • csb_clk = CLKIN × SPMF In PCI agent or PCI Disabled mode:  • csb_clk = PCI_CLK × SPMF                                                                   |

| 0                            | In PCI host mode:  PCI interface runs at half of CLKIN speed PCI_CLK_OUT = CLKIN/2  csb_clk = (PCI_SYNC_IN × 2 × SPMF) = CLKIN × SPMF In PCI agent or PCI Disabled mode: csb_clk = (PCI_CLK × 2 × SPMF) |

### 4.2 Reset Configuration Words

The reset configuration words control the clock ratios and other basic device functions such as PCI host or agent mode, boot location, and endian mode. The reset configuration words are loaded from the local bus or the  $I^2C$  interface during the power-on or hard reset flows. If the reset configuration word is from the flash memory, it should reside at the beginning of the flash memory. That is should start from address 0. A total of two 32-bit-words are read. The first byte is read from address 0x0, the second byte from address 0x8, the third byte from address 0x10, and so on until all 8 bytes are read. Bytes b0-b3 form a word, and this is the reset configuration word low register (RCWLR). Bytes b4-b7 form the reset configuration word high register (RCWHR) as follows:

#### RCWLR

#### RCWHR

0x0020: b4xxxxx xxxxxxxx 0x0028: b5xxxxx xxxxxxx 0x0030: b6xxxxx xxxxxxx 0x0038: b7xxxxxx xxxxxxx

If the reset configuration word is from an I<sup>2</sup>C device, the I<sup>2</sup>C setup must comply with the following requirements:

- I<sup>2</sup>C EEPROM must be connected to I<sup>2</sup>C.

- EEPROM of extended address type must be used.

- EEPROM must respond to the calling address 0x101\_0000.

MPC8321E/MPC8323E PowerQUICC™ II Pro Design Checklist, Rev.5

• Use the special data format as described in the reference manual.

# 4.2.1 Blank Flash Memory or I<sup>2</sup>C EEPROM

After power-on reset, the MPC8323E first loads the hard reset configuration word from either the local bus or I<sup>2</sup>C device depending on the value of the CFG\_RESET\_SOURCE[0:2] pins.

### 4.2.1.1 Blank Flash Memory

If the HRCW is in the local bus flash memory, and the flash memory is blank, the MPC8323E loads an invalid HRCW and the PLL cannot lock. When connecting to the processor using an emulator, it will not be possible to communicate with the device through the JTAG port. To overcome this problem, many third-party tools implement a procedure to override the HRCW through JTAG. Contact your tool vendor for further information. To override the HRCW through JTAG with CodeWarrior™, use a JTAG configuration file to change the board reset configuration settings, regardless of the current switches or the values in flash memory. The JTAG configuration file should contain the desired values for the RCWLR and RCWHR registers and specify them in the CCS remote connection settings (Debug Version Settings → Remote Debugging). You can also use the following example file:

<CW8.7\_Folder>\PowerPC\_EABI\_Support\Initialization\_Files\jtag\_chains\832x\_HRCW\_jtag.txt

This file has one line:

```

E300 (1 1) (2 0x62040083) (3 0x84600000)

```

The meanings of the parameters inside the JTAG configuration file are:

- Config template index 1: Boolean value that turns the overriding on and off

- Config template index 2: Value for Reset Configuration Word Low in the format of RCWLR

- Config template index 3: Value for Reset Configuration Word High in the format of RCWHR

#### NOTE

If index 1 is set, the next time the reset\_to\_user or reset\_to\_debug commands are issued, the core should come up with the HRCW overridden. It is not enough to clear index 1 to turn this feature off; a power-on reset should be issued.

### 4.2.1.2 Blank I<sup>2</sup>C EEPROM

If you are loading the HRCW from the  $I^2C$  bus, the override procedure described in the previous section will not work. To avoid this situation, be sure to have an alternate means of programming the EEPROM on the  $I^2C$  bus or implement an option on the board to use the default built-in HRCW options at power-on reset. The three possible workarounds are:

- Temporarily tie the SDA to the SCL pin rendering the I<sup>2</sup>C bus non-functional.

- Pull up the reset configuration pins to set the HRCW to load from a different interface such as the local bus, and then override the HRCW word.

- Pull up the reset configuration pins to use one of the default preloaded HRCW so the JTAG tool can gain control. Then program the I<sup>2</sup>C EEPROM with the appropriate HRCW. This is particularly

MPC8321E/MPC8323E PowerQUICC™ II Pro Design Checklist, Rev.5

#### **Power-On Reset and Reset Configurations**

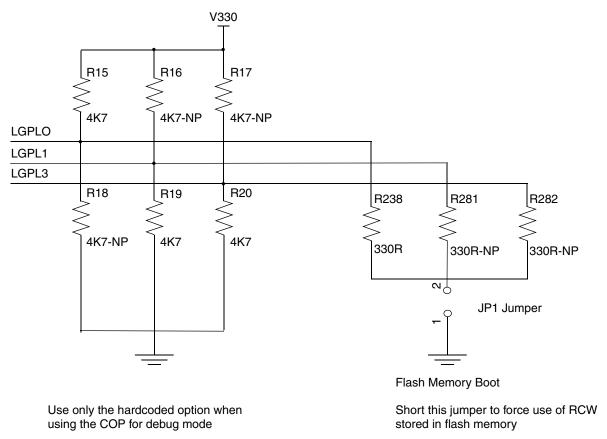

useful when the local bus flash memory is programmed for the first time or when reflashing is needed after the flash memory is accidentally erased. Figure 3 shows an example that fetches the HRCW either from the local bus (CFG\_RESET\_SOURCE[0:2] = 0b000) or chooses a hardcoded HRCW (CFG\_RESET\_SOURCE[0:2] = 0b100) through a jumper setting.

Figure 3. Enabling Hardcoded HRCW Option Via Jumper on CFG RESET SOURCE[0:2]

### 4.3 Boot sequencer

The boot sequencer is for loading the hardware reset configuration word and configuring any memory-mapped register before the boot-up code runs. Reset configuration load mode is selected based on the settings of the CFG\_RESET\_SOURCE[0:2] pins during the power-on reset sequence. The I<sup>2</sup>C interface loads the reset configuration words from an EEPROM at a specific calling address while the rest of the device is in the reset state. After the reset configuration words are latched inside the device, I<sup>2</sup>C is reset until HRESET is negated. Then the device can be initialized using boot sequencer mode.

Boot sequencer mode is selected at power-on reset by the RCWHR[BOOTSEQ] field. The I<sup>2</sup>C module communicates with one or more EEPROMs through the I<sup>2</sup>C interface to initialize one or more configuration registers of the PowerQUICC II Pro. For example, this code can be used to configure the port interface registers if the device is booting from PCI. Refer to the reference manual for the complete data format for programming the I<sup>2</sup>C EEPROM. The boot sequencer contains a basic level of error detection. If the I<sup>2</sup>C boot sequencer fails while loading the reset configuration words, the RSR[BSF] bit is set. If a

preamble or CRC fail is detected in boot sequencer mode, there is no internal or external indication that the boot sequencer operation has completed unsuccessfully.

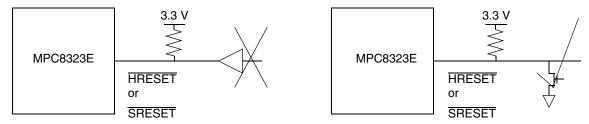

#### **HRESET** and **SRESET** 4.4

The HRESET and SRESET signals are not pure input signals. They are open-drain signals that the MPC8323E processor can drive low. The connection on the left side of Figure 4 causes signal contention and must not be used.

Figure 4. HRESET and SRESET Connection

#### 4.5 **Useful System POR Debug Registers**

The hardware reset configuration settings can be read in the RCWLR, the RCWHR, the reset status register (RSR), and the system PLL mode register (SPMR). See the reference manual for details on these registers. Note that all of these resisters are read-only registers.

#### 5 JTAG and Debug

Boundary-scan testing is enabled through the JTAG interface signals. The TRST signal is optional in the IEEE Std 1149.1<sup>TM</sup> specification, but it is provided on all processors that implement the Power Architecture<sup>TM</sup>. The device requires  $\overline{TRST}$  to be asserted during power-on reset flow to ensure that the JTAG boundary logic does not interfere with normal chip operation. While the TAP controller can be forced to the reset state using only the TCK and TMS signals, generally systems assert TRST during the power-on reset flow. Simply tying TRST to PORESET is not practical because the JTAG interface is also used for accessing the common on-chip processor (COP), which implements the debug interface to the chip.

The COP function of these processors allow a remote computer system (typically, a PC with dedicated hardware and debugging software) to access and control the internal operations of the processor. The COP interface connects primarily through the JTAG port of the processor, with some additional status monitoring signals. The COP port requires the ability to assert PORESET or TRST independently to control the processor fully. If the target system has independent reset sources, such as voltage monitors, watchdog timers, power supply failures, or push-button switches, the COP reset signals must be merged into these signals with logic.

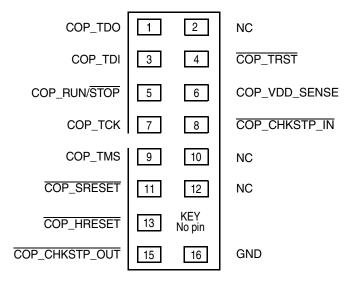

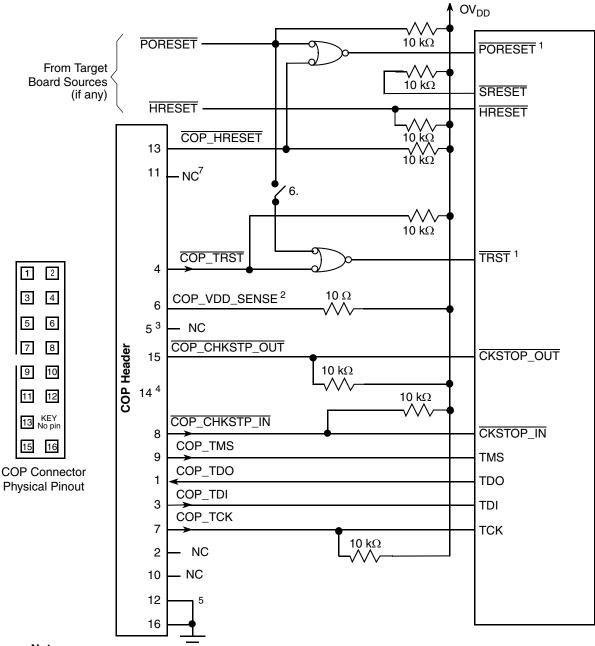

In the arrangement shown in Figure 5, the COP port can assert PORESET or TRST independently while ensuring that the target can drive PORESET as well. The COP interface has a standard header, shown in Figure 5, for connecting to the target system and is based on the 0.025" square-post, 0.100" centered

MPC8321E/MPC8323E PowerQUICC™ II Pro Design Checklist, Rev.5 Freescale Semiconductor 15

#### JTAG and Debug

header assembly (often called a Berg header). The connector typically has pin 14 removed as a connector key.

The COP header adds many benefits such as breakpoints, watchpoints, register and memory examination/modification, and other standard debugger features. An inexpensive option can be to leave the COP header unpopulated until needed. There is no standardized way to number the COP header; so emulator vendors have issued many different pin numbering schemes. Some COP headers are numbered top-to-bottom then left-to-right, while others use left-to-right then top-to-bottom. Still others number the pins counter- clockwise from pin 1 (as with an IC). Regardless of the numbering scheme, the signal placement recommended in Figure 5 is common to all known emulators.

If the JTAG interface and COP header are not used, Freescale recommends all of the following connections:

- TRST should be tied to PORESET through a 0 kΩ isolation resistor so that it is asserted when the system reset signal (PORESET) is asserted, ensuring that the JTAG scan chain is initialized during the power-on reset flow. Freescale recommends that the COP header be designed into the system as shown in Figure 6. If this is not possible, the isolation resistor allows future access to TRST in case a JTAG interface may need to be wired onto the system in future debug situations.

- Tie TCK to  $OV_{DD}$  through a 10 k $\Omega$  resistor to prevent TCK from changing state and reading incorrect data into the device.

- No connection is required for TDI, TMS, or TDO.

Figure 5. COP Connector Physical Pinout

#### Notes:

- 1. The COP port and target board should be able to assert PORESET and TRST independently to the processor to control the processor fully as shown here.

- 2. Populate this with a 10  $\Omega$  resistor for short-circuit/current-limiting protection.

- 3. COP\_RUN/STOP, normally found on pin 5 of the COP header, is not implemented on the device. Connect pin 5 of the COP header to  $OV_{DD}$  with a 10 k $\Omega$  pull-up resistor.

- 4. The KEY location (pin 14) is not physically present on the COP header.

- 5. Although pin 12 is defined as a No-Connect, some debug tools may use pin 12 as an additional GND pin for improved signal integrity.

- 6. This switch is included as a precaution for BSDL testing. The switch should be open during BSDL testing to avoid accidentally asserting the /TRST line. If BSDL testing is not being performed, this switch should be closed or removed.

- 7. See erratum RESET3 in MPC832xECE.

Figure 6. JTAG Interface Connection

MPC8321E/MPC8323E PowerQUICC™ II Pro Design Checklist, Rev.5

Table 8 details the termination recommendations for the JTAG, TEST, PMC, and thermal management pins.

Table 8. JTAG and TEST Pin Listing

|           | Pin                 | Connection                                                          |                                   |                                                                                                                                                                                                                                                                                             |  |

|-----------|---------------------|---------------------------------------------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Signal    | Signal Type if used |                                                                     | if not used                       | - Notes                                                                                                                                                                                                                                                                                     |  |

| TCK       | I                   | As needed + 10 k $\Omega$ to OV <sub>DD</sub>                       | 10 k $\Omega$ to OV <sub>DD</sub> | Commonly used for boundary scan testing. If this pin is truly not used, it can be tied directly to GND.                                                                                                                                                                                     |  |

| TDI       | I                   | As needed                                                           | Open                              | This JTAG pin has a weak internal pull-up P-FET that is always enabled.                                                                                                                                                                                                                     |  |

| TDO       | 0                   | As needed                                                           | Open                              | Actively driven during RESET                                                                                                                                                                                                                                                                |  |

| TMS       | I                   | As needed                                                           | Open                              | This JTAG pin has a weak internal pull-up P-FET that is always enabled.                                                                                                                                                                                                                     |  |

| TRST      | I                   | Tie to the output of a Negative OR gate + 10 kΩ to OV <sub>DD</sub> | Tie to PORESET through a 0 kΩ     | This JTAG pin has a weak internal pull-up P-FET that is always enabled.  If an In-Circuit Emulator is used in the design, TRST should be tied to the output of a Negative OR gate logic. The inputs to the Negative OR gate logic should be any external TRST source and the PORESET signal |  |

|           |                     |                                                                     | Test                              |                                                                                                                                                                                                                                                                                             |  |

| TEST_MODE | I                   | Tie direct                                                          | ly to GND                         | _                                                                                                                                                                                                                                                                                           |  |

|           |                     |                                                                     | PMC                               |                                                                                                                                                                                                                                                                                             |  |

| QUIESCE   | 0                   | As needed                                                           | Open                              | _                                                                                                                                                                                                                                                                                           |  |

|           |                     |                                                                     | Thermal Manag                     | gement                                                                                                                                                                                                                                                                                      |  |

| THERM0    | I                   | As needed                                                           | Tie to GND                        | Thermal sensitive resistor                                                                                                                                                                                                                                                                  |  |

| THERM1    | _                   | As needed                                                           | Tie to GND                        | Thermal sensitive resistor                                                                                                                                                                                                                                                                  |  |

# 6 Functional Blocks

This section discusses the recommendations and guidelines for designing with the various functional blocks on the PowerQUICC II Pro processors.

### 6.1 Local Bus Controller

The local bus runs at up to 66 MHz, The local bus supports four chip selects:  $\overline{LCS}[0:3]$ . LGPL4 must be pulled high to  $OV_{DD}$  with a  $1K-\Omega$  resistor. In the normal case, when MPC8323E boots from the flash memory on the local bus, the local bus uses the GPCM machine. Under GPCM, the LGPL4 functions as  $\overline{LGTA}$ , which is an input. Therefore, it must be pulled high. If it is floating and drifts to low, it terminates GPCM access prematurely. The pull-up also avoids the issue described in the local bus signal description table in the reference manual.

MPC8321E/MPC8323E PowerQUICC™ II Pro Design Checklist, Rev.5

The local bus frequency can be adjusted through the LCRR[CLKDIV] register field. After reset, the MPC8323E defaults to a 8:1 ratio. However the MPC8323E only supports Local bus frequencies of 33 and 66 MHz (these are the only frequencies that are currently tested). Therefore, the user must adjust the value of the LCRR[CLKDIV] in order to meet the local bus supported frequencies. Software should not reconfigure the local bus clock while code is executing from the local bus, but rather while code is executing from another interface, such as the DDR controller.

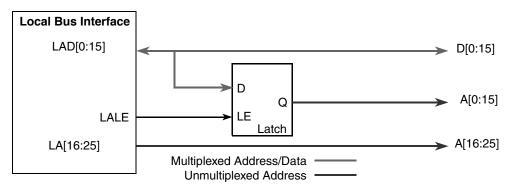

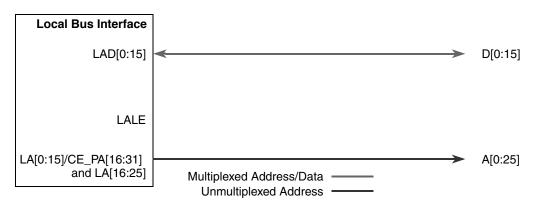

#### 6.1.1 **Local Bus Address Signals**

To save signals on the local bus, address and data are multiplexed onto the same 16-bit bus. An external latch is needed to demultiplex the 16-bit MSB address and, together with LA[16:25], to reconstruct the original address. No external intelligence is needed, because LALE provides the correct timing to control a standard logic latch. The LAD signals can be directly connected to the data signals of the memory/peripheral. Transactions on the local bus start with an address phase, where the LBC drives the transaction address on the LAD signals and asserts the LALE signal. This can be used to latch the address and then the LBC can continue with the data phase. Figure 7 and Figure 9 illustrate the connection of the local bus in both multiplexed and non-multiplexed address modes defined by the state of the CFG\_LBIU\_MUX\_EN signal. For details on the operation of the local bus controller, refer to the reference manual.

Figure 7. Local Bus Address Connection Example (Multiplexed Mode)

Figure 8. Unmultiplexed Address and Data Bus Connection Example

MPC8321E/MPC8323E PowerQUICC™ II Pro Design Checklist, Rev.5 Freescale Semiconductor 19

### 6.1.2 Connecting Devices to the Local Bus

The MPC8323E local bus features a multiplexed address and data bus, LAD[0:15]. An external latch is required to de-multiplex these signals to the connecting device. Figure 9 shows the timing of LALE. When LALE is high, it indicates LAD[0:15] is in the address phase.

Figure 9. LALE Timing

For every assertion of  $\overline{LCS}$ n, LALE is asserted first. While LALE is asserted, all other control signals are negated. The duration of LALE can be programmed to 1–4 cycles in LCRR[EADC]. The default is 4 cycles. The timing of LALE negation is important to ensure the correct latch. If the change of LAD and negation of LALE are too close and the margin for the latch is not sufficient, RCWHR[LALE] can be set. LALE is negated ½ a local bus clock earlier, which should ensure enough margin. Table 9 shows the termination recommendations for the local bus pins.

Connection Note Critical Signal Pin Type s If Used If Not Used **Local Bus Interface** 2 k-10 k $\Omega$  to OV<sub>DD</sub> LAD[0:15] I/O As needed LA[0:25] 0 As needed Open LCS[0:3] As needed 0 Open <u>LWE</u>[0:1]/<u>LBS</u>[0:1] 0 As needed Open **LBCTL** 0 As needed Open LALE 0 As needed Open Χ LGPL0/ CFG RESET SOURCE0 I/O As needed See Table 6 Х LGPL1/ CFG\_RESET\_SOURCE1 I/O As needed See Table 6 LGPL2/LOE 0 As needed Open Χ LGPL3/ CFG RESET\_SOURCE2 I/O As needed See Table 6

Table 9. Local Bus Pin Listing

MPC8321E/MPC8323E PowerQUICC™ II Pro Design Checklist, Rev.5

| Table 9. | Local | Bus | Pin | Listing | (continued) |

|----------|-------|-----|-----|---------|-------------|

|----------|-------|-----|-----|---------|-------------|

| Critical | Signal             | Pin Type   | Connection                                               | on          | Note |

|----------|--------------------|------------|----------------------------------------------------------|-------------|------|

| Ontious  | Oiginal .          | l III Type | If Used                                                  | If Not Used | s    |

| _        | LGPL4/LGTA/LUPWAIT | I/O        | As needed + 1 k–10 k $\Omega$ to $\text{OV}_{\text{DD}}$ | Open        | _    |

| Х        | LGPL5              | 0          | As needed                                                | Open        | _    |

| _        | LCLK[0:1]          | 0          | As needed                                                | Open        | _    |

### 6.2 DDR SDRAM

Refer to the following application notes for details on layout considerations and DDR programming guidelines:

- For signal integrity and layout considerations: *Hardware and Layout Design Considerations for DDR Memory Interfaces* (AN2582).

- Programming the PowerQUICC III DDR SDRAM Controller (AN2583).

- For signal integrity and layout considerations: *Hardware and Layout Design Considerations for DDR2 SDRAM Memory Interfaces* (AN2910).

The MPC8323E DDR controller supports both DDR1 and DDR2 SDRAM selectable via the DDRCDR register (please see the Reference Manual for details). The MPC8323E DDR controller can be configured with a 32-bit data bus interface only. Software must set the DDR\_SDRAM\_CFG[32\_BE] field. Also, the burst length should be set to 8 beats in 32-bit mode by properly configuring the DDR\_SDRAM\_CFG[8\_BE]. Refer to the MPC8323E reference manual. Table 10 lists the termination

DDR\_SDRAM\_CFG[8\_BE]. Refer to the MPC8323E reference manual. Table 10 lists the termination recommendations for the different DDR signals for both controllers.

**Table 10. DDR SDRAM Pin Listing**

| Critical | Connection tical Signal Pin Type |         | ction     | Notes       |                                                                                                                                                                                                                                                                                                 |

|----------|----------------------------------|---------|-----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Citical  | Sigilal                          | гш туре | If Used   | If Not Used | Notes                                                                                                                                                                                                                                                                                           |

| _        | MDQ[0:31]                        | I/O     | As needed | Open        | Proper signal integrity analysis must be performed using the respective device IBIS model.  Parallel termination is optional for DDR signals and should be simulated to verify necessity.  Differential termination is included on DIMMs. It is only required for discrete memory applications. |

| _        | MDM[0:3]                         | 0       | As needed | Open        | _                                                                                                                                                                                                                                                                                               |

| _        | MDQS[0:3]                        | I/O     | As needed | Open        | _                                                                                                                                                                                                                                                                                               |

| _        | MBA[0:2]                         | 0       | As needed | Open        | _                                                                                                                                                                                                                                                                                               |

| _        | MA[0:13]                         | 0       | As needed | Open        | _                                                                                                                                                                                                                                                                                               |

| _        | MWE                              | 0       | As needed | Open        | _                                                                                                                                                                                                                                                                                               |

#### Table 10. DDR SDRAM Pin Listing (continued)

| Critical | Critical Signal |          | Connection |             | Notes                                                                                    |

|----------|-----------------|----------|------------|-------------|------------------------------------------------------------------------------------------|

| Cittical | Signal          | Pin Type | If Used    | If Not Used | Notes                                                                                    |

| _        | MRAS            | 0        | As needed  | Open        | _                                                                                        |

| _        | MCAS            | 0        | As needed  | Open        | _                                                                                        |

| _        | MCS             | 0        | As needed  | Open        | _                                                                                        |

| _        | MCKE            | 0        | As needed  | Open        | This output is actively driven during reset rather than being three-stated during reset. |

| _        | MCK             | 0        | As needed  | Open        | _                                                                                        |

| _        | MCK             | 0        | As needed  | Open        | _                                                                                        |

| _        | MODT            | 0        | As needed  | Open        | _                                                                                        |

### 6.3 PCI Bus Interface

If PCI is used, program  $\overline{INTA/IRQ\_OUT}$  to open drain and pull it up with a 10-k $\Omega$  resistor.

The RCWHR controls the hardware configuration of the PCI blocks as follows:

- RCWH[PCIHOST]. Host/Agent mode for PCI.

- RCWH[PCIARB]. PCI internal/external arbiter mode select.

When the device is configured as a PCI host, the device provides three clock output signals for external PCI agents, PCI\_CLK\_OUT[0:2]. Each clock output can be enabled (enable toggling of the clock) by setting its corresponding OCCR[PCICOEn] bit. It is recommended to turn off the unused clock outputs by writing to OCCR[PCICOEn] in order to reduce EMI.

The MPC8323E PCI interface is hot swap friendly, meaning that it supports the hardware and software connection processes as defined in the Hot Swap specification. This level of support allows the board and system designers to build full hot swap systems based on the MPC8323E as a PCI target device. It is assumed that the system uses the external arbiter from the PCI host. Therefore, the extra pins needed for the CompactPCI Hot Swap are multiplexed with the PCI arbitration signals. When an external arbiter is selected (RCWH[PCIARB] = 0), the CompactPCI Hot Swap pins function. When an internal arbiter is selected (RCWH[PCIARB] = 1), the GNTx/REQx pins function.

Refer to the MPC8323E reference manual for details on the usage of the RCWH settings.

Table 11 lists the PCI bus interface pins.

**Table 11. PCI Bus Interface Pin Listing**

|          | Tuble 11.1 of bus interface 111 Listing |                     |                                                                        |                                                |                                                                                                                                                                                                                                                         |  |

|----------|-----------------------------------------|---------------------|------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Critical | Signal                                  | Pin Type Connection |                                                                        | ection                                         | - Notes                                                                                                                                                                                                                                                 |  |

|          |                                         |                     | If Used                                                                | If Not Used                                    |                                                                                                                                                                                                                                                         |  |

|          |                                         |                     | PC                                                                     | CI Interface                                   |                                                                                                                                                                                                                                                         |  |

| _        | PCI_INTA/IRQ_OUT                        | 0                   | 2 k–10 kΩ to<br>OV <sub>DD</sub>                                       | 2 k–10 kΩ to<br>OV <sub>DD</sub>               | Open-drain signal. In agent mode, INTA typically connects to a central interrupt controller. In host mode, INTA can be used to assert interrupts to other devices, such as a second processor.                                                          |  |

| _        | PCI_RESET_OUT                           | 0                   | As needed                                                              | Open                                           | This signal is used only in host mode. It should be left unconnected in agent mode.                                                                                                                                                                     |  |

|          | PCI_AD[31:0]                            | I/O                 | As needed                                                              | 2 k–10 kΩ to<br>OV <sub>DD</sub><br>or<br>Open | If the PCI port is not used and the bus is parked, no termination is needed. Software must park the bus as follows:  1. RCWHR[PCIHOST] = 1 2. RCWHR[PCIARB] = 1 3a. PCI Arbiter Control Configuration Register PM bit = 1, or 3b. PCI_GCR[BBR] = 1      |  |

|          | PCI_C/BE[3:0]                           | I/O                 | As needed                                                              | 2 k–10 kΩ to<br>OV <sub>DD</sub><br>or<br>Open | If the PCI port is not used and the bus is parked, no termination is needed. Software needs to park the bus as follows:  1. RCWHR[PCIHOST] = 1 2. RCWHR[PCI1ARB] = 1 3a. PCI Arbiter Control Configuration Register PM bit = 1, or 3b. PCI_GCR[BBR] = 1 |  |

| _        | PCI_PAR                                 | I/O                 | As needed                                                              | 2 k–10 kΩ to<br>OV <sub>DD</sub>               | If the PCI port is not used, this signal must be pulled up.                                                                                                                                                                                             |  |

| _        | PCI_FRAME                               | I/O                 | As needed + $2 \text{ k}10 \text{ k}\Omega$ to $\text{OV}_{\text{DD}}$ | 2 k–10 kΩ to<br>OV <sub>DD</sub>               | PCI specification requires a weak pullup.                                                                                                                                                                                                               |  |

| _        | PCI_TRDY                                | I/O                 | As needed + $2 \text{ k}10 \text{ k}\Omega$ to $\text{OV}_{\text{DD}}$ | 2 k–10 kΩ to<br>OV <sub>DD</sub>               | PCI specification requires a weak pullup.                                                                                                                                                                                                               |  |

| _        | PCI_IRDY                                | I/O                 | As needed + $2 \text{ k}10 \text{ k}\Omega$ to $\text{OV}_{\text{DD}}$ | 2 k–10 kΩ to<br>OV <sub>DD</sub>               | PCI specification requires a weak pullup.                                                                                                                                                                                                               |  |

| _        | PCI_STOP                                | I/O                 | As needed + $2 \text{ k}10 \text{ k}\Omega$ to $\text{OV}_{\text{DD}}$ | 2 k–10 kΩ to<br>OV <sub>DD</sub>               | PCI specification requires a weak pullup.                                                                                                                                                                                                               |  |

| _        | PCI_DEVSEL                              | I/O                 | As needed + 2 k–10 kΩ to OV <sub>DD</sub>                              | 2 k–10 kΩ to<br>OV <sub>DD</sub>               | PCI specification requires a weak pullup.                                                                                                                                                                                                               |  |

Table 11. PCI Bus Interface Pin Listing (continued)

| Critical | Cianal                  | Pin  | Conn                                                                                                     | ection                                                                                                 | Notes                                                                                                                                                                                                                                         |

|----------|-------------------------|------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Critical | Signal                  | Туре | If Used                                                                                                  | If Not Used                                                                                            | Notes                                                                                                                                                                                                                                         |

| _        | PCI_IDSEL               | I    | PCI host: Tie to GND PCI agent: One of PCI_AD[31:0]                                                      | Tie to GND                                                                                             | IDSEL should be connected to GND for host systems and to one address line for agent systems. If the PCI port is not used, it should be grounded.  • PCI host is selected by RCWH[PCIHOST] = 1.  • PCI agent is selected by RCWH[PCIHOST] = 0. |

| _        | PCI_SERR                | I/O  | As needed + $2 \text{ k}10 \text{ k}\Omega$ to $\text{OV}_{\text{DD}}$                                   | 2 k–10 kΩ to<br>OV <sub>DD</sub>                                                                       | PCI specification requires a weak pullup.                                                                                                                                                                                                     |

| _        | PCI_PERR                | I/O  | As needed + $2 \text{ k}10 \text{ k}\Omega$ to $\text{OV}_{\text{DD}}$                                   | 2 k–10 kΩ to<br>OV <sub>DD</sub>                                                                       | PCI specification requires a weak pullup.                                                                                                                                                                                                     |

|          | PCI_REQ0                | I/O  | External arbiter: As needed Internal arbiter: As needed + $2 \text{ k-} 10 \text{ k}\Omega$ to $OV_{DD}$ | External arbiter: Open Internal arbiter: $2 \text{ k-} 10 \text{ k}\Omega \text{ to}$ OV <sub>DD</sub> | If an external arbiter is used, REQ0 becomes an output signal and does not need to be terminated.  • External arbiter selected by RCWH[PCIARB] = 0.  • Internal arbiter selected by RCWH[PCIARB] = 1.                                         |

| _        | PCI_REQ1/<br>CPCI_HS_ES | I    | External arbiter: As needed  Internal arbiter: As needed + 2 k–10 kΩ to OV <sub>DD</sub>                 | 2 k–10 kΩ to<br>OV <sub>DD</sub>                                                                       | This pin is multiplexed with a CompactPCI Hot Swap function. CompactPCI functionality selected when external arbiter is used.  • External arbiter selected by RCWH[PCIARB] = 0.  • Internal arbiter selected by RCWH[PCIARB] = 1.             |

| _        | PCI_REQ2                | I    | As needed + $2 \text{ k}10 \text{ k}\Omega$ to $\text{OV}_{\text{DD}}$                                   | 2 k–10 kΩ to<br>OV <sub>DD</sub>                                                                       | _                                                                                                                                                                                                                                             |

| _        | PCI_GNT0                | I/O  | External arbiter: As needed + 2 k-10 kΩ to OV <sub>DD</sub> Internal arbiter: As needed                  | External arbiter: 2 k-10 kΩ to OV <sub>DD</sub> Internal arbiter: Open                                 | If an external arbiter is used, GNT0 becomes an input signal and should be pulled up with 2 k–10 kΩ to OV <sub>DD</sub> .  • External arbiter selected by RCWH[PCIARB] = 0.  • Internal arbiter selected by RCWH[PCIARB] = 1.                 |

### MPC8321E/MPC8323E PowerQUICC™ II Pro Design Checklist, Rev.5

| Critical | Signal                    | Pin  | Connection<br>Pin                                                                       |                                                                              | Notes                                                                                                                                                                                                                                                                                                                                             |

|----------|---------------------------|------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Critical | Signal                    | Туре | If Used                                                                                 | If Not Used                                                                  | NUICS                                                                                                                                                                                                                                                                                                                                             |

| _        | PCI_GNT1/<br>CPCI_HS_LED  | 0    | As needed                                                                               | Open                                                                         | This pin is multiplexed with a CompactPCI Hot Swap function. CompactPCI functionality selected when external arbiter is used.  • External arbiter selected by RCWH[PCIARB] = 0.  • Internal arbiter selected by RCWH[PCIARB] = 1.                                                                                                                 |

| _        | PCI_GNT2/<br>CPCI_HS_ENUM | 0    | External arbiter: As needed + 2 k-10 kΩ to OV <sub>DD</sub> Internal arbiter: As needed | External arbiter: Open Internal arbiter: Open                                | This pin is multiplexed with a CompactPCI Hot Swap function. CompactPCI functionality selected when external arbiter is used.  • If CompactPCI Hot Swap function is used, a weak pullup is required (2 k–10 k $\Omega$ to OV <sub>DD</sub> ).  • External arbiter selected by RCWH[PCIARB] = 0.  • Internal arbiter selected by RCWH[PCIARB] = 1. |

| _        | M66EN                     | I    | As needed                                                                               | $5 \text{ k}\Omega \text{ to OV}_{DD}$ or $1 \text{ k}\Omega \text{ to GND}$ | No role if PCI is not used.                                                                                                                                                                                                                                                                                                                       |

# 6.4 Integrated Programmable Interrupt Controller (IPIC)

The integrated programmable interrupt controller (IPIC) provides interrupt management for receiving hardware-generated interrupts from different sources (both internal and external). It also prioritizes and delivers the interrupts to the CPU for servicing.  $\overline{MCP\_OUT}$  is an open-drain signals that must be pulled up with a 4.7-k $\Omega$  resistor.  $\overline{IRQ0/MCP\_IN}$  is an input when the e300 core is enabled. When the e300 core is disabled,  $\overline{IRQ0/MCP\_IN}$  is an output that must be connected to the host processor.  $\overline{IRQ}[6:7]$  are multiplexed with other functions and are controlled by the SICRL register. Unused  $\overline{IRQ}$  signals must be pulled up to  $OV_{DD}$ . The IIC\_SCL/ $\overline{CKSTOP\_IN}$  and  $\overline{IRQ}[7]/\overline{CKSTOP\_IN}]$  signals must be actively driven or pulled up to  $OV_{DD}$  if they are programmed as  $\overline{CKSTOP\_IN}$ .

Table 12 lists the PIC pins.

Table 12. Programmable Interrupt Controller Pin Listing

| Critical        | Signal  | Pin Tyne | Connection in Type                                           |                     | Notes             |

|-----------------|---------|----------|--------------------------------------------------------------|---------------------|-------------------|

| Gritical Signal | ТШТУРС  | If Used  | If Not Used                                                  | Notes               |                   |

| _               | MCP_OUT | 0        | As needed + $4.7 \text{ k}\Omega$ to $\text{OV}_{\text{DD}}$ | 4.7 kΩ to $OV_{DD}$ | Open-drain signal |

Table 12. Programmable Interrupt Controller Pin Listing (continued)

| Critical | Signal            | Pin Tyne | Connection Pin Type                                                     |                                             | Notes                                                        |

|----------|-------------------|----------|-------------------------------------------------------------------------|---------------------------------------------|--------------------------------------------------------------|

|          | O.g.i.a.          | , , ,    | If Used                                                                 | If Not Used                                 |                                                              |

| _        | ĪRQ[0]/MCP_IN     | I        | As needed + 2 k–10 kΩ to OV <sub>DD</sub>                               | 2 k–10 kΩ to<br>OV <sub>DD</sub>            | _                                                            |

| _        | ĪRQ[1:5]          | I        | As needed + $2 \text{ k}10 \text{ k}\Omega$ to $\text{OV}_{\text{DD}}$  | 2 k–10 kΩ to $OV_{DD}$                      | _                                                            |

| _        | IRQ[6]/CKSTOP_OUT | I/O      |                                                                         | CKSTOP_OUT<br>: Open                        | Pin functionality determined by SICRL[IRQ_CKS] bit settings. |

|          |                   |          | Others:<br>As needed +<br>2k-10 kΩ<br>to OV <sub>DD</sub>               | Others:<br>2 k–10 kΩ to<br>OV <sub>DD</sub> |                                                              |

|          | IRQ[7]/CKSTOP_IN  | I/O      | CKSTOP_IN: As needed + 10 kΩ to $OV_{DD}$                               | CKSTOP_IN: 4.7 kΩ to $OV_{DD}$              | Pin functionality determined by SICRL[IRQ_CKS] bit settings. |

|          |                   |          | Others: As needed + $2 \text{ k-10 k}\Omega$ to $\text{OV}_{\text{DD}}$ | Others:<br>2 k–10 kΩ to<br>OV <sub>DD</sub> |                                                              |

### 6.5 DUART

The MPC8323E DUART module provides two standard UART interfaces, and any UCC from the QUICC Engine block can be programmed to function as UART. Refer to Section 6.7.3, "QUICC Engine UART." The DUART pins are multiplexed with the DDR controller and local bus controller debug functions. The functions are programmed with SICRL[URT\_CTPR]. If only UARTn\_SOUT and UARTn\_SIN are used, UARTn\_CTS must be pulled down.

Table 13 lists the DUART pins.

**Table 13. Dual UART Pin Listing**

| Critical | Critical Signal                         |          | Connection |             | Notes                                                        |

|----------|-----------------------------------------|----------|------------|-------------|--------------------------------------------------------------|

|          | O.g.i.u.                                | Pin Type | If Used    | If Not Used |                                                              |

| _        | UART1_SOUT/<br>M1SRCID[0]/<br>LSRCID[0] | 0        | As needed  | Open        | Pin functionality determined by SICRL[URT_CTPR] bit setting. |

### Table 13. Dual UART Pin Listing (continued)

| Critical | Signal                                  | Pin Type | Conne     |                                                                                          | Notes                                                                                                             |

|----------|-----------------------------------------|----------|-----------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Ontical  | Jighai                                  | ТШТУРС   | If Used   | If Not Used                                                                              | Notes                                                                                                             |

| _        | UART1_SIN/<br>M1SRCID[1]/<br>LSRCID[1]  | I/O      | As needed | 2 k-10 kΩ to<br>GND or program<br>pin to function as<br>a debug pin                      | Pin functionality determined by SICRL[URT_CTPR] bit setting.                                                      |

|          | UART1_CTS/<br>M1SRCID[2]/<br>LSRCID[2]  | I/O      | As needed | $2 \text{ k}10 \text{ k}\Omega \text{ to}$ GND or program pin to function as a debug pin | Pin functionality determined by SICRL[URT_CTPR] bit setting If DUART1 is used, but CTS is not used, pull it down. |

| _        | UART1_RTS/<br>M1SRCID[3]/<br>LSRCID[3]  | 0        | As needed | Open                                                                                     | Pin functionality determined by SICRL[URT_CTPR] bit setting. If DUART1 is used but RTS is not used, leave open.   |

| _        | UART2_SOUT/<br>M1SRCID[4]/<br>LSRCID[4] | 0        | As needed | Open                                                                                     | Pin functionality determined by SICRL[URT_CTPR] bit setting.                                                      |

| _        | UART2_SIN/MDVAL/<br>LDVAL               | I/O      | As needed | $2 \text{ k}10 \text{ k}\Omega \text{ to}$ GND or program pin to function as a debug pin | Pin functionality determined by SICRL[URT_CTPR] bit setting.                                                      |

| _        | UART2_CTS                               | I        | As needed | 2 k–10 kΩ to<br>GND or program<br>pin to function as<br>a debug pin                      | If DUART2 is used, but CTS is not used, pull it down.                                                             |

| _        | UART2_RTS                               | 0        | As needed | Open                                                                                     | If DUART2 is used but RTS is not used, leave open.                                                                |

### 6.6 I<sup>2</sup>C Interface

Table 14 lists the I<sup>2</sup>C pins.

Table 14. I<sup>2</sup>C Pin Listing