# Bootable CPU RTC with Two I<sup>2</sup>C Buses, 128 Byte SRAM and Alarm Function

### PCF85053A

Last Updated: Apr 12, 2024

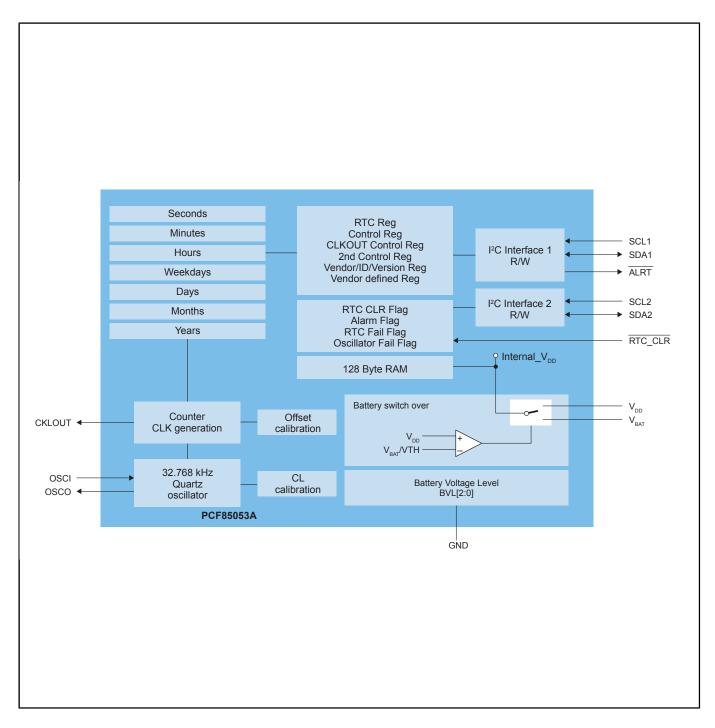

PCF85053A is a CMOS real-time clock (RTC) and calendar, optimized for low power consumption and automatic switching to battery on primary power loss. Featuring clock output, alert interrupt output and 128-byte battery backed-up SRAM, the PCF85053A includes two I<sup>2</sup>C buses. The primary I<sup>2</sup>C bus has the read / write capability on RTC and SRAM registers; the second I<sup>2</sup>C bus also can read / write most registers with the control bits set by primary I<sup>2</sup>C controller.

PCF85053A offers clock output calibration-related registers such as crystal capacitive load (CL) configuration and offset register setting.

## Bootable CPU RTC with Two I<sup>2</sup>C Buses, 128 Byte SRAM and Alarm Function Block Diagram

#### View additional information for Bootable CPU RTC with Two I<sup>2</sup>C Buses, 128 Byte SRAM and Alarm Function.

Note: The information on this document is subject to change without notice.

www.nxp.com NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. © 2024 NXP B.V.