#### **NXP Semiconductors**

# **Application Note**

Document Number: AN4998

Rev. 1, 07/2019

# MPC5746R Hardware Design Guide

by: NXP Semiconductors

### 1 Introduction

MPC5746R is a multi-core 32-bit microcontroller intended for automotive powertrain applications. It is based upon e200z4 Power® Architecture cores running at up to 200 MHz.

Throughout this application note, MPC5746R refers to the family of devices: MPC5743R, MPC5745R, and MPC5746R.

This application note details the options of MPC5746R power supplies and the correct external circuitry required for each supply, including digital, analog, and SRAM standby. It also discusses configuration options for clock, reset, and ADCs, as well as recommended debug and peripheral communication connections, and other major external hardware required for the device.

Please note that information from the MPC5746R Reference Manual, Data Sheet, and/or Errata report may be repeated in this application note for the convenience

#### **Contents**

| 1  | Introduction                                      |

|----|---------------------------------------------------|

| 2  | MPC5746R Package Options Overview                 |

| 3  | Power Supply                                      |

|    | Clock Circuitry                                   |

| 5  | Device Reset Configuration                        |

| 6  | Input/Output Pins                                 |

| 7  | Debug Options available                           |

| 8  | Emulation device                                  |

| 9  | ADC and Analog                                    |

| 10 | Example Communication Peripheral connections . 40 |

| 11 | References                                        |

| 12 | Revision History 51                               |

#### MPC5746R Package Options Overview

of the reader. The Reference Manual, Data Sheet and Errata report are the official specifications for MPC5746R and should be reviewed for the most up-to-date information available for this device.

# 2 MPC5746R Package Options Overview

The MPC5746R is available in four different package options; three of these are intended for production and one is intended to provide additional features to support debug and calibration.

| Package Target |             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|----------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 144 LQFP       |             | Provides access to the primary features of the device. Packages with additional pins provide                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 176 LQFP       | Production  | additional features and/or additional GPIO. No Nexus High Speed Aurora Trace interface is                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 252 MAPBGA     |             | provided on any production package, only JTAG.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 292 MAPBGA     | Development | Provides access to primary features of device, plus Nexus High Speed Aurora Trace and overlay/trace memory that can be used for calibration. This package is designed for debug and calibration development use and is typically provided mounted to an interposer/adapter system to connect to either a 144LQFP, 176 LQFP or 252 MAPBGA footprint. The Aurora debug interface connector is provided on this adapter board, eliminating the need for the customer to route the high speed Aurora differential pairs and allowing use on the customer PCB. |  |  |

Table 1. MPC5746R Package Options

The package selection should be based on the number of input/output pins required for the application and the area available for the target system. The following table shows the sizes of different packages. See the MPC5746R Data Sheet for complete package dimensions and ball placement. Drawings are also available on the NXP web site; search for the case outline number shown in Table 2.

| Package                 | Physical Size (mm) | Case Outline Number |

|-------------------------|--------------------|---------------------|

| 144 LQFP                | 20 x 20            | 98ASS23177W         |

| 176 LQFP                | 24 x 24            | 98ASS23479W         |

| 252 MAPBGA              | 17 x 17            | 98ASA00468D         |

| 292 MAPBGA <sup>1</sup> | 17 x 17            | 98ASA00261D         |

Table 2. Package Sizes

# 3 Power Supply

MPC5746R provides several options for providing power supply voltages. The main power supplies required are 1.25 V, 5 V and 3.3 V depending on the requirements of the application. The on-chip flash memory supply is generated internally. The SRAM has a separate supply input for data retention features, if they are required.

In addition the MPC5746R microcontroller includes a robust power management infrastructure that enables applications to select among various user modes and to monitor internal voltages for high- and

Only for development purpose and not intended for production.

low-voltage conditions. The monitoring capability is also used to ensure supply voltages and internal voltages are within the required ranges before the microcontroller can exit reset. The MPC5746R MCU supports three different input voltages:

- 1.25 V (required) for the internal logic. This supply may be provided externally or generated from either the 3.3 V or 5.0 V supply using an external NPN Bipolar Junction Transistor (BJT) ballast transistor and the internal 1.25 V regulator control.

- 5 V (required) for the Power Management controller, I/O, Debug, ADCs and external communication interfaces

- 3.3 V (optional) for I/O, Debug and external communication interfaces

The 3.3 V supply required for the flash memory is generated by an on-chip regulator. This regulator requires an external decoupling capacitor on VDD HV FLA.

#### 3.1 Power Supply Signals and Pins

Table 3 lists all power domains with corresponding pin names.

Supply Voltage<sup>1</sup> **Domain Name** Description VDD LV<sup>2</sup> 1.25 V Core Logic Low Voltage Supply VDD HV IO MAIN 5.0 V Main I/O Voltage Supply VDD HV ADV SAR 5.0 V SAR ADC Voltage Supply VDD\_HV\_ADR\_SAR SAR ADC Voltage Reference 5.0 V VDD HV ADV SD Sigma-Delta ADC Voltage Supply 5.0 V 5.0 V VDD\_HV\_ADR\_SD Sigma-Delta ADC Voltage Reference Production Device JTAG I/O and External Oscillator VDD\_HV\_IO\_JTAG 3.3 V or 5.0 V Voltage Supply VDD HV IO FEC 3.3 V or 5.0 V Ethernet I/O Supply VDD\_HV\_IO\_MSC 3.3 V or 5.0 V Microsecond Channel I/O Supply VDD HV PMC 5.0 V Power Management Controller Supply VDD HV FLA<sup>3</sup> 3.3 V PMC Flash Regulator Bypass Capacitor VDD LV BD4 1.25 V Emulation Device Core Logic Low Voltage Supply VDD HV IO BD4 3.3 V or 5.0 V Emulation Device Main I/O Voltage Supply VDDSTBY<sup>5</sup> 1.3 V-5.9 V Standby RAM Supply Input

**Table 3. MCU Supply Pins**

Nominal voltage, see MPC5746R Data Sheet for actual voltage specifications.

<sup>&</sup>lt;sup>2</sup> This supply may be optionally provided by the on-chip regulator using a pass transistor. See Section 3.1.2

<sup>&</sup>lt;sup>3</sup> No connection to external supply required, but it does require a bypass capacitor.

Only present on the 292 MAPBGA emulation device.

Ramp rate must be less than 16.6 kV/s as per limitation for the 0N94H mask set. Refer to the latest MPC5746R Data Sheet for additional requirements.

#### **Power Supply**

Some of the supplies can be powered with different supply voltages. In particular, the MCU allows flexibility in the supply of voltages that power selected input and output pins. These supplies are "high" supplies and can be connected to either a nominal 3.3 V or 5.0 V supply. In addition we recommend keeping all supply slew rates below 25 V/ms.

Refer to the MPC5746R Data Sheet to learn what voltages can be connected to the power pins. Supply pins/balls differ from package to package. Please refer to section 3.1.1 for package differences.

The following table shows several power supply design schemes. The flexibility of the supply configurations provides the board designer several options for optimizing the design.

| Supply options                   | Reference     |

|----------------------------------|---------------|

| Single 5 V supply                | Section 3.1.2 |

| Multi supply with 5 V and 3.3 V  | Section 3.1.3 |

| Multi supply with 5 V and 1.25 V | Section 3.1.4 |

Table 4. Power supply schemes

Please refer to the IO description attached to the MPC5746R Reference Manual for more details.

# 3.1.1 Power supply package differences

There are different numbers of balls/pins available for the power supplies in each of the MPC5746R package options. In addition, for some package options, some power supplies are not available. The table below shows, for each package, the number of balls available for the power supply input to the device. All supply balls that are available on the package should be connected to a supply voltage.

| Supply Domain           | Nominal Voltage | 144LQFP | 176LQFP | 252BGA |

|-------------------------|-----------------|---------|---------|--------|

| VDD_LV <sup>1</sup>     | 1.25 V          | 6       | 6       | 14     |

| VDD_HV_IO_MAIN          | 5.0 V           | 5       | 5       | 7      |

| VDD_HV_ADV_SAR          | 5.0 V           | 1       | 1       | 2      |

| VDD_HV_ADR_SAR          | 5.0 V           | 1       | 1       | 1      |

| VDD_HV_ADV_SD           | 5.0 V           | 1       | 1       | 1      |

| VDD_HV_ADR_SD           | 5.0 V           | 1       | 1       | 1      |

| VDD_HV_IO_JTAG          | 3.3 V or 5.0 V  | 1       | 1       | 1      |

| VDD_HV_IO_FEC           | 3.3 V or 5.0 V  | 1       | 1       | 1      |

| VDD_HV_IO_MSC           | 3.3 V or 5.0 V  | 1       | 1       | 1      |

| VDD_HV_PMC              | 5.0 V           | 1       | 1       | 1      |

| VDD_HV_FLA <sup>2</sup> | 3.3 V           | 1       | 1       | 1      |

| VDD_LV_BD <sup>3</sup>  | 1.25 V          | -       | -       | -      |

Table 5. Number of power supply balls/pins versus package

MPC5746R Hardware Design Guide, Rev. 1

Table 5. Number of power supply balls/pins versus package

| Supply Domain             | Nominal Voltage | 144LQFP | 176LQFP | 252BGA |

|---------------------------|-----------------|---------|---------|--------|

| VDD_HV_IO_BD <sup>4</sup> | 3.3 V or 5.0 V  | -       | -       | -      |

| VDDSTBY <sup>4</sup>      | 1.3 V - 5.9 V   | 1       | 1       | 1      |

This supply may be optionally provided by the on-chip regulator using a pass transistor. See Section 3.1.2

# 3.1.2 Single 5 V Supply

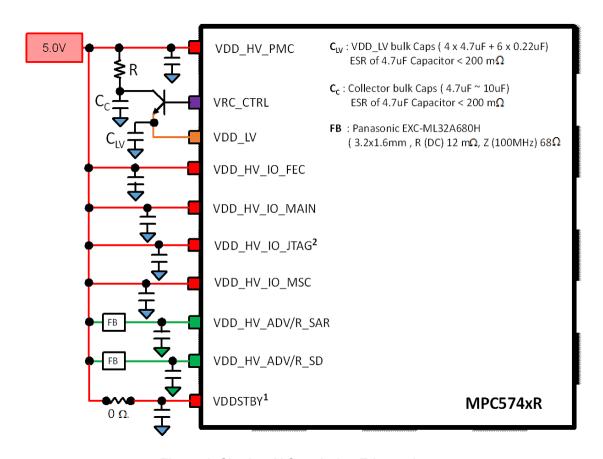

This topology uses a single 5 V supply for all I/O, with the internal regulator providing the 1.25 V for the VDD\_LV core supply. Note that most Fast Ethernet Controller (FEC) physical layer interfaces require 3.3 V signals, so the FEC would not normally be operational in this configuration.

Figure 1. Single 5 V Supply (no Ethernet)

<sup>&</sup>lt;sup>2</sup> Except bypass capacitor no connection to external supply required.

<sup>&</sup>lt;sup>3</sup> Only present on the 292 MAPBGA emulation device.

Ramp rate must be less than 16.6 kV/s as per limitation for the 0N94H mask set. Refer to the latest MPC5746R Data Sheet for additional requirements.

<sup>&</sup>lt;sup>1</sup> VDDSTBY may need to be powered by a separate supply in the case where the standby SRAM data retention feature is required. This figure is intended to illustrate that a single 5 V supply may be used where appropriate for the design.

<sup>&</sup>lt;sup>2</sup> VDD\_HV\_IO\_JTAG is typically powered by a 3.3 V supply for compatibility with many debug tools. However if tools support 5 V or JTAG access is not required, a 5 V supply may be used and the JTAG pins can be used as normal GPIO.

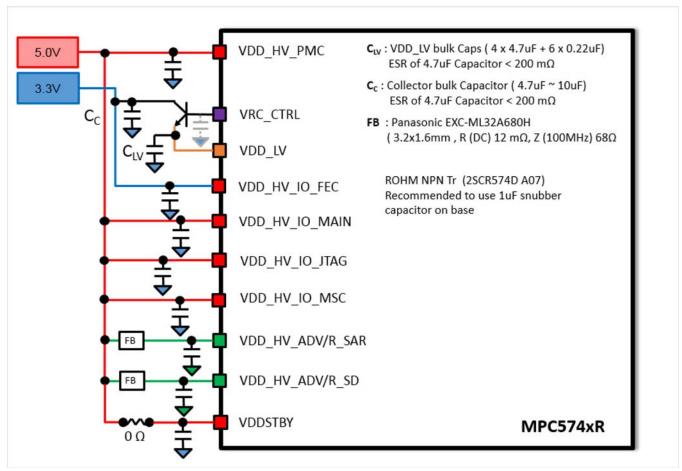

#### 3.1.3 Multi Supply - 5 V and 3.3 V

In this configuration there are dual supply voltages, 5 V and 3.3 V. The 5 V supply provides the I/O supply, the internal regulator provides the 1.25 V core supply and the 3.3 V supply is used to power the FEC subnet.

Figure 2. Multi Supply, 5 V and 3.3 V with Ethernet

#### NOTE

$\mbox{VDD\_HV\_IO\_JTAG}$  and/or  $\mbox{VDD\_HV\_IO\_MSC}$  could also be powered by 3.3 V.

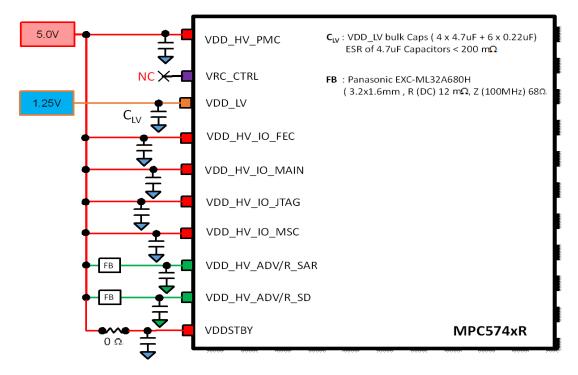

# 3.1.4 Multi Supply: 5.0 V and 1.25 V

In this configuration there are dual supply voltages, 5 V and 1.25 V. I/O is powered by the 5 V supply and the core voltage is powered by the 1.25 V supply. Note that most Fast Ethernet Controller (FEC) physical layer interfaces require 3.3 V signals, so the FEC would not normally be operational in this configuration.

Figure 3. Multi Supply, 5 V and 1.25 V without Ethernet

## 3.1.5 Decoupling Capacitor Recommendation for supply domains

Table 6 shows all power domains and the suggested decoupling and/or filter capacitors for their corresponding pins. These values are provided as a guideline and will vary depending on the application and capability of the power supplies used.

| Domain              | Supply Voltage | Bulk                | Bypass (each pin) |

|---------------------|----------------|---------------------|-------------------|

| VDD_LV <sup>1</sup> | 1.25 V         | 4.7 μF <sup>2</sup> | 220nF ~ 47 nF     |

| VDD_HV_IO_MAIN      | 5.0 V          | 4.7 uF <sup>3</sup> | 100nF ~ 10 nF     |

| VDD_HV_ADV_SAR      | 5.0 V          | 10 μF               | 220nF ~ 100 nF    |

| VDD_HV_ADR_SAR      | 5.0 V          | -                   | 220nF ~ 100 nF    |

| VDD_HV_ADV_SD       | 5.0 V          | 4.7 μF              | 220nF ~ 100 nF    |

| VDD_HV_ADR_SD       | 5.0 V          | -                   | 220nF ~ 100 nF    |

| VDD_HV_IO_JTAG      | 3.3 V or 5.0 V | 4.7 μF              | 220nF ~ 100 nF    |

| VDD_HV_IO_FEC       | 5.0 V or 3.3 V | 4.7 μF              | 220nF ~ 100 nF    |

| VDD_HV_IO_MSC       | 5.0 V or 3.3 V | 4.7 μF              | 220nF ~ 100 nF    |

| VDD_HV_PMC          | 5.0 V          | 4.7 μF              | 220nF ~ 47 nF     |

**Table 6. Supply Decoupling Requirements**

MPC5746R Hardware Design Guide, Rev. 1

| Table 6. Supply Decoupl | ing Requirements |

|-------------------------|------------------|

|-------------------------|------------------|

| Domain                    | Supply Voltage | Bulk        | Bypass (each pin) |

|---------------------------|----------------|-------------|-------------------|

| VDD_HV_FLA <sup>4</sup>   | 3.3 V          | 1 μF~2.2 μF | 1 nF              |

| VDD_LV_BD <sup>5</sup>    | 1.25 V         | 4.7 μF      | 100 nF            |

| VDD_HV_IO_BD <sup>5</sup> | 5.0 V          | 4.7 μF      | 100 nF            |

| VDDSTBY                   | 1.3 V-5.9 V    | 1 μF        | 100 nF            |

This supply may be optionally provided by the on-chip regulator using a bipolar junction transistor (BJT). See Section 3.1.2.

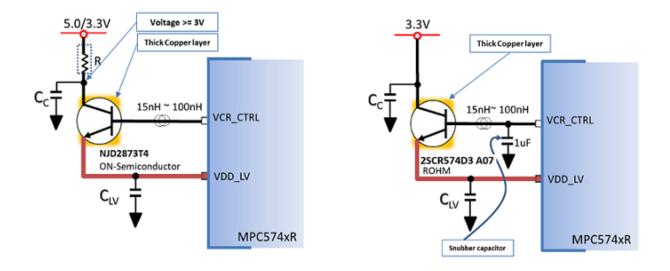

# 3.2 On-chip 1.25 V Regulator

In order to lower system cost, MPC5746R provides an on-chip regulator that can use an external NPN pass transistor to provide the 1.25 V core supply voltage from either a 5.0 V or 3.3 V supply. The recommended external circuits are shown in Figure 4.

Figure 4. 1.25 V Supply with external pass Transistor

When the 5.0 V supply configuration is in use, the internal regulator regulates the BJT emitter voltage to 1.25[V], which is used as the core supply (VDD\_LV). The remaining energy needs to be dissipated via the transistor as heat. The capability of the transistor package to dissipate heat degrades as the temperature increases. To overcome such problems, the user should analyze the thermal capabilities of the transistor and add sufficient heat dissipation options as needed.

<sup>&</sup>lt;sup>2</sup> Recommend 4 x 4.7 uF bulk capacitors with lower ESR (each < 200 mΩ) for VDD\_LV supply domain.

<sup>&</sup>lt;sup>3</sup> Recommend 5 x 4.7 uF bulk capacitors for VDD HV IO MAIN supply domain.

<sup>&</sup>lt;sup>4</sup> No connection to external supply required.

<sup>&</sup>lt;sup>5</sup> Only present on the 292 MAPBGA emulation device.

There are several options available: 1) use a heat sink 2) populate a copper layer(s) beneath the transistor with thermal VIAS to improve the heat dissipation. NXP recommends consulting the transistor vendor to obtain optimal thermal design.

As another option, an external resistor can be used to minimize the extra heat. The resistor will drop the collector voltage to mitigate the heat dissipation of the pass transistor (BJT). In this case, the collector voltage needs to be maintained at 3 V or above.

NXP recommends a low inductance between the transistor base and the VRC\_CTRL pin/pad. This should be less than 100nH. An inductance of 15nH is an optimal value.

The following examples explain how to calculate the power dissipation of the BJT with different resistor (R) values.

#### Example.1:

Supply voltage is 5.0 V, R=1.8  $\Omega$ , Max current consumption at VDD\_LV ( $I_{vdd_lv}$ ) = 700 [mA] and nominal VDD LV = 1.25 [V]

Voltage drop across the R =  $1.8 \Omega \times 700 \text{mA} = 1.260 \text{ [v]}$ , voltage at collector 5 V-1.26 V = 3.74 [V] (> 3 V)

Power dissipation on BJT transistor P (Tr): P (Tr) =  $(5 - 1.25 - 1.26) \times 0.7 = 1.743$  [w]

Power dissipation on resistor P(R): P(R)= 1.26 x 0.7 = 0.882 [w]

#### Example.2:

Supply voltage is 5.0 V, R=2.0  $\Omega$ , Max current consumption at VDD\_LV ( $I_{vdd_lv}$ ) = 700 [mA] and nominal VDD LV = 1.25 [V]

Voltage drop across the R =  $2.0 \Omega x 700 \text{mA} = 1.400 \text{ [V]}$ , voltage at collector 5 V-1.4 V = 3.6 [V] (> 3 V)

Power dissipation on BJT transistor P (Tr) given by:  $P(Tr) = (5 - 1.25 - 1.40) \times 0.7 = 1.645 \text{ [w]}$

Power dissipation on resistor P(R) given by:  $P(R) = 1.40 \times 0.7 = 0.980 \text{ [w]}$

#### 3.2.1 Recommended Pass Transistor

The on-chip 1.25 V regulator requires an external BJT for operation. Refer to the following table for recommended pass transistors. Please refer to the MPC5746R Data Sheet to obtain the requirements for the BJT device.

|                    |                                       |                | ı        |                |

|--------------------|---------------------------------------|----------------|----------|----------------|

| Transistor         | Collector capacitor (C <sub>C</sub> ) | Base capacitor | Resistor | Supply options |

| ON semiconductor   | 4.7 uF (min) ESR<200 mΩ               | -              | 2 Ω      | 5.0 V          |

| NJD2873T4          |                                       |                |          |                |

| ON semiconductor   | 4.7 uF (min) ESR<200 mΩ               | -              | -        | 3.3 V          |

| NJD2873T4          |                                       |                |          |                |

| ROHM 2SCR574D3 A07 | 4.7 uF (min) ESR<200 mΩ               | 1 uF           | -        | 3.3 V          |

**Table 7. Recommended pass Transistors**

MPC5746R Hardware Design Guide, Rev. 1

#### 3.3 External 1.25 V Supply

If an external regulator is used for the VDD\_LV supply, the pass transistor is not required. In this case, the internal voltage regulator driver should be disabled by setting the REG\_SEL bit in the Miscellaneous Device Configuration Format (DCF) client. This is accomplished via a DCF record programmed into the UTEST flash memory. See the DCF Chapter of the MPC5746R Reference Manual for complete information regarding the use of DCF records and UTEST flash memory.

Note that the VRC\_CTRL will remain active until the Reset Generation Module (RGM) enters the reset phase 3, where the UTEST configuration is read. When using an external VDD\_LV supply, the VRC\_CTRL pin should be left floating (no connect). See the RGM chapter of the MPC5746R Reference Manual for more information.

# 3.4 Input and output pins power supply segmentation

Each I/O pin is associated with one of the power domains. The majority of the I/O pins are powered by the VDD\_HV\_IO\_MAIN. The VDD\_HV\_IO\_JTAG, VDD\_HV\_IO\_FEC, and VDD\_HV\_IO\_MSC domains are primarily intended to allow the JTAG, FEC and MSC interfaces to be operated at a voltage level different from the VDD\_HV\_IO\_MAIN domain if desired. However, they can also be used to power a limited amount of I/O pins at an alternative voltage level.

The voltage level supplied on any I/O domain determines the output voltage level and input transition levels for the I/O pins associated with that domain. Each power domain with corresponding I/O pins is shown in Table 8. Each power domain needs to be maintained below 80 mA. In addition, the sum of all I/O power domains should be maintained below 200mA as described in the MPC5746R Data Sheet. Note that, not all of the listed I/O pins are available on some packages. <sup>1</sup>

| Power Domain   | I/O Pins                                                                                   |

|----------------|--------------------------------------------------------------------------------------------|

| VDD_HV_IO_MAIN | PD[0–15] PE[0] PF[0–13] PG[1–7, 9–15] PH[0–15] PI[0–5] PJ[0–15] PK[0–2, 4–5, 7–14] PL[0–1] |

| VDD_HV_IO_JTAG | PB[0-1]                                                                                    |

| VDD_HV_IO_FEC  | PC[0-13]                                                                                   |

| VDD_HV_IO_MSC  | PA[0-13]                                                                                   |

| VDD_HV_ADV_SAR | PW[0-3]<br>PX[0-15]<br>PY[0-15]                                                            |

| VDD_HV_ADV_SD  | PZ[0-15]                                                                                   |

Table 8. Power Domains vs. I/O

MPC5746R Hardware Design Guide, Rev. 1

#### 3.5 Decoupling capacitor layout priorities

When trade offs must be made in the layout, it is important to ensure that the highest priority decoupling capacitors are placed as close as possible to the MCU. The list below orders the power supply domains from highest to lowest priority in terms of decoupling capacitor placement.

| Priority | Domain                          | Description                        |

|----------|---------------------------------|------------------------------------|

| 1        | VDD_HV_ADR_SAR<br>VDD_HV_ADR_SD | ADC references                     |

| 2        | VDD_HV_ADV_SAR<br>VDD_HV_ADV_SD | ADC supplies                       |

| 3        | VDD_HV_IO_JTAG                  | JTAG debug and XOSC supply         |

| 4        | VDD_LV                          | Core(s) supply                     |

| 5        | VDD_HV_PMC                      | Power Management Controller supply |

| 6        | VDD_HV_FLA                      | Flash memory supply/decouple       |

| 7        | VDD_HV_IO_MAIN                  | GPIO supply                        |

| 8        | VDD_HV_IO_MSC                   | Microsecond channel supply         |

| 9        | VDDSTBY                         | SRAM standby voltage               |

**Table 9. Decoupling Capacitor Layout Priorities**

- Highest priority is given to the analog-to-digital converters reference and power supply decoupling: VDD\_HV\_ADR\_SAR, VDD\_HV\_ADR\_SD, VDD\_HV\_ADV\_SAR, and VDD\_HV\_ADV\_SD. Clean supplies are vital to ensure that the highest accuracy is achieved with the ADCs. In addition, linear supplies must be used as analog references. The supply for the oscillator (VDD\_HV\_IO\_JTAG) is also prioritized as this helps to ensure reliable and stable operation from the external oscillator.

- Medium priority is given to VDD\_LV, VDD\_HV\_PMC, and VDD\_HV\_FLA. VDD\_LV is the

main supply for the on-chip digital logic, including the cores, and this is prioritized because it

affects the largest amount of logic on the device. VDD\_HV\_PMC powers the flash regulator and

VDD\_HV\_FLA is the output of this regulator. A good supply to the flash memory ensures reliable

flash programming and erasing.

- VDD\_HV\_IO\_MAIN, VDD\_IO\_MSC, and VDDSTBY are given lower priority. Although it is still important that these supplies have a clean power signal, the hardware they power is less affected by noise.

# 3.6 Supply monitoring

MPC5746R monitors the voltage supplies internally. The function of the power-on reset (POR), low-voltage detect (LVD) and high-voltage detect (HVD) circuits is to hold the device in reset until critical

MPC5746R Hardware Design Guide, Rev. 1

<sup>1.</sup>See the MPC5746R Reference Manual for complete information on the power segmentation, input multiplexing and other pin characteristics.

#### **Power Supply**

voltages are in specification. LVD/HVD monitor limits are shown in Table 10 for your reference. Use the latest MPC5746R Data Sheet for the final specification values. The device is held in reset regardless of how slow the supply voltage rise is, until the point at which the POR and LVDs are released.

Configuration Trim Mas Pow Min Тур Max Unit Conditions Symbol Parameter bits Up Opt. POR098\_c LV internal supply power on Rising voltage (power up) N/A No 960 1060 mV Enab 1010 reset Falling voltage (power down) 1040 940 990 LVD core LV internal<sup>2</sup> supply low voltage Rising voltage (trimmed) mV 6bit 1146 1169 1193 No Enab monitoring hot Falling voltage (trimmed) 1146 1169 1193 LV external supply low voltage Rising voltage Disa 1161 1185 1208 cold monitoring b. Falling voltage 1185 1208 1161 HVD\_core LV internal cold supply high Rising voltage 6bit Disa 1353 1395 1438 mV voltage monitoring b. 1438 LVD\_HV HV internal supply low voltage Rising voltage (trimmed) No Enab 3300 3400 3500 mV 6bit monitoring 3470 Falling voltage (trimmed) 3270 3370 Rising voltage 5870 HVD HV HV internal supply high voltage Disa 5530 5700 mV 6bit Yes monitoring b. Falling voltage 5670 5840 LVD\_IO Main IO and RC oscillator Rising voltage (trimmed) 6bit Enab 3300 3400 3500 mV supply voltage monitoring Falling voltage (trimmed) 3270 3370 3470 LVD\_SAR | SAR ADC supply low voltage Rising voltage 2820 2910 3000 monitoring b. Falling voltage 2790 2880 2970 These Voltage Monitors are always enabled in the MPC574xR. These Disabled Monitors can be enabled via PMC REE register.

Table 10. Voltage monitor electrical characteristics

By default VDD\_LV internal POR (POR085\_c/POR098\_c), internal core voltage monitor (LVD\_core\_hot), VDD\_HV\_PMC voltage monitor (LVD\_HV) and VDD\_HV\_IO\_MAIN voltage monitor (LVD\_IO) are enabled. As shown in the mask option field under configuration column of the Table 10, the user can enable/disable the voltage monitors of LVD/HVD by either of following methods.

- 1. Program the PMC\_REE register directly by the application software. But, this method is only valid for LVD core cold, HVD core, HVD HV and LVD SAR configurations.

- 2. Program the PMC\_REE\_DCF\_client DCF record into the UTEST area. With this option, the user can disable the LVD\_core\_hot, enable the LVD\_core\_cold, HVD\_core, HVD\_HV and LVD\_SAR configurations. Note that the default configuration will remain active until the RGM enter phase 3, where the UTEST configuration is read.

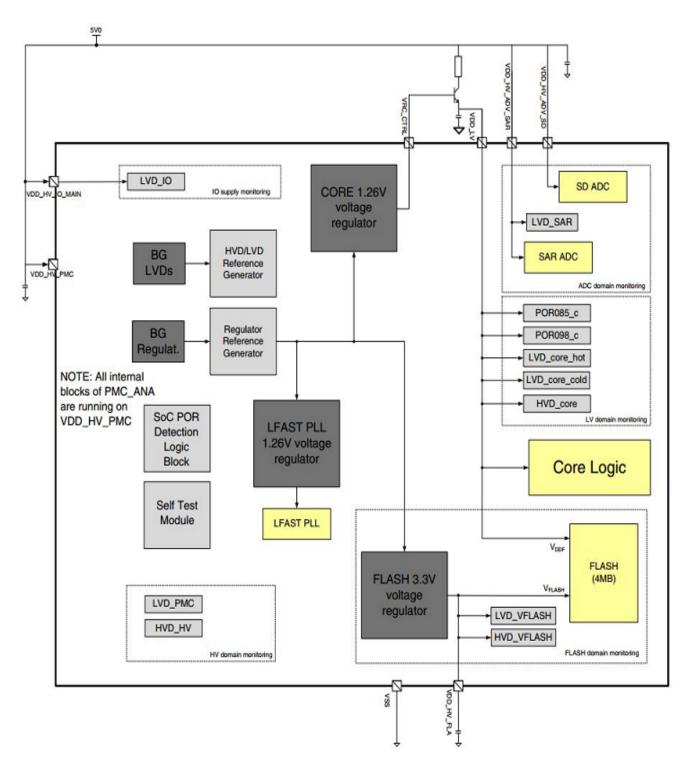

The POR and LVD circuits function correctly even if the input voltage is non-monotonic. A diagram illustrating the on-chip LVD/HVD circuits is shown in Figure 5. For detailed information on the low-voltage detect (LVD) and high-voltage detect (HVD) circuits, please refer to the MPC5746R Reference Manual and Data Sheet.

Figure 5. LVD and HVD Implementation

#### 3.6.1 Behavior of LVD / HVD

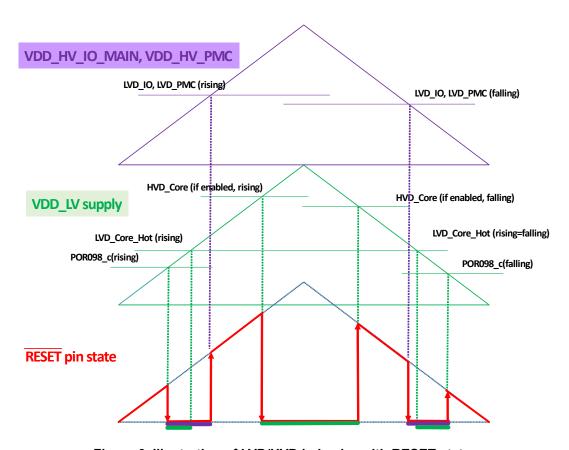

The internal LVD circuits monitor the voltage on the corresponding supply. If the supply falls below defined values, the LVD asserts either a reset or an interrupt. Figure 6 illustrates how the RESET behaves with different LVD/HVD levels. The LVDs also support hysteresis for the falling and rising trip points.

Although there is an option to disable the LVDs and HVDs following reset, they are capable of being used in a 'monitor' only mode and also capable of generating a safe/interrupt event. The LVDs/HVDs can also be configured after device initialization, preventing a reset when a supply crosses the LVD threshold, providing a higher voltage range. The customer application should monitor and verify that the device voltage supply levels remain in the functional range.

#### **NOTE**

VDD\_LV internal supply power on reset monitors (POR085\_c and POR098\_c) cannot be disabled. These trip points are used during the power-up phase and must ensure that an absolute lowest voltage threshold for operation is never crossed. This is not a guarantee that the device will function down to this level. It is rather a guarantee that the device will be reset if this level is crossed.

Figure 6. Illustration of LVD/HVD behavior with RESET status

#### 3.6.2 Power-on reset

The power management controller (PMC) controls the Power-On reset (POR) for the MCU. When the critical power supplies are below minimum levels, the MCU is held in the POWER-UP phase of the reset state machine (see the Reset and Boot chapter of the MPC5746R Reference Manual), until the power supplies have reached their specified levels. Power sequencing is not necessary. When the required voltage levels have been reached, the reset generation module (RGM) propagates the device through the next steps of the boot process.

The PMC has three internal power-on reset circuits:

- 1.25 V input supply This circuit monitors the VDD\_LV pin and asserts a reset when the input supply is below defined values.

- POR085\_c monitors the voltage on the 1.25 V input supply on the VDD\_LV pin. POR085\_c asserts a reset when the input supply is below defined values.

- POR098\_c monitors the voltage on the 1.25 V input supply on the VDD\_LV pin. POR098\_c asserts a reset when the input supply is below defined values. The POR098\_c trip point makes sure that the voltage is high enough for LV logic to initialize and recognize RESET assertion, ensuring the correct logic state. At this point all the LVD circuits become functional.

- 5.0 V input supply This circuit monitors the VDD\_HV\_PMC pin and ensures the PORST trip point is high enough to make sure all the LVD circuits are functional.

- LVD\_HV monitors the voltage on the 3.5 5.0 V input supply at the VDD\_HV\_PMC pin, the actual PMC module supply. The POR trip point is high enough to make sure all the LVD circuits are functional i.e. to ensure that the VDD\_HV\_PMC supply is in range to allow all PMC internal circuits to operate reliably.

- The LVD\_VFLASH monitors the flash input voltage and is used to control the power-up sequence, ensuring the flash memory can be accessed prior to the reset phase 0 being completed.

POR085\_c2 and POR098\_c2 are used for redundancy. Minimum and maximum values and trigger conditions for each LVD and HVD monitor can be found in the MPC5746R Data Sheet. See the Reset chapter in the MPC5746R Reference Manual for PORST/RESET pin functionality.

# 3.6.3 Low-Voltage (LVD) and High-Voltage Detection (HVD)

- All LVDs and HVDs are capable of generating reset.

- All LVDs and HVDs configured for reset generation cause functional or destructive reset. MC RGM PHASE0 is not exited until all destructive reset conditions are cleared.

- The appropriate bits in the PMC registers are set by LVD and HVD events.

- LVD and HVD control is protected by the System-on-Chip (SoC) wide register protection scheme.

- There are user option bits available to allow degrade of configurable LVDs/HVDs from destructive reset down to functional reset. This is a write once mechanism managed by System Status and Configuration Module (SSCM) during device initialization.

- When the LVD or the HVD is enabled for destructive reset generation, and a trigger event is detected, the external PORST pin is driven low.

# 3.6.4 Analog module self-test and parameter monitoring

The ADC interface includes connections to the PMC internal voltages for diagnostic purposes. An analog multiplexer and the buffer are inside the PMC. SAR ADC0 converts the selected voltage, which can then be evaluated by the CPU. Voltages in the PMC module can be monitored with the ADC and the ADC does not impact the PMC voltage levels. These signals are used for calibration, diagnostics during test or to allow the application to actively monitor the signal levels. There is a dedicated ADC channel for these monitoring purposes.

Table 11 lists all the internal test signals that can be monitored using SAR ADC0.

Table 11. ADC 0 Mux Interface

| PMC_ADC_CS[ADC_CHSE] | ADC Channel Output          | Typical Value        |

|----------------------|-----------------------------|----------------------|

| 6'b000000            | ADC Channel Off             |                      |

| 6'b011110            | por085_c sense value        | 1.25 V (CORE supply) |

| 6'b011101            | por085_c reference value    | 0.915 V              |

| 6'b011100            | por098_c sense value        | 1.25 V (CORE supply) |

| 6'b011011            | por098_c reference value    | 1.01 V               |

| 6'b011010            | por085_c2 sense value       | 1.25 V (CORE supply) |

| 6'b011001            | por085_c2 reference value   | 0.905 V              |

| 6'b011000            | por098_c2sense value        | 1.25 V (CORE supply) |

| 6'b010111            | por098_c2 reference value   | 0.993 V              |

| 6'b010110            | lvd_core_cold sense         | 1.25 V (CORE supply) |

| 6'b010101            | lvd_core_cold_reference     | 1.24 V               |

| 6'b010100            | lvd_core_hot_sense          | 1.25 V (CORE supply) |

| 6'b010011            | lvd_core_hot_reference      | 1.21 V               |

| 6'b010010            | hvd_core_sense              | 1.25 V (CORE supply) |

| 6'b010001            | hvd_core_reference          | 1.43 V               |

| 6'b010000            | por260_c divider tap point  | 2.55 V               |

| 6'b001111            | por260_c reference          | 1.2 V                |

| 6'b001110            | por260_c2 divider tap point | 2.55 V               |

| 6'b001101            | por260_c2 reference         | 1.2 V                |

| 6'b001100            | lvd_pmc divider tap point   | 1.98 V               |

| 6'b001011            | lvd_pmc reference           | 1.2 V                |

| 6'b001010            | hvd600 divider tap point    | 1.13 V               |

| 6'b001001            | hvd600 reference            | 1.2 V                |

| 6'b001000            | lvd_flash divider tap point | 1.31 V               |

| 6'b000111            | lvd_flash reference         | 1.2 V                |

| 6'b000110            | hvd_flash divider tap point | 1.13 V               |

Table 11. ADC 0 Mux Interface

| PMC_ADC_CS[ADC_CHSE] | ADC Channel Output                       | Typical Value       |

|----------------------|------------------------------------------|---------------------|

| 6'b000101            | hvd_flash reference                      | 1.2 V               |

| 6'b000100            | lvd_io divider tap point                 | 1.97 V              |

| 6'b000011            | lvd_io reference                         | 1.2 V               |

| 6'b000010            | Reserved                                 | _                   |

| 6'b000001            | Reserved                                 | _                   |

| 6'b000000            | Reserved                                 | _                   |

| 6'b1111111           | Reserved                                 | _                   |

| 6'b111110            | Reserved                                 | _                   |

| 6'b111101            | Reserved                                 | _                   |

| 6'b111100            | Reserved                                 | _                   |

| 6'b111011            | Reserved                                 | _                   |

| 6'b111010            | lvd_buddy reference                      | 1.05 V              |

| 6'b111001            | lvd_buddy sense                          | 1.2 V (BD supply)   |

| 6'b111000            | lvd_sar_adc divider tap point            | 2.25 V              |

| 6'b110111            | lvd_sar_adc reference                    | 1.2 V               |

| 6'b110110            | hvd_sar_adc divider tap point            | 1.13 V              |

| 6'b110101            | hvd_sar_adc reference                    | 1.2 V               |

| 6'b110100            | bandgap voltage with only curve trimming | 1.205 V             |

| 6'b110011            | nwellbias regulator output               | 1.25 V              |

| 6'b110010            | nwellbias regulator reference            | 1.25 V              |

| 6'b100100            | ioseg3_sense                             | VDD_HV_IO segment 3 |

| 6'b100011            | ioseg2_sense                             | VDD_HV_IO segment 2 |

| 6'b100010            | vrefh_sd_adc                             | 5 V                 |

| 6'b100001            | vrefh_sd_adc                             | 5 V                 |

| 6'b100000            | vss_sd_adc                               | 0 V                 |

# 3.7 Power sequence

The following section describes the power sequence and the relationship between the different supplies during power-up and power-down.

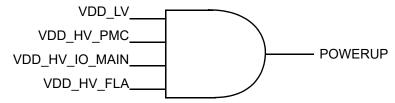

The device is considered to be in a power sequence (or POWERUP state) when the power is not supplied or is only partially powered. An internal power-on signal is used to identify the POWERUP state. This signal is released high on exit of the power sequence. The power-on signal is a combination of certain LVDs that are monitoring supplies:

Figure 7. Logical connection between power domains

The actual threshold used for each LVD depends on the configuration of the device. This is configurable by hardware (flash option bit settings) or by software (LVD event configuration through a register interface). Once the power-on signal has been asserted, the device configuration is reset to default power-up configuration; during the initialization phase, the device defaults to a pre-determined state for each of the LVDs, HVDs, and the internal regulators. As the flash memory becomes available, the differential read process allows the trimmed data to be available for trimming the internal LVDs, HVDs, and regulators.

#### 3.7.1 Power-up sequence

In this section, the assumption is made that all supplies are low when entering the power-up sequence. Brown-out and power down sequences are discussed in following sections.

At the beginning of power-up, the internal power-on signal remains low due to the parasitic diodes. As soon as the minimum threshold is reached on VDD\_LV, the power-on signal is forced low. It remains low until the power-up LVDs reach their upper (not trimmed) threshold. During power-up, all functional pins are maintained in a known state as described in Table 12.

| Pin Type | POWERUP<br>Pad State | During RESET<br>Pad State | Out of RESET<br>Pad State |

|----------|----------------------|---------------------------|---------------------------|

| PORST    | strong pull-down     | weak pull-down            | weak pull-down            |

| RESET    | strong pull-down     | weak pull-up              | weak pull-up              |

| GPIO     | high impedance       | weak pull-up              | weak pull-up              |

| ANALOG   | high impedance       | high impedance            | high impedance            |

| ERROR    | high impedance       | high impedance            | high impedance            |

| JCOMP    | high impedance       | weak pull-down            | weak pull-down            |

| TCK      | high impedance       | weak pull-down            | weak pull-down            |

| TMS      | high impedance       | weak pull-up              | weak pull-up              |

| TDI      | high impedance       | weak pull-up              | weak pull-up              |

| TDO      | high impedance       | high impedance            | high impedance            |

Table 12. Functional Terminal State - Power-Up and Reset

The power-up sequence is as follows:

- 1. Digital reset is asserted, ensuring that all module registers are reset to their power-on value.

- 2. The POWERUP state is exited when both VDD LV and VDD HV are above threshold.

- 3. After both LV, HV and temperature POWERUP exit conditions have been verified, the internal power-on signal is released to all analog modules.

- 4. The internal RC oscillator module starts initialization and provides a clock to the system. The PMC digital interface reset is released after two RC clock cycles.

- 5. The device proceeds with the reset sequence through RGM phase PHASE0, PHASE1[DEST], PHASE2[DEST] and PHASE3[DEST].

- 6. Voltage detector (LVD/HVD) modules are trimmed at the beginning of PHASE3[DEST]. Trimming of the LVDs/HVDs is done by the SSCM at low voltage. After trimming is completed, the SSCM waits for PMC acknowledge to proceed with the reset sequence.

- 7. The configurable LVD/HVD modules are optionally enabled at the beginning of PHASE3[DEST] by programming the PMC\_REE/PMC\_RES DCF records. After trimming, the PMC interface monitors all the HVD/LVD outputs that have been enabled by the flash user option bits. When all enabled LVDs/HVDs are released and the analog temporization period has elapsed, LVDs/HVDs are unmasked.

- 8. When the LVDs are masked, the device relies on the PORST signal to detect a voltage failure during power-up. The device must wait for PORST to be released high before proceeding with power-up sequence. This may increase the amount of time necessary to complete the reset sequence.

- 9. After all LVDs/HVDs are unmasked the SSCM proceeds with the reset sequence, eventually running full speed accesses to the extended flash option bits required to complete device configuration.

- 10. The VDD HV conditions to exit POWERUP are as follows:

- LVD HV and LVD IO upper threshold is crossed

- LVD VFLASH is crossed

#### 3.7.2 Power-down sequence

During power down, any time the VDD\_HV or the VDD\_LV supply crosses the respective LVD threshold, the device enters the POWERUP state. The power-down sequence is entered as soon as the threshold of one of the LVD\_HV, LVD\_IO, LVD\_core\_hot, LVD\_VFLASH or POR98 is crossed. The device supplies may then proceed to drop down to ground either through device leakage or external pull-down.

### 3.7.3 Brown-out management

During brown-out, the MPC57xx devices re-enter the POWERUP phase as soon as the LVD/HVD threshold of either VDD LV or VDD HV is crossed.

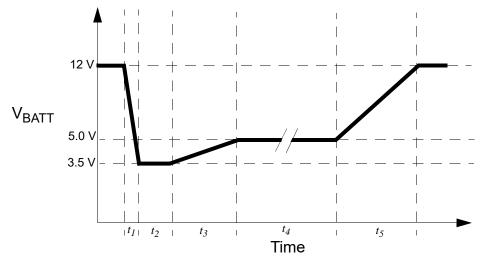

#### 3.7.4 Low voltage during crank

The device is able to continue operation at the minimum input voltage during cranking. In order to proceed with execution during cranking and prevent device reset, it is important to correctly configure the high voltage LVDs. Figure 8 illustrates a typical cranking voltage profile.

Figure 8. Example Cranking Voltage Profile

The above diagram shows the input voltage falling to 3.5 V at the battery terminals. Several options are available to filter the supply sag.

- DC-DC converters to boost the supply

- Additional capacitance to filter the sag

- External power supply system asserts a reset

# 4 Clock Circuitry

MPC5746R can use either the internal RC oscillator, an external crystal or an external clock as the reference clock. This reference is qualified by multiple methods before the Phase-Locked Loop (PLL) will begin lock operation. The 'pre' Frequency-Modulated Phase-Locked Loop (FMPLL) circuitry consists of an automatic level-controlled amplifier, a comparator, a loss of clock detector, and a pre-divider.

Care must be taken in the layout and design of the circuitry around the crystal and FMPLL power supplies. Any noise in these circuits can affect the accuracy of the clock source to the FMPLL. The PLLs are powered by VDD\_LV. The oscillator (OSC) is powered by VDD\_HV\_IO\_JTAG. Noise on either of these supplies can affect the accuracy and jitter performance of the oscillator and PLLs.

In order to minimize any potential noise, connect the capacitors recommended in Table 6 to the VDD\_LV and VDD\_HV\_IO\_JTAG supplies.

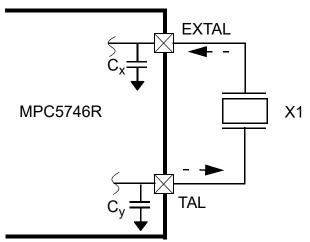

MPC5746R provides configurable internal load capacitors for the external crystal (Cx and Cy in Figure 9). This feature is intended to simplify the hardware design and reduce the overall system cost by eliminating external components and reducing the printed circuit board (PCB) footprint. If an 8 MHz–16 MHz crystal is used, as shown in Figure 10 external load capacitance must be connected. If the external crystal is to be started during power-up by hardware, the crystal frequency and the selected load capacitance must be specified in the UTEST Miscellaneous DCF Client records field. See the MPC5746R Reference Manual for details.

21

Figure 9. Internal Crystal Load Capacitors and Crystal Connections

Since the layout of the module/board can affect the component values required, customers should have their board characterized by their crystal vendor to recommend values for  $C_X$  and  $C_Y$ . The values shown in this document should be used as a starting point. These should be re-characterized for any change to the oscillator circuit layout, including routing changes of other circuitry near the crystal circuit.

The crystal should be placed as close as possible to the MCU. In order to minimize signal degradation, the circuitry should be placed entirely on only one PCB layer, avoiding unnecessary vias where ever possible. Do not allow any signals to cross the crystal connections to the device. Absolutely no high current or high speed signals should be run near any of the crystal components.

Other than the connections shown in the figure above, no other connections should be made to the crystal or EXTAL and XTAL device pins. Do not use XTAL to drive any other circuitry.

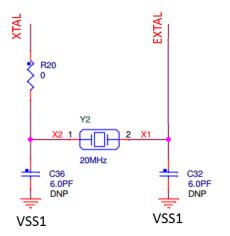

The following figure illustrates an example circuitry of oscillator with ground routing with external load capacitors.

Load capacitors of C36, C32 should be obtained by Crystal Manufacture. Crystal load Capacitors' GND and the Crystal guard pattern should connect to VSS1.

VSS1 should be connected to other VSS by one point.

Figure 10. External oscillator circuitry example

#### **Device Reset Configuration**

The recommendations from the crystal manufacturer will include not only a series resistor value but also the load capacitance required for the crystal (the total crystal load capacitance is usually specified in the crystal Data Sheet). Keep in mind that the load capacitance is the sum of the following:

- Physical capacitors ( $C_X$  and  $C_Y$ )

- Capacitance of the MCU

- Capacitive loading of the board (C<sub>PCB</sub>)

- Pin capacitance (C<sub>MCU PIN</sub>) of the MCU EXTAL and XTAL balls (BGA balls are specified as 7 pF maximum)

The requirement for the crystal vendor to measure the customer board is due to the board capacitance effect on the crystal load capacitors.

Generally, the method to calculate the capacitor values to use for C<sub>X</sub> and C<sub>Y</sub> is provided by the following formulas:

$$C_{A} = C_{B} = 2 \times C_{L}$$

$$C_{A} = C_{X} + C_{MCU\_PIN} + C_{BOARD}$$

$$C_{B} = C_{Y} + C_{MCU\_PIN} + C_{BOARD}$$

$C_{L}$  should come from the crystal specifications (requirements).  $C_{BOARD}$  should also include any socket capacitance if a socket is used.  $C_{MCU\ PIN}$  is listed in the MPC5746R Data Sheet as the discrete load capacitance to connect to EXTAL and XTAL.

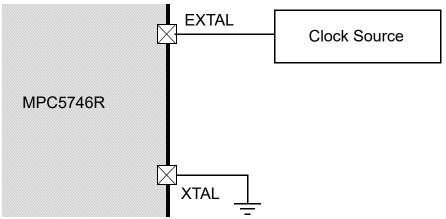

If an external clock is being used as clock reference to the MCU, then the XTAL pin should be connected to ground and the clock should be provided to EXTAL as shown in the figure below.

Figure 11. MPC5746R External Clock Connection

#### **Device Reset Configuration** 5

MPC5746R does not require external reset circuitry for device configuration. The device is configured during reset based on data in flash memory.

MPC5746R Hardware Design Guide, Rev. 1

### 5.1 External reset signals

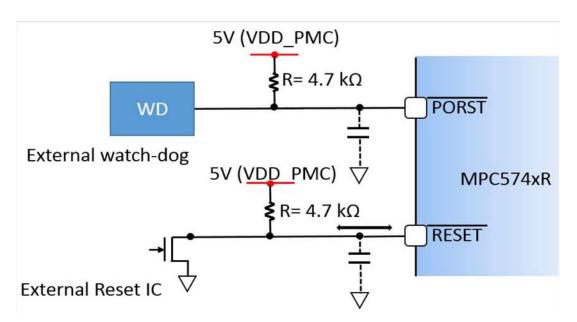

MPC5746R devices feature two external reset signals:

- Power-on reset ( $\overline{PORST}$ )

- External reset (RESET)

Both external reset signals are bidirectional and active-low.  $\overline{RESET}$  indicates whether the device is active (high signal) or in reset. It is in a weak pull-up state after the reset sequence has completed. An external 4.7 k $\Omega$  pull-up resistor on  $\overline{RESET}$  is required. A falling edge on this pin will trigger a functional reset to the Reset Generation Module (RGM). Holding this pin low will keep the device in the last phase of the reset sequence (Phase3[Functional]).

After reset,  $\overline{PORST}$  is configured as a weak pull-down for safety reasons. In case  $\overline{PORST}$  is disconnected the device will remain in reset.  $\overline{PORST}$  is released when the device leaves the power-up state of the RGM.  $\overline{PORST}$  must be forced high externally so the device will leave the reset state. The internal weak pull-down maximum current of  $\overline{PORST}$  is 100 uA. It is recommended that an external 4.7 k $\Omega$  pull-up resistor be used to ensure the  $\overline{PORST}$  voltage level remains safely above the threshold.

Figure 12 illustrates the typical system configuration of  $\overline{RESET}$  and  $\overline{PORST}$  pins with the external components.

Figure 12. example Circuitry for RESET & PORST pins

# 5.2 Reset Out (RSTOUT)

MPC5746R has an optional Reset out signal which can be used to notify external systems that the MCU has been reset. Pin PJ[5] can be configured to drive the reset out signal (RSTOUT) without generating the internal reset. RSTOUT will follow the RESET pin until reconfigured in software.

In a POR event RSTOUT is internally pull-up then actively drives low during reset PHASE3 and drives

high at the end of reset PHASE3. Please refer the MPC5746R Reference Manual for more information.

# 6 Input/Output Pins

The I/O pads are distributed across the I/O supply segments. Each I/O supply segment is associated with a VDD\_HV\_IO/VSS\_HV supply pair. In order to ensure device reliability, the total current of the I/O on a single segment should remain below the maximum current per segment value as defined in the data sheet.

If there is a need to source/sink current through some I/Os, care should be taken to spread the amount of current between the segments.

In the MPC5746R family, all of the I/Os have a weak pull up/down feature. In addition, input buffers and the weak-pulls are enabled for all I/Os by default. SD\_ADC analog input channels are only multiplexed with digital inputs.

# 6.1 I/O Pad Block Diagram (GPIO & Module Multiplexer Port)

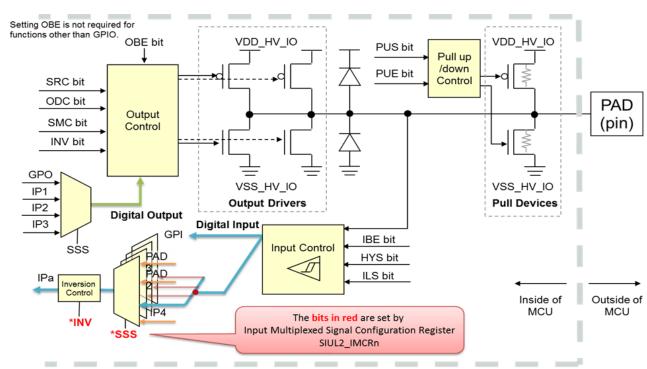

The following figure illustrates an I/O pad (without analog inputs) internal block diagram and the input/output multiplexer. This also illustrates the internal input/output control, pull-up/pull-down control and module selection. Please refer the system integration unit lite2 (SIUL2) chapter of the MPC5746R Reference Manual for more information

Note: This diagram shows a PAD with full functions. Some PADs do not have them all. Refer to RM for the details.

Note: This diagram shows a PAD with full functions. Some Pads do not implement all functions. Refer the MPC5746R reference manual for the details.

Figure 13. I/O pad block diagram without analog inputs

# 6.2 I/O Pad Block Diagram with analog input (GPIO & Module Multiplexer Port)

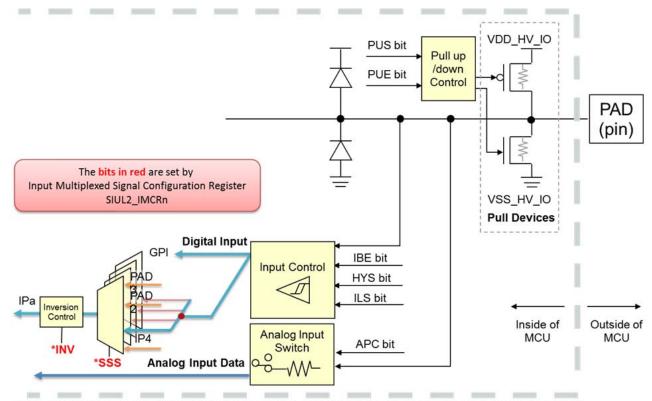

The figure below illustrates the I/O pad internal block diagram with analog inputs. This also illustrates the internal digital/analog input control, pull-up/pull-down control and module selection. Please refer to the system integration unit lite2 (SIUL2) chapter of the MPC5746R Reference Manual for more information.

Note: This diagram shows a PAD with full functions. Some PADs do not have them all. Refer to RM for the details.

Note: This diagram shows a PAD with full functions. Some Pads do not implement all functions. Refer the MPC5746R reference manual for the details.

Figure 14. I/O pad block diagram with analog inputs

#### 6.3 Unused GPIO Pin Termination

Most microcontrollers are designed to be used in a variety of applications and often a particular application does not use 100% of the MCU resources. To increase EMC performance, unused clocks, counters or I/Os, should never be left floating or unconnected.

Following table describes the termination options that the user should follow for the unused pins.

#### Table 13. Termination options for unused pins

- (1) External pull up or down

- (2) Direct connection to VDD source or GND.

- (3) Configure as input pin and enable internal weak pull up or down by software

- ( MSCR Register PUE=1 & PUS=1 or 0 )

- (4) Configure as output pin and set output to Low or High by software

- ( MSCR Register OBE=1 & GPDO Register PDO=1 or 0 )

- (5) No configuration (MSCR Register IBE=0 & OBE=0 as default)

| Pin Type                    | Termination | Note                                                                                                                       |

|-----------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------|

|                             | (1)         | Recommended. Benefit of this option is to ensure the termination during Power-On. But this option costs more.              |

| Pin which is                | (2)         | Take care for output collision toward external driver due to software mishandling.                                         |

| exposed to IO<br>pad on the | (3)         | Recommended. But take care for long wiring to external device without external pull up or down.                            |

| package.                    | (4)         | Recommended. Don't apply for input pin. Take care for output collision toward external driver due to software mishandling. |

|                             | (5)         |                                                                                                                            |

| Pin which is not            | (3)         | Recommended.                                                                                                               |

| exposed out of              | (4)         | Recommended. Don't apply for input pin.                                                                                    |

| the package                 | (5)         |                                                                                                                            |

#### 6.4 Injection Current

The following guidelines should be followed with respect to injection currents.

- Maximum injected input current on any pin during overload condition: +/-3 mA

- Note that the ADC input pad must never exceed its own IO segment supply voltage where the input

pad resides. If ADC input pin voltage is higher than IO supply where the pin resides, then this will

cause ESD diodes in pads to forward bias.

- Applying signals to pins (~3.3/5.0 V) during power-off (VDD ~0 V) must be considered as an over load condition. Series resistors between signal sources and pins may be needed to limit injection current I<sub>IC</sub>.

- In general, any over load conditions (positive or negative voltage out of the maximum VIH and the minimum VIL spec applied to the pins) should be avoided.

- Injection current may cause to increase the leakage current on the pins next to the injected pin.

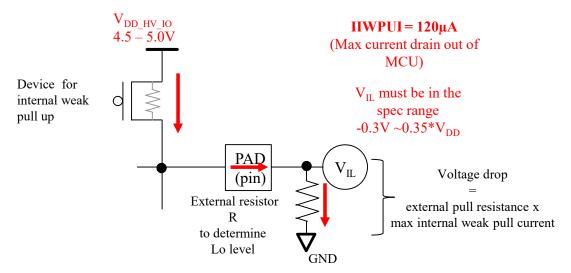

#### 6.5 Internal Weak Pull-Up/Down

The internal weak pull feature is used primarily for device protection. The maximum weak pull current specification is important when the application requires the internal weak pull up to oppose a voltage level caused by an external pull up/down resistor before software changes the internal weak pull configuration. Figure 15 shows an example configuration.

Figure 15. Example Weak pull up/down configuration.

Following example describes how to calculate a suitable pull-up resistor value based on data sheet specifications.

#### **Example:**

External resistor R= $4.7 \text{ k}\Omega$

120 uA max weak pull up current as specified in the data sheet when VDD\_HV\_IO >= 4.5 V.

Voltage drop ( $V_{IL}$ )= 4.7 k $\Omega$  x 120  $\mu$ A = 0.56 V

The voltage above pin is less than  $V_{IL}$  max= 0.35x4.5 V = 1.575 V at  $V_{DD}$ =4.5 V

Therefore  $R=4.7 \text{ k}\Omega$  is suitable.

The same principal applies for internal weak pull down scenarios.

# 7 Debug Options available

The MPC5746R production device (PD) supports a standard 14-pin JTAG connector. A development solution is provided by the 292BGA emulation device (ED). The ED supports a high-speed serial Nexus trace port that utilizes a Xilinx Aurora interface as the transport mechanism. The ED is mounted to a Trace Adapter that allows the customer to install it on production hardware for development support. This ED solution may be ordered through your NXP representative.

#### NOTE

It is possible that "keep-out" areas may be required by some debug tools. Consult the preferred debug tool vendor to determine any area that must remain clear around the debug connector. Also note that the ED solution may require a small keep out area on the customer PCB to accommodate the adapter and device. Refer to the drawings provided with the MPC5746R ED system.

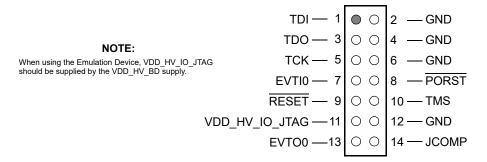

#### 7.1 MPC5746R JTAG connector

Figure 16 shows the pin-out of the recommended JTAG connector to support MPC5746R device. The recommended connector for the target system is Tyco part number 2514-6002UB.

Figure 16. JTAG Connections

# 7.2 MPC5746R high-speed Nexus serial trace connector

For high speed Nexus Aurora trace applications, the Samtec<sup>TM</sup> ERF8 Series connector is recommended in the IEEE-ISTO 5001<sup>TM</sup>-2012 standard. For the MPC57xx family, the 17 position (34 pins) connector is recommended. The part number of the Samtec connectors are shown in the following table.

| Connector | Part number (Samtec) | Style                                    | Description                   |

|-----------|----------------------|------------------------------------------|-------------------------------|

| HS34      | ASP-137973-01        | Samtec ERF8 Series, 17 position by 2 row | Vertical mount for MCU module |

| HS34      | ASP-177706-02        | Samtec ERF8 Series, 17                   | Right Angle mount for MCU     |

**Table 14.** Recommended high-speed serial trace connector part numbers

MPC5746R Hardware Design Guide, Rev. 1

The Samtec ERF8 series of connectors is intended for high speed applications requiring a minimum footprint size with a reliable, latching connection. The recommended connector has two rows of seventeen contacts each with a spacing of 0.8 mm. The connector provides isolation between the high-speed trace signals and the low-speed JTAG and control signals. It also provides ample ground connections to ensure signal integrity. If at all possible, the connector should be placed onto the target system with the even numbered pins nearest the edge of the printed circuit board. Figure is courtesy of Samtec U.S.A (http://www.samtec.com/search/NEXUS.aspx).

Figure 17. Recommended Nexus connector

Table 15 shows the recommended pin-out for Samtec connector.

Table 15. MPC5746R high-speed serial trace connector

| Function            | Pin No | Pin No | Function |

|---------------------|--------|--------|----------|

| VSS                 | GND    | GND    | VSS      |

| TX0+                | 1      | 2      | VREF     |

| TX0-                | 3      | 4      | TCK/TCKC |

| VSS                 | 5      | 6      | TMS/TMSC |

| TX1+                | 7      | 8      | TDI      |

| TX1-                | 9      | 10     | TDO      |

| VSS                 | 11     | 12     | JCOMP    |

| TX2+                | 13     | 14     | EVTI1    |

| TX2-                | 15     | 16     | EVTI0    |

| VSS                 | 17     | 18     | EVTO0    |

| TX3+                | 19     | 20     | PORST    |

| TX3-                | 21     | 22     | RESET    |

| VSS                 | 23     | 24     | VSS      |

| (TX4+) <sup>1</sup> | 25     | 26     | CLK+     |

| (TX4-) <sup>1</sup> | 27     | 28     | CLK-     |

$(TX5-)^{1}$

**VSS**

| Function            | Pin No | Pin No | Function |

|---------------------|--------|--------|----------|

| VSS                 | 29     | 30     | VSS      |

| (TX5+) <sup>1</sup> | 31     | 32     | EVTO1    |

34

**GND**

N/C or WDT

**VSS**

Table 15. MPC5746R high-speed serial trace connector

33

**GND**

It is recommended that the "even" side of the connector be mounted closer to the edge of the printed circuit board to facilitate a direct connection to the tool.

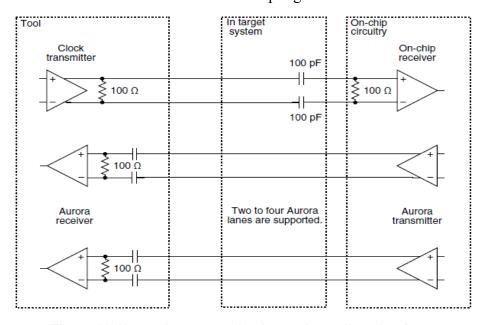

### 7.3 Nexus Aurora Target System Requirements

The Nexus Aurora interface requires termination and AC coupling of the signals between the target system and the tool. The termination resistor for the Aurora clock is located inside the MCU. An external termination resistor is required. The transmit termination resistor must be implemented in the target system; however, it may be implemented internally to the FPGA of the tool.

Figure 18 illustrates the nexus aurora termination and coupling circuit between the tool and the MCU.

Figure 18. Nexus Aurora termination and coupling circuits

#### 7.4 External circuitry

Additional resistor pull-ups/pull-downs may be required for the JTAG debug circuitry. The MPC5746R device includes internal pull devices that ensure the pins remain in a safe state; however, if there is additional circuitry connected to the JTAG pins, or long traces that could be affected by other signals (due

TX4-, TX4+, TX5-, and TX5+ these pins are not used on this device.

to crosstalk from high-current or high-speed signals), optional external pull resistors as shown in Table 16 can be added to ensure proper operation under all conditions.

Table 16. Optional External Pull Ups/Pull Downs

| JTAG Signal      | Component                  | Description                                                                                                                                                                                                                                                        |

|------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JCOMP            | 10 kΩ pull-down resistor   | Holds debug port in reset and prevents any debug commands from interfering with the normal operation of the MCU.                                                                                                                                                   |

| PORST            | 4.7 kΩ pull-up resistor    | The PORST input should be driven from an open collector output; therefore, it requires a pull-up resistor for the MCU.                                                                                                                                             |

| RESET            | 4.7 kΩ pull-up resistor    | The RESET input should be driven from an open collector output; therefore, it requires a pull-up resistor for the MCU.                                                                                                                                             |

| EVTI             | 10 kΩ pull-up resistor     | A pull-up resistor prevents debug mode from being forced after reset if debug mode is enabled (JCOMP = high). It also prevents breakpoints from being forced if debug mode is enabled.  NOTE: In almost all situations, a resistor is not required on this signal. |

| TCK <sup>1</sup> | series 0 $\Omega$ resistor | A series resistor may be required on TCK to allow the TCK signal in the target system to be disconnected for signal integrity if TCK is connected to multiple connectors.                                                                                          |

<sup>&</sup>lt;sup>1</sup> TCK isolation may be required if using both a JTAG connector and a Nexus Aurora trace connector in the target system to reduce reflections. Selection of TCK to either connector should be supported. On the NXP Trace Adapter board, by default, the debug connectors signals are not connected to the target system and are already isolated.

In addition to the pull-up and pull-down resistors, some systems may want to use buffers between the JTAG connector inputs (JCOMP, TDI, TDO, TMS, EVTI, EVTO, PORST and RESET) and the MCU. This will prevent over-voltage conditions from causing damage to the MCU pins. Normal systems should not require this circuitry, but it is helpful in systems that can be exposed to improper connections that provide voltages that are outside the operating conditions of the MCU. A common circuit for this application is the Texas Instruments SN74CBTLV38615. This device is a bus switch that implements a bidirectional interface between two terminals with less than 5  $\Omega$  of resistance. It should be powered by the same supply that powers the debug port. The device enable pin should be connected to ground for the interface to be enabled whenever the debug port on the MCU is powered. This circuit provides a high impedance to the tool when the debug port is powered off.

MPC5746R Hardware Design Guide, Rev. 1 **NXP Semiconductors** 31

#### **Emulation device** 8

The emulation device (ED) is a multi-die MCU that adds additional functionality for calibration and debug during the ECU development. The ED consists of the production die (PD) and a buddy die (BD). The BD JTAG interface replaces the JTAG interface of the PD, but allows access to the PD JTAG interface by passing control from the BD JTAG interface to the PD JTAG interface. Please refer the MPC5746R Reference Manual and AN5181: "Introduction to the MPC5746R Trace Adapter" application note for more information.

It is recommended that customers use the NXP Trace Adapter (TA) for development systems. The TA allows development features with a production ECU board layout. TA solutions are described in Section 8.2. and available at www.NXP.com.

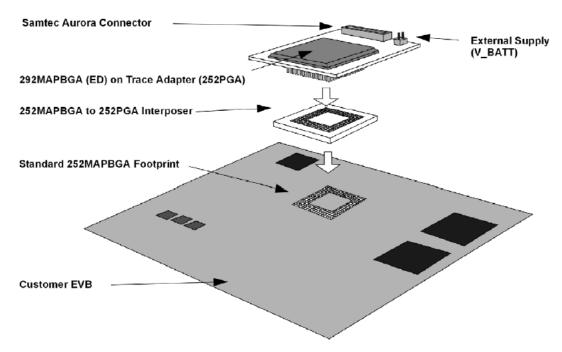

Figure 19 illustrates the LFDBGK46RT4S2A adapter card for MPC5746R 292-pin BGA ED with Aurora interface.

Figure 19. 292 BGA to 252 PGA Adapter card for Emulation and Debug Device

#### 8.1 **Emulation device power sequencing**

The power supplies to the ED can be sequenced in any of the following orders.

- Power the BD first with 12 V external supply

- Power the PD second

- Or power both BD and PD at same time

#### 8.2 **Available ED Trace Adapters**

There are two Trace adapters available 1) 292 BGA to 252 PGA and 2) 292 BGA to 208 PGA. The 208 PGA is used to support both 176 LQFP device and the 144 LQFP device. Another adapter is required to adopt the 208 PGA to either the 176 LQFP footprint or the 144 LQFP footprint. Refer to Table 17 for adapter card part numbers.

MPC5746R Hardware Design Guide, Rev. 1 32 NXP Semiconductors

|  | Table 17. | MPC574xR | <b>ED Ada</b> | pter ( | Card ty | pes |

|--|-----------|----------|---------------|--------|---------|-----|

|--|-----------|----------|---------------|--------|---------|-----|

| Pin conversion    | Part Number                   | Description                                                                                                                                             |

|-------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 292BGA to 252PGA  | LFDBGK46RT4S2A                | 292 PIN 0.8MM BGA to 252 0.8MM PGA Adapter with Aurora interface for MPC574xR                                                                           |

| 292BGA to 176LQFP | LFDBGK46RT4QA<br>LFTAK46MQM2A | 292 PIN 0.8MM BGA to 208 1.0MM PGA Adapter with Aurora interface for MPC574xR. 208 pin 1.0mm PGA to 176 pin 0.5mm QFP target Adapter board for MPC574xR |

| 292BGA to 144LQFP | LFDBGK46RT4QA                 | 292 PIN 0.8MM BGA to 208 1.0MM PGA Adapter with Aurora interface for MPC574xR.                                                                          |

|                   | LFTAK46MQLA                   | 208 pin 1.0mm PGA to 144 pin 0.5mm QFP target Adapter board for MPC574xR                                                                                |

Refer the following illustration for 292 MAPBGA package mapped into a 252BGA footprint.

Figure 20. 292MAPBGApackage into a 252BGA footprint

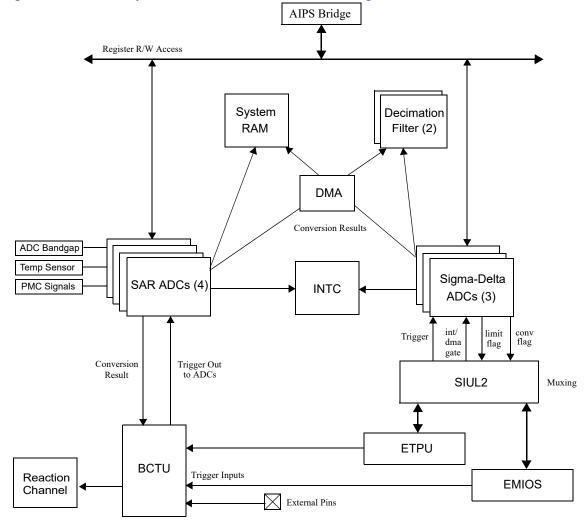

# 9 ADC and Analog

#### 9.1 Overview

MPC5746R includes seven separate Analog-to-Digital converters (ADC) and associated support modules:

- Four independent 12-bit Successive-Approximation-Register (SAR) ADCs

- Three independent 16-bit Sigma-Delta (SD) ADCs

- Two Decimation Filter blocks

- ADC Cross-Triggering Unit (BCTU)

These ADCs interface a various number of analog input pins depending on whether the 252 MAPBGA, the 176 LQFP package, or the 144 LQFP package is selected for the design. Both the SAR and SD ADCs have their own power supply and references. Please refer to the Power Supply section for information on how to connect these signals and for specific details of the analog pins available in each package.

A diagram of the ADC system in MPC5746R is shown in Figure 21.

Figure 21. MPC5746R ADC Subsystem

MPC5746R Hardware Design Guide, Rev. 1

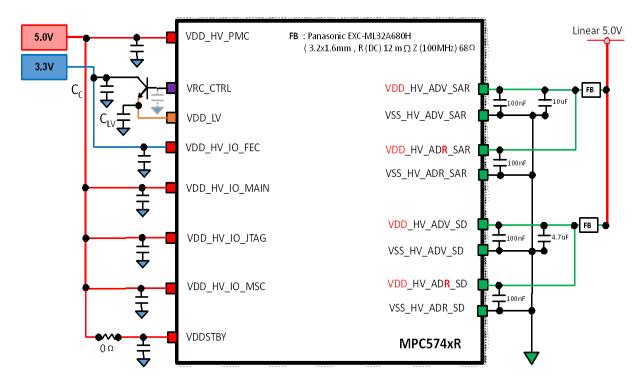

# 9.2 Analog supply configuration

The following diagram illustrates the full SD/SAR ADC supply configuration with external components.

Figure 22. SD/SAR ADC supply configuration

Ferrite beads are used to isolate noise induced from the digital supply domain. Each pair of ADC supplies must have a 100 nF filtering capacitor and should be populated at the pin. NXP recommends a separate linear stable supply for the ADC analog domain to avoid noises from digital supply domain.

The following board schematic and layout guidelines should be followed:

- Isolate the analog power supplies (VDDA) from digital power supplies (see Analog supply configuration)

- Isolate analog traces from digital high-frequency traces

- Incorporate robust bypassing of power supplies (analog and digital supplies) to ensure lowest possible voltage ripple on the power supplies

- Use linear power supplies when possible, or minimize or isolate the switching noise when using a switching power supply

- Incorporate low-pass filter on ADC inputs to remove unwanted higher frequency components as shown in the following sections

User can select either 3.3 V or 5 V for the SD/SAR ADC reference supply. Refer to the MPC5746R Data Sheet for ADC characteristics with different reference supply.

**ADC** and Analog

#### 9.3 SAR ADC

This section describes the various features and configurations of the SAR ADC. Refer to "AN4881 - SAR ADC Implementation and Use", "AN5032 - Ref Circuit Design for SAR ADC" (available at www.nxp.com) and the MPC5746R Reference Manual for additional information.

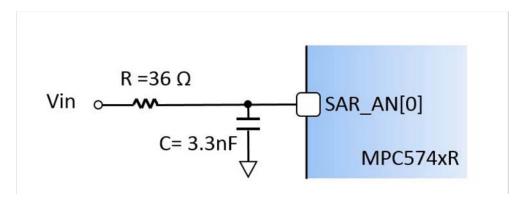

#### 9.3.1 External circuitry for SAR ADC analog input

Figure 23 shows the typical circuitry for the analog input channel with filtering components. NXP recommends checking the ADC performance on silicon to get optimal R and C values. The SAR ADC supports a maximum sampling frequency of 1 MHz (total conversion time of 1us). The maximum allowed input frequency is 125 kHz. Refer to the MPC5746R Data Sheet for additional information on internal circuitry, minimum sample time and minimum conversion time etc.

Figure 23. SAR ADC external circuitry example

# 9.3.2 Input Multiplexing

SAR ADC3 supports 4 external multiplexers, with 8 inputs each. None of the other ADCs support external multiplexers. Table 18 provides the address mapping for the SAR ADC3 multiplexed channels.

| Channel | External Mux Input | External Mux Address (binary) |

|---------|--------------------|-------------------------------|

| 64      |                    | 000                           |

| 65      |                    | 001                           |

| 66      |                    | 010                           |

| 67      | PX[5]              | 011                           |

| 68      |                    | 100                           |

| 69      |                    | 101                           |

| 70      |                    | 110                           |

| 71      |                    | 111                           |

Table 18. Channel and External Mux Mapping

MPC5746R Hardware Design Guide, Rev. 1

Table 18. Channel and External Mux Mapping

| Channel | External Mux Input | External Mux Address (binary) |

|---------|--------------------|-------------------------------|

| 72      |                    | 000                           |

| 73      |                    | 001                           |

| 74      |                    | 010                           |

| 75      | DVICI              | 011                           |

| 76      | - PX[6]            | 100                           |

| 77      |                    | 101                           |

| 78      |                    | 110                           |

| 79      |                    | 111                           |

| 80      |                    | 000                           |

| 81      |                    | 001                           |

| 82      |                    | 010                           |

| 83      | DVIZI              | 011                           |

| 84      | PX[7]              | 100                           |

| 85      |                    | 101                           |

| 86      |                    | 110                           |

| 87      |                    | 111                           |

| 88      |                    | 000                           |

| 89      |                    | 001                           |

| 90      | 1                  | 010                           |

| 91      | DVIO               | 011                           |

| 92      | - PX[8]            | 100                           |

| 93      |                    | 101                           |

| 94      |                    | 110                           |

| 95      |                    | 111                           |

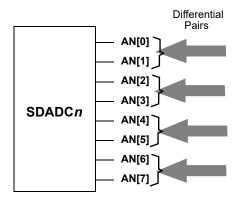

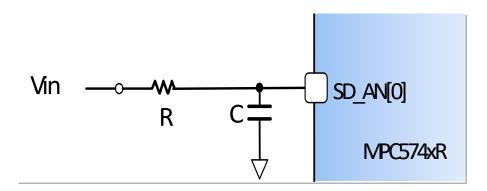

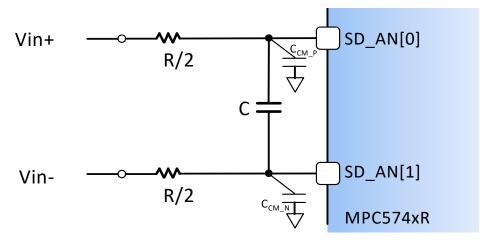

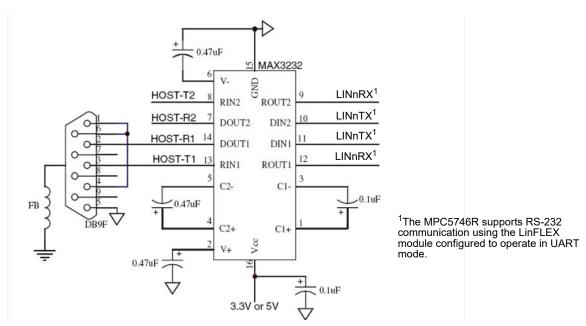

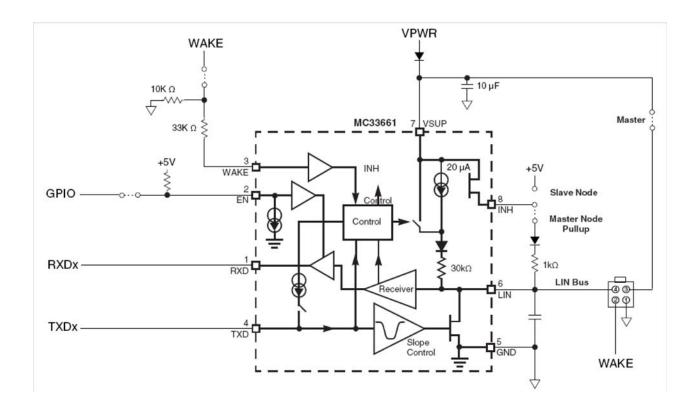

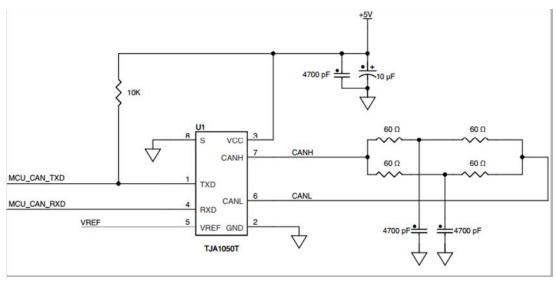

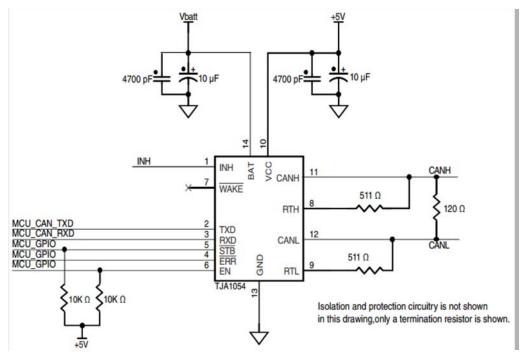

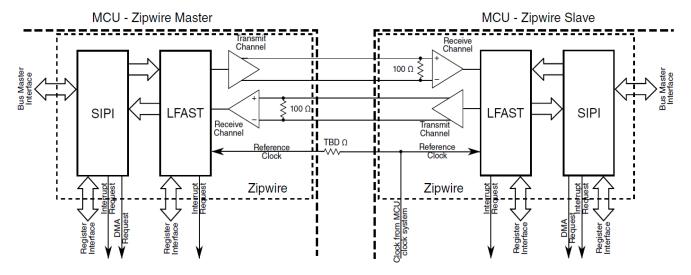

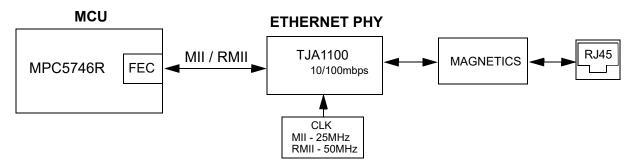

# 9.4 Sigma Delta ADC