# Freescale Semiconductor Application Note

Document Number: AN4347 Rev. 0, 08/2011

# Transitioning Applications from S08AC and S08FL Family to S08PT Family

by: Systems and Applications

Asia Pacific

Microcontroller Solutions Group

Freescale's S08PT family has the first S08 MCUs that employ the 0.18 micron process, a new version of the S08 CPU, and a new 5 V pad. This family also introduces many new features for different peripheral modules. With these new features, the S08PT family has lower power consumption, better transient protection, and better performance.

This application note outlines the product family differences between S08AC/FL and S08PT families, and provides recommendations for code conversion.

# 1 Flash and EEPROM

The flash memory is ideal for single-supply applications, allowing for field reprogramming that does not require external high voltage sources for program or erase operations.

The S08PT family has both flash and EEPROM memory. Flash memory size is device-dependent with a maximum size of 64 KB. The EEPROM memory is 256 bytes. This

#### **Contents**

| 1  | Flas | h and EEPROM 1                    |

|----|------|-----------------------------------|

|    | 1.1  | Protection                        |

|    | 1.2  | Commands                          |

|    | 1.3  | ECC parity check                  |

| 2  | Cloc | k gating13                        |

| 3  | Inte | rupt Priority Controller          |

| 4  | S08  | CPU V6                            |

| 5  | Enh  | anced code debug16                |

| 6  | Pinc | out changes                       |

| 7  | Para | allel I/O structure               |

| 8  | Safe | ety feature enhancements          |

|    | 8.1  | Watchdog timer                    |

|    | 8.2  | Cyclic redundancy check26         |

| 9  | Flex | Timer versus TPM29                |

|    | 9.1  | FTM clock source                  |

|    | 9.2  | TPM-compatible functions31        |

|    | 9.3  | FTM-specific functions            |

| 10 | TSI  | addition                          |

|    | 10.1 | TSI function description45        |

|    |      | TSI applications                  |

| 11 | RTC  | and MTIM additions48              |

|    | 11.1 | Real time counter                 |

|    |      | Modulo timer                      |

| 12 |      | oit SPI with queue addition       |

| 13 |      | log-to-Digital Converter (ADC) 55 |

| 14 |      | erences                           |

| 15 | Glos | ssary                             |

|    |      |                                   |

## Flash and EEPROM

family provides a security mechanism similar to that found in the S08AC and S08FL families, to prevent unauthorized access to the flash memory and EEPROM. Unsecuring the flash and EEPROM memory can also be done in similar way via Backdoor Key access, then an Erase All Blocks command (similar to Mass Erase of S08AC/FL families).

The S08PT family supports simultaneous flash and EEPROM operations. It is possible to read from flash memory while some commands are executing on EEPROM memory. However, it is not possible to read from EEPROM memory while a command such as Erase and Program is executing on flash memory.

The EEPROM memory is implemented with Error Correction Codes (ECC) that can resolve single-bit faults and detect double-bit faults, providing the best safety features among all three families.

An erase operation is performed on a sector base on devices in the S08PT family, which is similar to a page on devices in the S08AC/FL families. Each flash sector contains 512 bytes. Each EEPROM sector consists of two bytes. Therefore, the flash memory has up to 128 sectors, while EEPROM has 128 sectors.

## Flash memory has these features:

- Automated program and erase algorithm with verify

- Fast sector erase and longword (32-bit) program operation

- Ability to read flash memory while programming a byte in EEPROM memory

- Flexible protection scheme to prevent accidental program or erase of flash memory

- Ability to set flash read margin levels

## EEPROM memory has these features:

- Single-bit fault correction and double-bit fault detection within a word during read operations

- Automated program and erase algorithm with verification and generation of ECC parity bits

- Fast sector erase and byte program operation

- Protection scheme to prevent accidental program or erase of EEPROM memory

- Ability to program up to four bytes in a burst sequence

- Ability to set EEPROM read margin levels

Table 1 compares flash and EEPROM features among the S08AC/FL/PT families:

Table 1. Flash and EEPROM comparision

| Features               | S08AC | S08FL | S08PT                                                                       | Unit          |

|------------------------|-------|-------|-----------------------------------------------------------------------------|---------------|

| Flash security         |       |       |                                                                             |               |

| Flash protection       |       |       |                                                                             |               |

| EEPROM                 | X     | Х     | 256                                                                         | Bytes         |

| Flash size             | 128K  | 16K   | 64K                                                                         | Bytes maximum |

| Flash sector/page size | 512   | 512   | 512                                                                         | Bytes         |

| ECC parity check       | Х     | х     | Single fault bit resolve<br>&<br>Double fault bit<br>detection on<br>EEPROM |               |

| Table 1. Flash and | <b>EEPROM</b> com | parision ( | (continued) |

|--------------------|-------------------|------------|-------------|

|                    |                   |            |             |

| Features                        | S08AC                                 | S08FL                                 | S08PT                           | Unit          |

|---------------------------------|---------------------------------------|---------------------------------------|---------------------------------|---------------|

| Flash clock<br>frequency (FCLK) | 150k to 200K                          | 150k to 200K                          | 0.8M to 1M                      | Hz            |

| Flash program bytes             | 1                                     | 1                                     | 8                               | Bytes maximum |

| EEPROM program bytes            | Х                                     | Х                                     | 4                               | Bytes maximum |

| Access time/byte read           | 1                                     | 1                                     | 1                               | Bus cycles    |

| Program time                    | 9 (byte program)<br>4 (burst program) | 9 (byte program)<br>4 (burst program) | ~68 (2 words)<br>~122 (4 words) | FCLK cycles   |

| Page Erase time                 | 4000                                  | 4000                                  | ~20015                          | FCLK cycles   |

| Mass erase time                 | 20,000                                | 20000                                 | ~100066                         | FCLK cycles   |

## 1.1 Protection

Flash protection is performed on three separate memory regions in the flash memory: one that starts at global address 0x8000 and extends upward (low range), one that starts at global address 0xFFFF and extends downward (high range), and the remaining memory region. The protected address region can only be increased, not reduced, once it is implemented.

Flash protection and unprotection features are controlled via NVM\_FPROT register bits, as listed in Table 2, Table 3, and Table 4.

Table 2. Flash protection function

| FPOPEN | FPHDIS | FPLDIS | Function                          |

|--------|--------|--------|-----------------------------------|

| 1      | 1      | 1      | No flash protection               |

| 1      | 1      | 0      | Protect low range                 |

| 1      | 0      | 1      | Protect high range                |

| 1      | 0      | 0      | Protect both low and high range   |

| 0      | 1      | 1      | Protect full flash memory         |

| 0      | 1      | 0      | Unprotect low range               |

| 0      | 0      | 1      | Unprotect high range              |

| 0      | 0      | 0      | Unprotect both high and low range |

#### Flash and EEPROM

Table 3. Flash protection high range

| FPHS[1:0] | Global address range | Protected size |

|-----------|----------------------|----------------|

| 00        | 0xF800—0xFFFF        | 2 KB           |

| 01        | 0xF000—0xFFFF        | 4 KB           |

| 10        | 0xE000—0xFFFF        | 8 KB           |

| 11        | 0xC000—0xFFFF        | 16 KB          |

Table 4. Flash protection low range

| FPLS[1:0] Global Address Range |               | Protected size |

|--------------------------------|---------------|----------------|

| 00                             | 0x8000—0x83FF | 1 KB           |

| 01                             | 0x8000—0x87FF | 2 KB           |

| 10                             | 0x8000—0x8FFF | 4 KB           |

| 11                             | 0x8000—0x9FFF | 8 KB           |

Figure 1 shows seven different protection schemes.

Figure 1. Flash protection schemes

Transitioning Applications from S08AC and S08FL Family to S08PT Family, Rev. 0

Table 5 specifies all valid transitions between flash protection scenarios:

| From                    | To protection scenario# |   |   |   |   |   |   |   |

|-------------------------|-------------------------|---|---|---|---|---|---|---|

| protection<br>scenario# | 0                       | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 0                       | Х                       | Х | Х | Х |   |   |   |   |

| 1                       |                         | Х |   | Х |   |   |   |   |

| 2                       |                         |   | Х | Х |   |   |   |   |

| 3                       |                         |   |   | Х |   |   |   |   |

| 4                       |                         |   |   | Х | Х |   |   |   |

| 5                       |                         |   | Х | Х | Х | Х |   |   |

| 6                       |                         | Х |   | Х | Х |   | Х |   |

| 7                       | Х                       | Х | Х | Х | Х | Х | Х | Х |

EEPROM protection is controlled by NVM\_EEPROT register bits. The protected region can only be increased, not reduced, once it is implemented. The NVM\_EEPROT[DPOPEN] bit enables or disables the EEPROM protection. NVM EEPROT[DPS2:0] bits define the protected address range as in Table 6.

Table 6. EEPROM protection address range

| DPS[2:0]                                                                                                | Global address range | Protected size (bytes) |  |  |

|---------------------------------------------------------------------------------------------------------|----------------------|------------------------|--|--|

| 000                                                                                                     | 0x0_3100—0x0_311F    | 32                     |  |  |

| 001                                                                                                     | 0x0_3100—0x0_313F    | 64                     |  |  |

| 010                                                                                                     | 0x0_3100—0x0_315F    | 96                     |  |  |

| 011                                                                                                     | 0x0_3100—0x0_317F    | 128                    |  |  |

| 100                                                                                                     | 0x0_3100—0x0_319F    | 160                    |  |  |

| 101                                                                                                     | 0x0_3100—0x031BF     | 192                    |  |  |

| The protection size continues to increase in increments of 32 bytes for each DPS value increase of one. |                      |                        |  |  |

| 111                                                                                                     | 0x0_3100—0x0_31FF    | 256                    |  |  |

## 1.2 Commands

The flash memory module includes a memory controller that executes commands to modify flash memory contents. The user interface to the memory controller consists of the indexed Flash Common Command Object (NVM\_FCCOB) register which is written to with the command, global memory address, data, and any required command parameters. The memory controller must complete the execution of a command before the FCCOB register can be written to with a new command. The 16-bit NVM\_FCCOB register includes the high-byte NVM\_FCCOBHI and the low-byte NVM\_FCCOBLO. When the flash command is completed and/or the flash error is detected, it will generate the corresponding interrupt, if enabled.

Transitioning Applications from S08AC and S08FL Family to S08PT Family, Rev. 0

#### Flash and EEPROM

Table 7 shows the general command parameter format in NVM\_FCCOB and the corresponding parameter index in NVM FCCOBIX.

Table 7. General command parameter format in FCCOB

| NVM FCCOBIX[2:0]   | FCCOB register meaning (the least significant bits are at the right side and most significant bits must be filled 0 if not used) |                             |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--|--|

| NVIM_1 COODIX[2.0] | High byte                                                                                                                        | Low byte                    |  |  |

|                    | NVM_FCCOBHI                                                                                                                      | NVM_FCCOBLO                 |  |  |

| 000                | Flash command code(FCMD)                                                                                                         | memory address bits[17: 16] |  |  |

| 001                | memory address bits[15 : 8]                                                                                                      | memory address bits[7 : 0]  |  |  |

| 010                | Data0 bits[15:8]                                                                                                                 | Data0 bits[7:0]             |  |  |

| 011                | Data1 bits[15:8]                                                                                                                 | Data1 bits[7:0]             |  |  |

| 100                | Data2 bits[15:8]                                                                                                                 | Data2 bits[7:0]             |  |  |

| 101                | Data3 bits[15:8]                                                                                                                 | Data3 bits[7:0]             |  |  |

The command write sequence contains five steps:

- 1. Wait for the previous command to be completed, that is,  $NVM_FSTAT[CCIF] == 1$ .

- 2. Configure the flash clock to be 1 MHz by writing NVM FCLKDIV, if it is not configured.

- 3. Check NVM\_FSTAT[ACCERR] and NVM\_FSTAT[FPVIOL] bits. Clear these bits if they are set by writing 0x30 to NVM\_FSTAT.

- 4. Write the desired flash/EEPROM command and all the related parameters to NVM\_FCCOB indexed by NVM\_FCCOBIX[2:0] (the recommended write sequence is in ascending order of the command parameter format).

- 5. Launch the command by writing 0x80 to NVM\_FSTAT to clear the NVM\_FSTAT[CCIF] flag.

There are twelve commands for flash operation and nine commands for EEPROM operation, as shown in Table 8.

## Table 8. Flash operation commands

| Commands                   | Flash | EEPROM | Function Description                                                                                                                                  |

|----------------------------|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Erase verify all blocks    | Y     | Y      | Verify that all blocks including flash and EEPROM are erased.                                                                                         |

| Erase verify block         | Y     | Y      | Verify that the flash block or EEPROM block is erased.                                                                                                |

| Erase verify flash section | Y     | _      | Verify that a given number of words in the flash are erased.                                                                                          |

| Read Once                  | Y     | _      | Read a dedicated 64 B field in the nonvolatile information register of the flash block that was previously programmed using the program once command. |

| Program Once               | Y     | -      | Program a dedicated 64 B field in the nonvolatile information register of the flash block.                                                            |

| Program flash              | Y     | _      | Program up to two longwords in the flash block.                                                                                                       |

| Erase all blocks           | Y     | Y      | Erase all flash and EEPROM blocks.                                                                                                                    |

| Erase block                | Y     | Y      | Erase a flash block or EEPROM block.                                                                                                                  |

| Erase flash sector         | Υ     | _      | Erase a flash sector.                                                                                                                                 |

| Unsecure flash             | Y     | Y      | Supports a method of releasing MCU security by erasing all flash and EEPROM blocks and verifying that all flash and EEPROM blocks are erased.         |

| Verify backdoor access key | Υ     | _      | Supports a method of releasing MCU security by verifying a set of security keys.                                                                      |

## Flash and EEPROM

Table 8. Flash operation commands (continued)

| Commands                    | Flash | EEPROM | Function Description                                                  |

|-----------------------------|-------|--------|-----------------------------------------------------------------------|

| Set user margin level       | Y     | Y      | Specify a user margin read level for the flash block or EEPROM block. |

| Erase verify EEPROM section | _     | Y      | Verify that a given number of bytes in EEPROM provided are erased.    |

| Program EEPROM              | _     | Y      | Program up to four bytes in the EEPROM block.                         |

| Erase EEPROM sector         | _     | Y      | Erase all bytes in a sector of the EEPROM block.                      |

The following sections describe some typical commands. For a full list of valid commands, please refer to Freescale document MC9S08PT60RM, MC9S08PT60 Microcontroller Reference Manual.

## 1.2.1 Erase flash/EEPROM

The commands in this group are:

- Erase Flash Sector

- Erase Flash Block

- Erase All Blocks

- Erase EEPROM Sector

The Erase Flash Sector command will erase all memory units in the specified flash sector, while the Erase Flash Block command will bulk-erase the entire flash memory space. The Erase All Blocks command will bulk-erase the entire flash memory space as well as the whole EEPROM memory space.

The Erase Flash/EEPROM Sector command is similar to the page erase command in the S08AC/FL families. The Erase Flash Block command and Erase All Blocks command are similar to the mass-erase command in S08AC/FL families.

The following code snippet shows how to erase a flash sector at address 0x8684:

```

// Write index to specify the command code to be loaded

NVM_FCCOBIX = 0x0;

// Write command code and memory address bits[17:16]

NVM_FCCOBHI = 0x0A;// Erase flash sector command

NVM_FCCOBLO = 0;// memory address bits[17:16]

// Write index to specify the memory address bits[15:0] to be loaded

NVM_FCCOBIX = 0x1;

// Write the desired memory address bits[15:0] in the flash sector to be erased

NVM_FCCOB = 0x8684;

// Launch program command

NVM_FSTAT = 0x80;

// Wait till command is completed

While (!(NVM_FSTAT & NVM_FSTAT_CCIF_MASK));

```

Transitioning Applications from S08AC and S08FL Family to S08PT Family, Rev. 0

The following code snippet shows how to erase an EEPROM sector at address 0x3100:

```

// Write index to specify the command code to be loaded

NVM_FCCOBIX = 0x0;

// Write command code and memory address bits[17:16]

NVM_FCCOBHI = 0x12;// Erase EEPROM sector command

NVM_FCCOBLO = 0;// memory address bits[17:16]

// Write index to specify the memory address bits[15:0] to be loaded

NVM_FCCOBIX = 0x1;

// Write the desired memory address bits[15:0] in the EEPROM sector to be erased

NVM_FCCOB = 0x3100;

// Launch program command

NVM_FSTAT = 0x80;

// Wait till command is completed

While (!(NVM FSTAT & NVM FSTAT CCIF MASK));

```

## 1.2.2 Program flash/EEPROM

The Program Flash command will program up to two previously erased longwords in the flash memory, using an embedded algorithm. The memory locations to be programmed must be a longword or two longwords and their addresses must be aligned to a longword (4 B) boundary, that is, the lower two memory address bits [1:0] must be zero. The command code for Program Flash is 0x06.

The following code snippet shows how to program a longword 0x55667788 at 0x8684 in flash memory:

```

// Write index to specify the command code to be loaded

NVM FCCOBIX = 0 \times 0;

// Write command code and memory address bits[17:16]

NVM FCCOBHI = 0x06;// program flash command

NVM FCCOBLO = 0;// memory address bits[17:16]

// Write index to specify the longword memory address bits[15:0] to be loaded

NVM FCCOBIX = 0x1;

// Write the longword memory address bits[15:0]

NVM FCCOB = 0x8684;

// Write index to specify the word0 of the longword to be programmed

NVM FCCOBIX = 0x2;

// Write the word 0 of the longword

NVM FCCOB = 0x7788;

// Write index to specify the wordl of the longword to be programmed

NVM FCCOBIX = 0x3;

// Write the word 1 of the longword

NVM FCCOB = 0x5566;

// Launch the command

NVM FSTAT = 0x80;

// Wait till command is completed

While (!(NVM FSTAT & NVM FSTAT CCIF MASK));

```

The following code snippet shows how to program a 4-byte 0x55667788 at address 0x3100 in EEPROM memory:

```

// Write index to specify the command code to be loaded NVM_FCCOBIX = 0x0; // Write command code and memory address bits[17:16]

```

Transitioning Applications from S08AC and S08FL Family to S08PT Family, Rev. 0

#### Flash and EEPROM

```

NVM FCCOBHI = 0x11;// program EEPROM command

NVM FCCOBLO = 0;// memory address bits[17:16]

// Write index to specify the lower byte memory address bits[15:0] to be loaded

NVM FCCOBIX = 0x1;

// Write the lower byte memory address bits[15:0]

NVM FCCOB = 0 \times 3100;

// Write index to specify the byte0 to be programmed

NVM FCCOBIX = 0x2;

// Write the byte 0

NVM FCCOBLO = 0x88;

// Write index to specify the bytel to be programmed

NVM FCCOBIX = 0x3;

// Write the byte 1

NVM FCCOBLO = 0x77;

// Write index to specify the byte2 to be programmed

NVM FCCOBIX = 0x4;

// Write the byte 2

NVM FCCOBLO = 0x66;

// Write index to specify the byte3 to be programmed

NVM FCCOBIX = 0x5;

// Write the byte 3

NVM FCCOBLO = 0x55;

// Launch the command

NVM FSTAT = 0x80;

// Wait till command is completed

While (!(NVM FSTAT & NVM FSTAT CCIF MASK));

```

# 1.2.3 Program Once and Read Once commands

The Program Once and Read Once commands are used to access a reserved 64 B (8 phrases) field in the nonvolatile information register (IFR) in the flash block. This reserved field cannot be erased and can be used to store the product ID or any other information that can only be written once. So, the Program Once command can only be used once.

The following code snippet shows how to program and read the second eight bytes, 0x1122334455667788, in the reserved 64 B field of IFR:

```

// Write index to specify the command code to be loaded

NVM FCCOBIX = 0 \times 0;

// Write command code and memory address bits[17:16]

NVM FCCOBHI = 0x7;// program once command

// Write index to specify one of the 8 phrases in the reserved area once field

NVM FCCOBIX = 0x1;

// Write the phrase index to the reserved area once field

NVM FCCOB = 0 \times 0001; // 2^{nd} phrases

// Write index to specify the word0 to be programmed

NVM FCCOBIX = 0x2;

// Write the word 0

NVM FCCOB = 0x7788;

\ensuremath{//} Write index to specify the word1 to be programmed

NVM FCCOBIX = 0x3;

// Write the word1

NVM FCCOB = 0 \times 5566;

// Write index to specify the word2 to be programmed

```

Transitioning Applications from S08AC and S08FL Family to S08PT Family, Rev. 0

```

NVM FCCOBIX = 0x4;

// Write the word 2

NVM FCCOB = 0x3344;

// Write index to specify the word3 to be programmed

NVM FCCOBIX = 0x5;

// Write the word 3

NVM FCCOB = 0 \times 1122;

// Launch the command

NVM FSTAT = 0x80;

// Wait till command is completed

While (!(NVM FSTAT & NVM FSTAT CCIF MASK));

/* Use Read Once command to read the just programmed once phrases

into global variables gwIFRPhrases[0] to gwIFRPhrases[4]

// Write index to specify the command code to be loaded

NVM FCCOBIX = 0x0;

// Write command code and memory address bits[17:16]

NVM FCCOBHI = 0x4;// read once command

// Write index to specify one of the 8 phrases in the reserved area once field

NVM FCCOBIX = 0x1;

// Write the phrase index to the reserved area once field

NVM FCCOB = 0 \times 0001; // 2^{nd} phrases

// Launch the command

NVM FSTAT = 0 \times 80;

// Wait till command is completed

While (!(NVM FSTAT & NVM FSTAT CCIF MASK));

// Write index to specify which word to read

NVM FCCOBIX = 0x2;

// Read the word0 from once field

gwIFRPhrases[0] = NVM FCCOB;

// Write index to specify which word to read

NVM FCCOBIX = 0x3;

// Read the word1 from once field

gwIFRPhrases[1] = NVM FCCOB;

// Write index to specify which word to read

NVM FCCOBIX = 0x4;

// Read the word2 from once field

gwIFRPhrases[2] = NVM FCCOB;

// Write index to specify which word to read

NVM FCCOBIX = 0x5;

// Read the word3 from once field

gwIFRPhrases[3] = NVM FCCOB;

```

# 1.2.4 User margin level

The user margin is a small delta to the normal read reference level. In effect it serves as a minimum safety margin. If the reads pass at the tighter tolerances of the user margins, then the normal reads have at least this much safety margin before a user will experience data loss. There are two user margin levels: user

Transitioning Applications from S08AC and S08FL Family to S08PT Family, Rev. 0

#### Flash and EEPROM

margin-1 level, and user margin-0 level. User margin-1 level is the read margin to the erased state, while user margin-0 level is the read margin to the programmed state.

Users can use the Set User Margin level command to set the related user margin for the future read operation from flash/EEPROM. If user margin-1 level is set, and the future flash/EEPROM read returns a single-bit value of zero, then the flash read robustness is not guaranteed. If user margin-0 level is set, and the future flash/EEPROM read returns a bit of 1, then the flash read robustness is also not guaranteed.

This feature helps to ensure flash memory read robustness, and users can take the necessary action for safety purposes.

The NVM\_FCCOBLO[7] bit is used to select between flash memory and EEPROM memory to be applied with the set user margin level:

- 0—flash memory to be applied

- 1—EEPROM memory to be applied

The following code snippet shows how to set the user margin-0 level for the EEPROM block at a specified address:

```

/*

Set user margin-0 level for the future flash operations

// Write index to specify the command code to be loaded

NVM FCCOBIX = 0 \times 0;

// Write command code and memory address bits[17:16]

NVM FCCOBHI = 0x0D;// set user margin level command

NVM FCCOBLO = 0x80;// Bit 7 =1 selects EEPROM memory

// Write index to specify EEPROM address

NVM FCCOBIX = 0x1;

// Write the EEPROM address

NVM FCCOB = 0x3100;//

// Write index to specify user margin level

NVM FCCOBIX = 0x2;

// Write the user margin-0 level

NVM FCCOB = 0 \times 0002;//

// Launch the command

NVM FSTAT = 0x80;

// Wait till command is completed

While (! (NVM FSTAT & NVM FSTAT CCIF MASK));

```

# 1.3 ECC parity check

EEPROM supports ECC parity check. It supports single fault bit and double fault bit detection and also single fault bit resolve. This feature provides an additional safety mechanism for the system.

Both errors are reflected in the NVM\_FERSTAT register. NVM\_FERSTAT[DFDIF] indicates that a double fault bit error has occurred, while NVM\_FERSTAT[SFDIF] indicates a single fault bit error that occurs if NVM\_FCNFG[IGNSF] is cleared.

Both ECC errors can generate the corresponding interrupt if the corresponding bit in NVM\_FERCNFG register is set.

Transitioning Applications from S08AC and S08FL Family to S08PT Family, Rev. 0

There is a one-cycle delay in storing the ECC DFDIF] and SFDIF fault flags in NVM\_FERSTAT register. At least one clock cycle is required after a flash memory read before checking NVM\_FERSTAT for the occurrence of ECC errors.

# 2 Clock gating

The S08PT family includes a clock gating system to manage the bus clock sources to the individual peripherals. Using this system, the user can enable or disable the bus clock to each of the peripherals at the clock source, eliminating unnecessary clocks to peripherals which are not in use and thereby reducing the MCU's overall run and wait mode currents.

Out of reset, all peripheral clocks will be enabled. For lowest possible run wait currents, user software should disable the clock source to any peripheral not in use. The actual clock will be enabled or disabled immediately following the write to the Clock Gating Control registers (SCG Cx).

In stop modes, the bus clock is disabled for all gated peripherals, regardless of the setting in the SCG\_Cx registers.

The following code snippet is used to gate off the clock to TSI:

# 3 Interrupt Priority Controller

The Interrupt Priority Controller (IPC) is the same as in the S08FL family, but the S08AC family does not have it.

The IPC has these features:

- Four-level programmable interrupt priority for each interrupt source

- Support for prioritized preemptive interrupt service routines

- Lower priority interrupt requests are blocked when higher priority interrupts are being serviced

- Higher or equal priority level interrupt requests can preempt lower priority interrupts being serviced

- Automatic update of interrupt priority mask with the priority level of the interrupt source currently being serviced when the interrupt vector is being fetched

- Interrupt priority mask can be modified during main flow or interrupt service execution

- Previous interrupt mask level is automatically stored when interrupt vector is fetched (four levels of previous values accommodated)

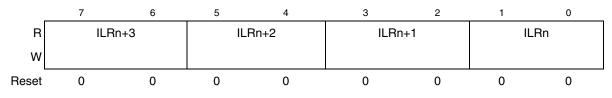

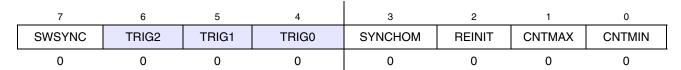

The interrupt priority level is programmable in the IPC\_ILRSx register as below:

Figure 2. IPC ILRSx register

Transitioning Applications from S08AC and S08FL Family to S08PT Family, Rev. 0

#### **Interrupt Priority Controller**

- ILRn bits corresponds to vector number <n>. To get the correct IPC\_ILRSx register, divide the vector number <n> by 4 and the result quotient is <x>, that is, x = vector number <n>/4.

- Each interrupt priority level is a 2-bit value such that a user can program the interrupt priority level of each interrupt source to priority 0,1, 2, or 3.

- Level 3 has the highest priority while level 0 has the lowest.

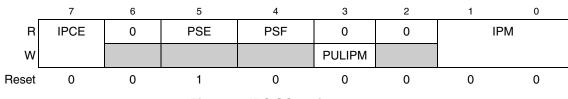

The current interrupt priority mask (IPM) defined in IPC\_SC register controls which interrupt is allowed to be presented to the HCS08 CPU. During vector fetch, the interrupt priority mask is updated automatically with the value of the ILR corresponding to that interrupt source.

Figure 3. IPC SC register

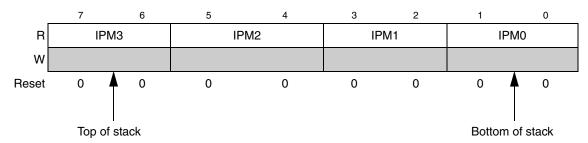

The original value of the IPM will be saved to the Interrupt Priority Mask Pseudo Stack (IPC\_IPMPS), which is a shift register for restoration after the interrupt service routine completes execution.

Figure 4. IPC IPM Pseudo Stack register

When the interrupt service routine completes execution, the user restores the original value of IPM by writing 1 to the IPC SC[PULIPM] bit.

When the IPM is updated, the original value is shifted into IPC\_IPMPS. The IPC\_IPMPS can store four levels of IPM. If the last position of IPC\_IPMPS is written to the area marked as "Top of stack" in Figure 4, the PSF flag is set and indicates that the IPC\_IPMPS is full. If all the values in the IPMPS were read, the PSE flag indicates that the IPC\_IPMPS is empty.

The interrupt priority arbitration scheme is:

- When the IPC is enabled by setting IPC\_SC[IPCE] bit, the active interrupt source's interrupt priority level (IPC\_ILRSx[ILRn]) is compared with the current interrupt priority mask (IPC\_SC[IPM]) (in stop3 mode, the IPC\_SC[IPM] = 0x00); otherwise, the interrupt request signal from the source is directly passed to the CPU.

- If the ILRn value ≥ IPC\_SC[IPM], the corresponding interrupt out (INTOUT) signal will be asserted and will signal an interrupt request to the HCS08 CPU.

- Because the IPC is an external module, the interrupt priority level programmed in the interrupt priority register IPC\_ILRm will not affect the inherent interrupt priority arbitration as defined by

Transitioning Applications from S08AC and S08FL Family to S08PT Family, Rev. 0

the HCS08 CPU. Therefore, if two (or more) interrupts are present in the HCS08 CPU at the same time, the inherent priority in HCS08 CPU will perform arbitration by the inherent interrupt priority.

To support nesting interrupt, there are some requirements on an interrupt service routine (ISR):

- A minimum overhead of six bus clock cycles is added inside an ISR to enable preemptive interrupts due to added CLI and BSET instructions.

- Because interrupts of the same priority level are allowed to pass from the IPC to the HCS08 CPU, the flag generating the interrupt should be cleared before doing CLI to enable preemptive interrupts.

- The IPM is automatically updated to the level the interrupt is servicing, and the original level is kept in IPC\_IPMPS. Watch out for the full (PSF) bit if nesting for more than four levels is expected.

- Before leaving the interrupt service routine the previous levels should be restored manually by setting the PULIPM bit. Watch out for the full (PSF) bit and empty (PSE) bit.

The following code snippet shows how to set up nesting interrupts:

```

/* Initializing interrupt priorities and IPC */

/* Configure RTC IPL to 2 */

IPC_ILRS8_ILR35 = 2;

/* Configure KBIO PTA2 IPL to the highest level 3 */

IPC_ILRS9_ILR37 = 3;

IPC_SC_IPM = 1;   /* set current IPM */

IPC_SC_IPCE = 1;   /* enable IPC */

/* Interrupt Serivce Routines (ISRs) */

interrupt VectorNumber_Vrtc void RTC_Isr(void)

{

/*clear RTC flag by writing 1*/

RTC_SC1 |= RTC_SC1_RTIF_MASK;

/* do most critical work which can not be interrupted by higher priority interrupt.

asm (CLI);   /* enable nesting interrupt */

```

# 4 S08 CPU V6

The S08PT family devices include an S08 CPU V6, which is the newest version of the S08 CPU. It has no 2× clock domain, but is still fully source - and object-code compatible with old versions of the S08 CPU.

The core clock and the system bus clock are the same. This greatly reduces the power consumption of the core by around 59% compared with the old HCS08 CPU, given the same performance.

In addition, S08 CPU V6 and V5 added two special instructions: CALL and RTC to support extended memory space exceeding 64 KB. This requires memory management unit (MMU) support. APPAGE register is used to manage 16 KB pages of memory which can be accessed by the CPU through a 16 KB window from 0x8000 through 0xBFFF. The MMU also includes a linear address pointer register and data access registers, so that the extended memory space operates as if it is a single linear block of memory.

CALL operates like the JSR instruction, except that CALL saves the current PPAGE value on the stack and provides a new PPAGE value for the destination. RTC works like the RTS instruction, except RTC restores the old PPAGE value in addition to the PC during the return from the called routine.

Transitioning Applications from S08AC and S08FL Family to S08PT Family, Rev. 0

#### Enhanced code debug

The S08PT family does not include MMU as the memory size is within 64 KB. As a result, both CALL and RTC instructions are of no use.

The S08FL family devices contain the S08 CPU V1. Most of the S08AC family devices like the MC9S08AC60 series include the S08 CPU V2. These devices have no CALL and RTC instructions. However, the MC9S08AC128 series devices include the S08 CPU V5, and the MMU is able to access the memory space exceeding 64 KB.

Table 9 shows the difference between these instructions among the different versions of the S08 CPUs:.

| Instruction | CPU V6 | CPU V5 | CPU V4/V3/V2/V1 | Description |

|-------------|--------|--------|-----------------|-------------|

| RTS         | 6      | 6      | 5               | Bus cycles  |

| STOP        | 3+     | 2+     | 2               | Bus cycles  |

| CALL        | 9      | 8      | N/A             | Bus cycles  |

| RTC         | 7      | 7      | N/A             | Bus cycles  |

Table 9. CPU comparison

# 5 Enhanced code debug

The S08PT family includes version three of the Debug Module (DBG V3). It implements an on-chip ICE (in-circuit emulation) system and allows non-intrusive debugging of application software by providing an on-chip trace buffer with flexible triggering capability. The trigger also can provide extended breakpoint capacity. The on-chip ICE system is optimized for the S08CPUV6 8-bit architecture and supports 2 MB of memory space.

The DBG V3 added the following enhanced features, compared with the old version:

- Support up to three hardware breakpoints (old version only supports two hardware breakpoints) by adding additional comparator (comparator C) logic

- End-trace until reset, which allows capturing change of flow (COF) information that caused reset event

- Begin-trace from reset, which enables capturing COF information as soon as reset occurs

- LOOP1 capture mode, which is efficient for tracing loop code

In the case of an end-trace to reset where DBGEN=1 and BEGIN=0, the bits in DBG A/B/C Comparator registers, FIFO registers, and Debug Count Status register, do not change after reset. The bits in Debug Trigger register do not change after reset. The Debug Status register ARMF bit gets cleared by reset but AF, BF, and CF do not change after reset. The ARM and BRKEN bits in the Debug Control register are cleared but other control bits do not change after reset. Those control and status bits unaffected by reset are overridden so a host development system can read out the results of the trace run after the MCU has been reset. This is different from a POR reset which will reset those registers to default reset values. The end-trace until reset is an important feature which allows capturing trace information that caused the reset event.

In LOOP1 capture mode, the comparator C is managed by logic in the DBG module to track the address of the most recent change-of-flow event that was captured in the FIFO buffer. And in this case, the comparator C is not available for use as a normal hardware breakpoint. Therefore the number of hardware

breakpoints is reduced to two in LOOP1 capture mode. If the values match, the capture is inhibited to prevent the FIFO from filling up with duplicate entries. If the values do not match, the COF event is captured into the FIFO and the Comparator C registers are updated to reflect the address of the captured COF event.

In addition to the above improved features in the debug module, the S08PT family also provides illegal address detect (ILAD) in addition to the illegal opcode detect (ILOP). This feature facilitates debugging the runaway code by capturing the errant addresses. When the MCU is reset by ILOP or ILAD, the address of the illegal opcode or illegal address is captured in the Illegal Address register. This is a 16-bit register consisting of SYS ILLAL and SYS ILLAH, which contain the LSB and MSB 8-bit of the address, respectively. There are two flags in the System Reset And Status register (SYS SRS)to indicate such sources of reset: ILOP and ILAD. By checking the above register bits, users can easily know whether runaway code is caused by an illegal address and/or illegal opcode.

#### **Pinout changes** 6

On the S08PT family, the 5 V pad and internal layout are both optimized for transient protection.

These pins are general-purpose, bidirectional I/O port pins.

- PTA7-0 (except PTA4)

- PTB7-0

- PTC7-0

- PTD7-0

- PTE7-0

- PTF7-0

- PTG3-0

- PTH7-6

- PTH2-0

These port pins also have selectable pullup devices when configured for input mode (except PTA4).

The pulling devices are disengaged when configured for output mode and are selectable on an individual basis.

PTA4 is an output-only port pin. The port does not have pulling devices. PTA3 and PTA2 provide true open drain when operated as output.

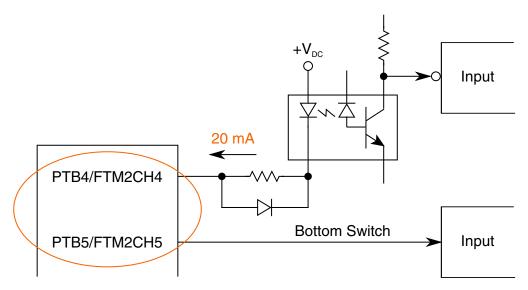

PTB4-5, PTD0-1, PTE0-1, and PTH0-1 support high current function (regardless of their pin functionality) when they are configured as output. When high current function is enabled, they can drive output current. Each high current drive pin can drive a 20 mA sink/source current. These pins can directly drive devices requiring high current such as optocouplers (see Figure below). All of the other pins can offer a single 5 mA sink/source current. Only one or two pins are allowed to sink and/or source current at a time.

Transitioning Applications from S08AC and S08FL Family to S08PT Family, Rev. 0 17 Freescale Semiconductor

Figure 5. Direct connection between high current drive pins and optocouplers

After reset, all pins are configured as parallel I/O pins with pullup disabled and are high-impedance (Hi-Z). If any pin is not used, it should be configured to output for maximum system robustness.

# 7 Parallel I/O structure

S08PT family devices have eight sets of I/O ports, which include up to 57 general-purpose I/O pins. The I/O ports have these features:

- Data direction control

- Internal pullup control

- Extreme high drive control

- Input filter control

When a peripheral module or system function is in control of a port pin, the data direction register bit still controls what is returned for reads of the port data register, even though the peripheral system has overriding control of the actual pin direction. This provides the ability to read the actual state of a pin when configured as output by a peripheral, with the steps given here.

S08PT family devices use the PTxIEn register bit to enable the corresponding pin as input, and the PTxOEn register bit to enable the corresponding pin as output.

Both S08AC and S08FL families use PTxDD registers to control the direction of the corresponding pins.

Below is the example code snippet to configure a PTA0 pin as input and to read the pin state on the S08PT family:

```

/* read pin state on PTAO pin */

PORT_PTAIE |= 1;/* configure pin as input */

PORT_PTAPE |= 1;/* enable pullup on this pin */

PinState = PORT PTAD & 1;

```

Transitioning Applications from S08AC and S08FL Family to S08PT Family, Rev. 0

PTA4 is an output-only port pin. The port does not have pullup or pulldown devices. PTA3 and PTA2 provide true open drain when operated as output. All other ports are bidirectional I/O port pins.

These port pins also have selectable pullup devices when configured for input mode. The pulling devices are disengaged when configured for output mode. The pulling devices are selectable on an individual port bit basis in the PORT\_PTxPE register. If the corresponding bit is set, the internal pullup is enabled; otherwise, it is disabled. For I<sup>2</sup>C applications, the internal pullup on both pins can be used to save power when SDA/SCL outputs are low.

Output extreme high drive can drive 20 mA sink/source current on the enabled pins, as described in Section 7, "Parallel I/O structure."

This feature can be enabled by setting the corresponding bit in the PORT HDRVE register for:

- PTH1

- PTH0

- PTE1

- PTE0

- PTD1

- PTD0

- PTB5

- PTB4

when they are operated as output. The extreme high drive strength is disabled if the pin is configured as an input. When configured as any shared peripheral function, the extreme high drive function strength still works on these pins, but only when they are configured as outputs.

This code shows how to enable extreme high drive on PTE1 pin:

```

/* Enabel extreme high drive on PTE1 pin */

PORT_PTEOE_PTEOE1 = 1;/* configure PTE1 pin as output pin */

PORT HDRIVE PTE1 = 1;/* enable extreme high drive on PTE1 pin */

```

A filter is implemented for each port pin set as digital input. It can be used as a simple low-pass filter and filters any glitch introduced from the pins of GPIO, IRQ, RESET, and KBI. The glitch width threshold can be adjusted easily by setting registers PORTP\_IOFLTn and PORTP\_FCLKDIV between 1–4096 bus clocks or 1–128 ms. This configurable glitch filter can take the place of all the other analog filters on board, and greatly improves the EMC performance on noise immunity.

# 8 Safety feature enhancements

Compared with the S08AC/FL families, the S08PT family has enhanced safety features in addition to the EEPROM ECC:

- Watchdog timer redesigned to be fully compatible with IEC60730 safety standard

- Programmable cyclic redundancy check (CRC) redesigned to support standard 16-bit and 32-bit CRC protocols for error detection

Transitioning Applications from S08AC and S08FL Family to S08PT Family, Rev. 0

#### Safety feature enhancements

# 8.1 Watchdog timer

The watchdog timer module (WDOG) is an independent timer that is available for system use. If it is not updated with a certain data write within a certain period, it will reset the MCU. It is used as a safety element to make certain the software is executing as planned and that the CPU is not stuck in an infinite loop or executing unintended code.

WDOG has the following features:

- Configurable independent clock source input from bus clock

- Internal 32 kHz RC oscillator

- Internal 1 kHz RC oscillator

- External clock source

- Programmable time-out period with 16-bit modulo value and optional fixed 256 clock prescaler

- Robust write sequence for counter refresh

- Refresh sequence of writing 0xA602 and then 0xB480 within 16 bus clock cycles

- Windowed refresh option

- Programmable 16-bit window value

- Provides robust check that program flow is faster than expected

- Refresh outside window leads to reset

- Programmable timeout post-processing

- Interrupt request to CPU with interrupt vector allowing ISR

- Force a reset after 128 bus clock cycles

- Robust write sequence for unlocking write-once control/configuration bits

- Unlock sequence of writing 0xC520 and then 0xD928 within 16 bus clock cycles for allowing updates to write-once control/configuration bits

- User need to update these after unlocking, within 128 bus clock cycles. Failure to update resets the system

- Configuration bits and registers are write-once-after-reset, to ensure watchdog configuration cannot be mistakenly altered (rewrite two preceding items for consistency)

- Flexible test mode enabling fast testing watchdog in the safety environment

- Backup reset to prevent hardware lockup condition driven by bus clock

S08AC/FL family COP watchdog configurations are listed in Table 10.

2<sup>18</sup> cycles

bus

1

1

| S08A    | С    | S08FL   |      | L                        |                | Watchdog               |                                                                                                                  |

|---------|------|---------|------|--------------------------|----------------|------------------------|------------------------------------------------------------------------------------------------------------------|

| COPCLKS | СОРТ | COPCLKS | СОРТ | COPW = 1<br>(COP Window) | Clock source   | overflow count         | Comments                                                                                                         |

| _       | _    | х       | 00   | x                        | х              | х                      | Watchdog disabled<br>for S08FL;<br>Watchdog disabled<br>by clearing<br>write-once bit<br>SOPT[COPE] for<br>S08AC |

| 0       | 0    | 0       | 01   | x                        | 1 KHz internal | 2 <sup>5</sup> cycles  |                                                                                                                  |

| 0       | 1    | 0       | 10   | х                        | 1 KHz internal | 2 <sup>8</sup> cycles  |                                                                                                                  |

| _       | _    | 0       | 11   | х                        | 1 KHz internal | 2 <sup>10</sup> cycles | Not applicable for S08AC                                                                                         |

| 1       | 0    | 1       | 01   | 6144 cycles              | Bus            | 2 <sup>13</sup> cycles |                                                                                                                  |

| _       |      | 1       | 10   | 49152 cycles             | Bus            | 2 <sup>16</sup> cycles | Not applicable for S08AC                                                                                         |

|         |      |         |      |                          |                |                        |                                                                                                                  |

Table 10. Watchdog configurations for S08AC/FL

For the watchdog clock source, the S08AC/FL families have two clock source options: internal 1 kHz low power oscillator, and bus clock. However, the S08PT family has additional two clock options: an internal 32 kHz RC oscillator (from ICSIRCLK), and external clock (from OSCOUT). The internal 1 kHz oscillator, 32 kHz oscillator, and external clock source allows an independent clock source from the bus clock for a robust application requirement.

196,608 cycles

11

On S08AC/FL families, resetting/clearing the watchdog counter is managed by writing 0x55 and 0xAA to the SRS register, in sequence. The S08FL family requires clearing the watchdog counter within the last 25% of the selected timeout period if the COP window is enabled.

Window mode allowsteh user to determine if the main loop is executing faster than expected. The S08AC family does not support watchdog window mode, while the S08FL and S08PT families support window mode.

The watchdog overflow count option is limited on both the S08AC and S08FL families, but the S08PT family has a programmable overflow count defined in a 16-bit timer register.

On the S08PT family, clearing the watchdog counter is conducted by writing 0xA602 and then 0xB480 to the WDOG\_CNT register in sequence within 16 bus clock cycles. If the window mode is enabled, the watchdog must be refreshed after the watchdog counter has reached the window value and before it has reached the overflow value. Any invalid watchdog refresh done before the watchdog counter has reached the window value or after it has reached the overflow value will assert a fault, resetting the CPU.

All three families support write-once protection. This means that once a write has occurred the watchdog control bits cannot be changed unless a reset occurs. This provides a robust mechanism to configure the watchdog and ensure that a runaway condition cannot mistakenly disable or modify the watchdog

#### Safety feature enhancements

configuration, once configured. However, only the S08PT family supports unlock write-once protection, which allows reconfiguring all watchdog control bits without a reset.

The S08PT family provides another enhanced safety feature: backup reset. If the clock source (except bus clock) is selected as the reference clock, the backup reset function takes effect. In this case, if the watchdog counter continuously overflows twice, the watchdog will generate a reset by force. This function can prevent the state machine and other logic driven by the bus clock from pausing illegally.

Table 11 shows the feature comparisons among the S08PT and S08AC/FL families.

| Features                          | S08PT                                                                | S08AC                                           | S08FL                                        |

|-----------------------------------|----------------------------------------------------------------------|-------------------------------------------------|----------------------------------------------|

| Independent clock source from bus | 1K Hz<br>32K Hz<br>External clock                                    | 1KHz                                            | 1KHz                                         |

| Overflow count                    | 16-bit programmable                                                  | Fixed                                           | Fixed                                        |

| Refresh sequence                  | Write 0xA602 to counter<br>WDOG_CNT, then<br>Write 0xB480 to counter | Write 0x55 to SRS,<br>then<br>Write 0xAA to SRS | Write 0x55 to SRS, then<br>Write 0xAA to SRS |

| Window mode                       | Supported                                                            | Unsupported                                     | Supported                                    |

| Write-once protection             | Yes                                                                  | Yes                                             | Yes                                          |

| Unlock write-once protection      | Supported                                                            | Unsupported                                     | Unsupported                                  |

| Test mode                         | Supported                                                            | Unsupported                                     | Unsupported                                  |

| Backup reset                      | Supported                                                            | Unsupported                                     | Unsupported                                  |

Table 11. Watchdog comparison

The following sections describe S08PT watchdog usage.

## 8.1.1 Clock source

WDOG CS2[WDOGC[1:0]] bits are used to select to one of four clock sources:

- · Bus clock

- 1 kHz internal low-power oscillator

- 32 kHz internal RC oscillator

- External clock

The WDO CS2[WDOGP] bit selects a fixed 256 prescaler for the clock source.

After reset, the watchdog is configured as 1 ms with internal 1 kHz clock source.

### 8.1.2 Window mode

WDOG CS1[WDOGW] is used to enable window mode.

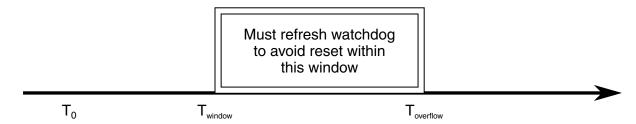

The starting point of the time window is  $T_{window}$ , and is defined by the WDOG\_WIN register. Assume  $T_0$  is the watchdog counter reset point or refreshing point, and  $T_{overflow}$  is the watchdog counter overflow

Transitioning Applications from S08AC and S08FL Family to S08PT Family, Rev. 0

point defined by watchdog timer register WDOG\_TMR. Figure 6 shows the time window within which the watchdog must be refreshed:

Figure 6. Watchdog window mode

## 8.1.3 Refreshing watchdog

Refreshing the watchdog is performed by this write sequence:

- 1. Write 0xA602 to WDOG CNT.

- 2. Write 0xB480 to WDOG CNT.

The second write must occur within 16 bus clock cycles after the first write happens.

## 8.1.4 Unlock write-once protection

All watchdog control bits, overflow value, and window value are write-once-after-reset. To update them, the unlock write-once protection mechanism must be used. To enable unlock write-once, WDOG\_CS1[WDOGA] must be cleared. The default value of WDOG\_CS1[WDOGA] is 0 after reset. If this bit is set, then all watchdog control bits are only write-once, which is similar to S08AC/FL families. In other words, once configured, the watchdog cannot be modified without forcing a reset.

The unlock write-once protection is performed with this unlock write sequence:

- 1. Write 0xC520 to WDOG CNT.

- 2. Write 0xD928 to WDOG CNT.

The second write must occur within 16 bus clock cycles after the first write happens.

Upon completion of the unlock write sequence, the watchdog write-once control bits should be reconfigured within 128 bus clock cycles. Otherwise a reset will occur.

### 8.1.5 Initialization

After reset, users can initialize the watchdog by performing these steps:

- 1. Write WDOG\_WIN register and WDOG\_TMR register to configure the window and overflow value first.

- 2. Write all other registers except the watchdog counter register WDOG\_CNT (CNTH:L) while ensuring WDOG\_CS1[WDOGA] = 0.

Transitioning Applications from S08AC and S08FL Family to S08PT Family, Rev. 0

#### Safety feature enhancements

The new configuration will take effect only after all registers except WDOG\_CNTH:WDOG\_CNTL are written once.

Please note that the above procedure must be completed before watchdog timeout occurs.

This code snippet shows how to perform watchdog initialization:

```

void wdog_user_mode(void)

{

/* Write all 6 8-bit registers or 2 16-bit registers plus 2 8-bit registers */

WDOG_TMR = 2000;/* 16-bit register, timeout at 2000 cycles */

WDOG_WIN = 1000;/* 16-bit register, window starts from 1000 cycles */

WDOG_CS1 = 0x88;/* watchdog enabled, WDOGA = 0, WDOGT=01 (application user mode) */

WDOG_CS2 = 0x83;/* window mode enabled, external clock source */

}

```

To disable the watchdog after reset, refer to this code snippet:

```

/* Write all 6 8-bit registers or 2 16-bit registers plus 2 8-bit registers */ WDOG_TMR = 2000;/* 16-bit register, timeout at 2000 cycles */ WDOG_WIN = 1000;/* 16-bit register, window starts from 1000 cycles */ WDOG_CS1 = 0;/* watchdog disabled, WDOGA = 0 */ WDOG_CS2 = 0x81;/* window mode enabled, 1K Hz clock source */

```

## 8.1.6 Test mode

Generally watchdog timeouts are set to around 100 ms or longer. The watchdog has a feature to test the watchdog more quickly and help minimize the delay time after reset to start application code execution.

To test the watchdog quickly, the counter can be split into two blocks: low 8-bit block and high 8-bit block. In this case, the watchdog counter functions as an 8-bit counter rather than 16-bit counter.

To enable test mode, WDOG\_CS1[WDOGT[1:0]] bits must be set to binary 10 or 11. These bits are cleared by a POR reset only and not affected by other resets.

Transitioning Applications from S08AC and S08FL Family to S08PT Family, Rev. 0

| WDOG_CS1<br>WDOGT[1:0] | Test Mode | Comments                                                                                                                                                                                    |

|------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00                     | disabled  | Reset only by POR                                                                                                                                                                           |

| 01                     | disabled  | Application user mode                                                                                                                                                                       |

| 10                     | enabled   | Test performed only on the lower 8-bit block (use only lower counter register and lower timer register):  • WDOG_CNTL is compared with WDOG_TMRL  • WDOG_CNTH and WDOG_TMRH are not used    |

| 11                     | enabled   | Test performed only on the higher 8-bit block (use only higher counter register and higher timer register):  • WDOG_CNTH is compared with WDOG_TMRH  • WDOG_CNTL and WDOG_TMRL are not used |

This code snippet shows how to do test mode after reset:

```

void wdog test mode low(void)

{

/* Write all 6 8-bit registers or 2 16-bit registers plus 2 8-bit registers */

WDOG TMR = 2000;/* 16-bit register, timeout at 2000 cycles */

WDOG WIN = 1000; /* 16-bit register, window starts from 1000 cycles */

WDOG CS1 = 0x90;/* watchdog enabled, WDOGA = 0, WDOGT=10 (lower 8-bit test mode)

* /

WDOG CS2 = 0x83; /* window mode enabled, external clock source */

void wdog test mode high (void)

/* Write all 6 8-bit registers or 2 16-bit registers plus 2 8-bit registers */

WDOG\_TMR = 2000;/* 16-bit register, timeout at 2000 cycles */

WDOG_WIN = 1000;/* 16-bit register, window starts from 1000 cycles */

WDOG CS1 = 0x98;/* watchdog enabled, WDOGA = 0, WDOGT=11 (higher 8-bit test mode)

* /

WDOG CS2 = 0x83;/* window mode enabled, external clock source */

}

startup code:

If ( SYS SRS POR )

/* POR reset, conduct watchdog low test mode */

wdog test mode low();

else If(SYS SRS WDOG ) /* watchdog reset occurs but not POR */

/* check watchdog test mode bits */

If( WDOG CS1 WDOGT == 3)

/* higher 8-bit test mode generated watchdog reset */

/* done test mode, and enable user mode */

```

Transitioning Applications from S08AC and S08FL Family to S08PT Family, Rev. 0

#### Safety feature enhancements

```

wdog_user_mode();

}

else if (WDOG_CS1_WDOGT == 2)

{

/* lower 8-bit test mode generated watchdog reset */

/* enter watchdog high test mode */

wdog_test_mode_high();

}

```

# 8.2 Cyclic redundancy check

The programmable cyclic redundancy check (CRC) generates 16/32-bit CRC code for error detection. The PCRC can be configured to work as any standard 16-bit or 32-bit CRC. It provides the user with programmable polynomial, seed value, and other parameters required to implement the required 16-bit or 32-bit CRC standard.

CRC also provides a feature to reverse input and output data by bit, and a feature to invert the final CRC result.

## 8.2.1 CRC initialization

To enable the CRC calculation, the user must program the SEED, POLYNOMIAL and necessary transpose type, and CRC result inversion parameters in their respective registers. Asserting the CRC\_CTL[WAS] bit (SEED bit), enables the programming of the SEED value into the CRC data registers. Re-asserting the SEED bit and programming a new or same seed value after a previously completed CRC calculation will re-initialize the CRC for a new CRC computation. All other parameters must be set before programming the seed value and subsequent data values.

## 8.2.2 16-bit CRC calculation

These steps show the process to compute a 16-bit CRC:

- 1. Clear the CRC CTRL[TCRC] bit to enable 16-bit CRC mode.

- 2. Program the transpose option bits (CRC\_CTRL[TOT] for data write/input, CRC\_CTRL[TOTR] for result read) and complement option bit (CRC\_CTRL[FXOR]) in the CRC\_CTRL register, as required for the CRC calculation.

- 3. Write 16-bit polynomial to CRC\_P2:CRC\_P3. CRC\_P1:CRC\_P0 are not usable in 16-bit CRC mode. CRC\_P2 is the high byte of the 16-bit polynomial, CRC\_P3 is the low byte.

- 4. Set SEED bit (CRC CTRL[WAS]) to program the seed value.

- 5. Write 16-bit seed to CRC\_D2:CRC\_D3. CRC\_D1:CRC\_D0 are not used. CRC\_D2 is the high byte of 16-bit seed, while CRC\_D3 is the low byte.

- 6. Clear SEED bit (CRC\_CTRL[WAS]) to start writing data values.

- 7. Write data values into CRC\_D3. CRC is computed on every data value write, and the intermediate CRC result is stored back into CRC\_D2:CRC\_D3.

- 8. When all values have been written, the final CRC result can be read out from CRC\_D2:CRC\_D3. CRC\_D2 is the high byte of the 16-bit CRC result, while CRC\_D3 is the low byte.

Transitioning Applications from S08AC and S08FL Family to S08PT Family, Rev. 0

9. Transpose and complement are performed dynamically while reading or writing values.

The next code snippet shows how to perform CCITT CRC-16:

```

CRC CTRL = 0;/* enable 16-bit CRC mode with no transpose */

CRC P2P3 = 0x1021;/* write 16-bit CCITT polynomial 0x1021 */

/* Standard CCITT polynomial of (x^16 + x^12 + x^5 + 1) */

CRC CTR WAS = 1;/* enable SEED write */

CRC D2D3 = 0xffff;/* write seed 0xffff */

CRC CTRL WAS = 0;/* disable SEED write, enable data write */

for (i = 0; i < 256; i++)

CRC D3 = 'A';/* Dummy 256 'A'*/

Checksum = CRC D2D3; /* read CRC result */

```

#### 8.2.3 32-bit CRC calculation

These steps show the process for computing a 32-bit CRC:

- 1. Set CRC CTRL[TCRC] bit to enable 32-bit CRC mode.

- 2. Program the transpose option bits (CRC CTRL[TOT] for data write/input, CRC CTRL[TOTR] for result read) and complement option bit (CRC CTRL[FXOR]) in the CRC CTRL register, as required for the CRC calculation.

- 3. Write 32-bit polynomial to CRC P0 to CRC P3. CRC P0 is the most significant byte (bit 31 to bit 24 of the 32-bit value) and CRC P3 is the least significant byte (bit 7 to bit 0 of the 32-bit value).

- 4. Set SEED bit (CRC CTRL[WAS]) to program the seed value.

- 5. Write 32-bit seed to CRC D0 to CRC D3. CRC D0 is the most significant byte (bit 31 to bit 24 of the 32-bit value) and the CRC D3 is the least significant byte (bit 7 to bit 0 of the 32-bit value).

- 6. Clear SEED bit (CRC CTRL[WAS]) to start writing data values.

- 7. Write data values into CRC D3. CRC is computed on every data value write and the intermediate CRC result is stored back into CRC D0 to CRC D3.

- 8. When all values have been written, the final CRC result can be read out from CRC D0 to CRC D3.

- 9. Transpose and complement are performed dynamically while reading or writing values.

#### 8.2.4 **Transpose feature**

Some protocols use little endian format for the data stream to calculate CRC. In such a case, this feature comes in quite handy when performing such flipping of bits. By default, the transpose feature is disabled. Data is transposed dynamically while being read or written.

This version of CRC only supports bit transpose in a byte (CRC CTRL[TOT]/CRC CTRL[TOTR] = 01). For the TOT or TOTR bits, 10 and 11 are not valid values and should not be used.

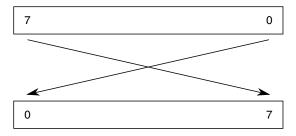

The following figure shows the bit transpose/reverse in a byte:

Transitioning Applications from S08AC and S08FL Family to S08PT Family, Rev. 0 Freescale Semiconductor 27

### Safety feature enhancements

Figure 7. CRC bit transpose

#### **Final XOR** 8.2.5

The CRC result complement function outputs the complement of the checksum value in CRC data registers every time the CRC data register is read out. When FXOR bit in CRCCTL register is set, the checksum is complemented. Otherwise, the raw checksum is accessed.

#### 8.2.6 Typical use cases

Table 13 lists some typical CRC standards and the corresponding settings:

|  | Table | e 13. CRC t | ypical use cases   |

|--|-------|-------------|--------------------|

|  |       | Fin al      | Turne of Transport |

| Name   | Poly           | Seed                                                      | Final<br>XOR? | Type of Transpose for Input   | Type of<br>Transpose for<br>CRC Read | Standards                            |

|--------|----------------|-----------------------------------------------------------|---------------|-------------------------------|--------------------------------------|--------------------------------------|

| CRC-16 | 0x1021         | 0xFFFF<br>(ITU-T V.41)<br>0x0000<br>(ITU-T T.30,<br>X.25) | No            | No transpose                  | No transpose                         | CRC-CCITT,<br>ADCCP,<br>SDLC/HDLC    |

| CRC-16 | 0x1021         | 0                                                         | No            | Transpose only bits in a byte | Transpose only bits in a byte        | CRC-CCITT<br>(Kermit)                |

| XMODEM | 0x8408         | 0x0000                                                    | No            | Transpose only bits in a byte | Transpose only bits in a byte        | XMODEM                               |

| ARC    | 0x8005         | 0x0000                                                    | No            | Transpose only bits in a byte | Transpose only bits in a byte        | ARC (zip file)                       |

| CRC-32 | 0x04C11DB<br>7 | 0xFFFFFFF                                                 | Yes           | Transpose only bits in a byte | Transpose both bits and bytes        | PKZIP, AUTODIN<br>II, Ethernet, FDDI |

# 9 FlexTimer versus TPM

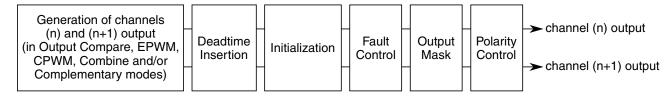

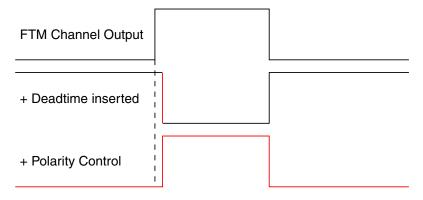

The FlexTimer module (FTM) on the S08PT family is designed based on the Timer/ PWM (TPM). It provides input capture, output compare, and generation of PWM signals. It is fully backward compatible with the TPM module used on the S08AC/FL families. It also provides these new enhanced features targeting motor control and power conversion applications:

- Complementary mode

- Combined mode, to generate asymmetric PWM

- Deadtime insertion hardware

- PWM synchronization control

- Fault control inputs

- Output masking

- Polarity control

- Enhanced triggering functionality

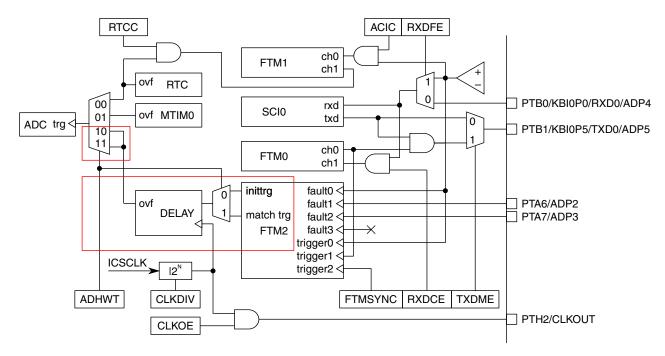

There are 3 FTMs on the S08PT family: FTM0, FTM1, and FTM2. Both FTM0 and FTM1 have two independent channels. FTM2 has six independent channels.

FTM register space is divided into two sets: one has fully TPM-compatible registers, and the other has FTM-specific registers.

Table 14 shows the FTM registers that are compatible with TPM.

Table 14. FlexTimer registers compatible with TPM

| Fle           | FlexTimer   |               | PWM (TPM)   |

|---------------|-------------|---------------|-------------|

| Register Name | Address     | Register Name | Address     |

| FTMx_SC       | Base + 0000 | TPMxSC        | Base + 0000 |

| FTMx_CNTH     | Base + 0001 | TPMxCNTH      | Base + 0001 |

| FTMx_CNTL     | Base + 0002 | TPMxCNTL      | Base + 0002 |

| FTMx_MODH     | Base + 0003 | TPMxMODH      | Base + 0003 |

| FTMx_MODL     | Base + 0004 | TPMxMODL      | Base + 0004 |

| FTMx_C0SC     | Base + 0005 | TPMxC0SC      | Base + 0005 |

| FTMx_C0VH     | Base + 0006 | TPMxC0VH      | Base + 0006 |

| FTMx_C0VL     | Base + 0007 | TPMxC0VL      | Base + 0007 |

| FTMx_C1SC     | Base + 0008 | TPMxC1SC      | Base + 0008 |

| FTMx_C1VH     | Base + 0009 | TPMxC1VH      | Base + 0009 |

| FTMx_C1VL     | Base + 000A | TPMxC1VL      | Base + 000A |

#### FlexTimer versus TPM

Table 14. FlexTimer registers compatible with TPM (continued)

| FlexTimer     |                       | Timer PWM (TPM) |             |  |

|---------------|-----------------------|-----------------|-------------|--|

| Register Name | Register Name Address |                 | Address     |  |

|               |                       |                 |             |  |

| FTMx_C5SC     | Base + 0014           | TPMxC5SC        | Base + 0014 |  |

| FTMx_C5VH     | Base + 0015           | TPMxC5VH        | Base + 0015 |  |

| FTMx_C5VL     | Base + 0016           | TPMxC5VL        | Base + 0016 |  |

For FTM0 and FTM1, the shaded areas in the above table are holes and are considered to be illegal when accessing them.

Table 15 shows the FTM-specific register map:

Table 15. FlexTimer-specific registers

| Register Name | Address     | Register Name  | Address     |

|---------------|-------------|----------------|-------------|

| FTMx_CNTINH   | Base + 0017 | Reserved       | Base + 0021 |

| FTMx_CNTINL   | Base + 0018 | FTMx_DEADTIME  | Base + 0022 |

| FTMx_STATUS   | Base + 0019 | FTMx_EXTTRIG   | Base + 0023 |

| FTMx_MODE     | Base + 001A | FTMx_POL       | Base + 0024 |

| FTMx_SYNC     | Base + 001B | FTMx_FMS       | Base + 0025 |

| FTMx_OUTINIT  | Base + 001C | FTMx_FILTER0   | Base + 0026 |

| FTMx_OUTMASK  | Base + 001D | FTMx_FILTER1   | Base + 0027 |

| FTMx_COMBINE0 | Base + 001E | FTMx_FLTFILTER | Base + 0028 |

| FTMx_COMBINE1 | Base + 001F | FTMx_FLTCTRL   | Base + 0029 |

| FTMx_COMBINE2 | Base + 0020 |                |             |

## 9.1 FTM clock source

The FTM clock source can be the system clock divided by two or the system clock, depending on the FTMx\_MODE[FTMEN] bit, the fixed system clock, and the external clock. The fixed system clock is ICSFFCLK. The external clock must not exceed one-fourth (1/4) of the system clock.

Table 16 shows the clock source selection:

| FTMx_SC[CLKS] | FTMx_MODE[FTMEN] | FTM Clock Source                      |

|---------------|------------------|---------------------------------------|

| 00            | Х                | No Clock selected. FTM disabled       |

| 01            | 0                | System Clock divided by 2 (bus clock) |

|               | 1                | System Clock                          |

| 10            | Х                | Fixed System Clock                    |

| 11            | Х                | External Clock                        |

Table 16. FlexTimer-specific registers

# 9.2 TPM-compatible functions

To use TPM-compatible functions, make sure that FTMx\_MOD[FTMEN] is zero, and do not write to FTM-specific registers. Instead, write to TPM-compatible registers as is done on S08AC/FL families.

# 9.3 FTM-specific functions

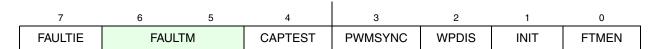

FTM provides specific functions which are enhanced features to TPM. Prior to accessing any FTM-specific function, FTMx\_MOD[FTMEM] must be set.

## 9.3.1 Combined mode

In combined mode, the channel (n) (an even channel) and channel (n+1) (the adjacent odd channel) are combined together as a PWM channel pair n. This is then used to create a single PWM signal which can be used for asymmetrical PWM/phase shift PWM. This feature is widely used in power conversion applications.

The FTMx\_COMBINEn register controls the PWM channel n and n+1 pair. In order for a PWM channel pair n to enter combined mode, these conditions must be met:

- FTMx\_MODE[FTMEN] = 1

- FTMx\_COMBINEn[COMBINE] = 1

- $FTMx\_COMBINEn[DECAPEN] = 0$

- $FTMx\_SC[CPWMS] = 0$

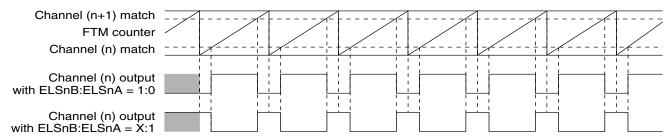

FTMx\_CnSC[ELSB:ELSA] controls when channel *n* outputs high:

- = 10, when channel n matches

- = 1X, when channel n+1 matches

Figure 8 shows the channel *n* output in combined mode:

#### FlexTimer versus TPM

Figure 8. Program flash example

The PWM period is  $FTMx\_MODH:L - FTMx\_CNTINH:L + 1$ , and the PWM pulse width is  $FTMx\_C(n+1)VH:L - FTMx\_C(n)VH:L$ .

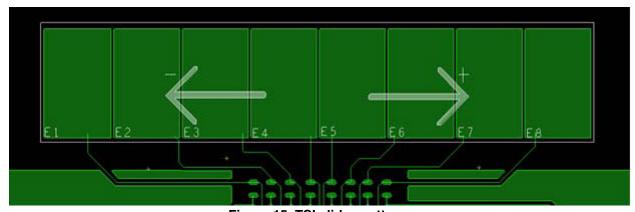

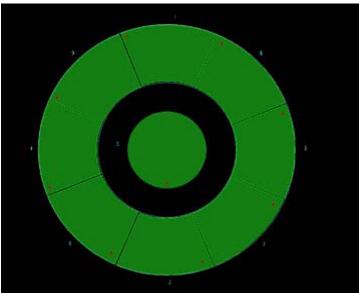

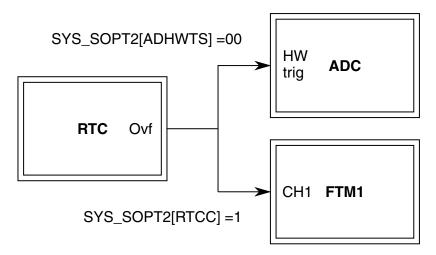

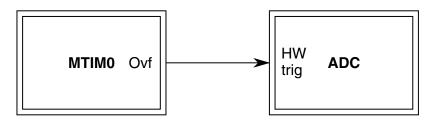

A channel *n* interrupt occurs when FTMx\_CNT = FTMx\_CnVH:L, and a channel n+1 interrupt occurs when FTMx CNT = FTMx C(n+1)VH:L.