#### Freescale Semiconductor

**Order this document** by AN1783/D

**AN1783**

# **Determining MCU Oscillator Start-up Parameters**

By Stuart Robb & David Brook, East Kilbride, Scotland Andreas Rusznyak, Geneva, Switzerland

Rev 1.0, December 1998

#### Introduction

Many microcontrollers (MCUs) incorporate an inverting amplifier for use with an external crystal or ceramic resonator in a Pierce oscillator configuration. This paper describes how to calculate the minimum gain (transconductance) of the amplifier required to ensure oscillation with specific external components, and also how to measure the amplifier transconductance to establish whether the minimum gain requirement is met.

#### **Oscillator Circuit**

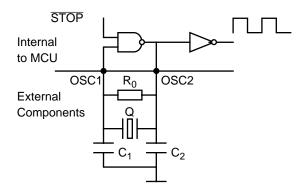

Figure 1 Standard Pierce Oscillator for > 1MHz Operation

Figure 1 shows the standard Pierce oscillator configuration typically used on MCUs for frequencies in the range 1MHz to 20MHz. The oscillator pins are labelled OSC1, OSC2 on the MC68HC05 and

Oscillator Circuit

MC68HC08 families of MCUs and EXTAL, XTAL, respectively, on the MC68HC11 and MC68HC12 families. On some MCUs (e.g. the MC68HC05B and MC68HC05X families), the resistor R<sub>0</sub> is integrated on-chip, in which case the external resistor is not required. This circuit is not applicable to some members of the MC68HC12 family of MCUs which employ a low power oscillator, e.g. MC68HC12D60.

#### **Internal Circuit**

The circuit internal to the MCU is shown in simplified form as a NAND gate followed by an inverter. The NAND gate has two inputs; one is connected to the MCU pin called OSC1 and the other input is connected to the inverted internal STOP signal. There are two conditions under which the oscillator is required to start oscillating; one is when power is applied to the MCU (called power-on reset) and the other is when the STOP signal is de-asserted. Following a power-on reset, the oscillation will start as soon as the MCU supply voltage,  $V_{DD}$ , has reached a level where the oscillator loop gain is greater than unity. For reliable operation, the oscillator must be oscillating by the time  $V_{DD}$  has reached the minimum specified operating value.

Most MCUs have a low power STOP mode. STOP mode is entered when the software executes the STOP command and as a result the STOP signal is asserted to stop the oscillator. The MCU is no longer clocked and the only current consumed by the MCU is due to 'leakage'. An external interrupt or a reset can release the STOP signal and allow the oscillator to re-start. The remainder of this paper will ignore the STOP input and treat the NAND gate as a simple inverter.

The output signal at the pin OSC2 is typically a distorted sine wave whose amplitude may even exceed the supply rail voltages. The following inverter provides additional voltage gain to produce an approximately square wave signal which in turn drives the internal clock generation circuitry.

#### **External Circuit**

In current designs the p-channel and the n-channel transistors in the inverter contribute approximately equally to the total gain provided that  $\text{Vin} \approx \text{Vout} \approx \text{V}_{DD}/2$ . Resistor  $R_0$  ensures that this optimal condition is met at oscillation start-up. For the circuit to oscillate, there must be positive feedback and the closed loop gain must be greater than unity. Resistor  $R_0$  results in negative feedback which increases the open loop gain requirement of the amplifier.  $R_0$  is usually made as large as possible to minimise the feedback whilst still overcoming leakage currents at start-up. For operation between 1MHz and 20MHz a value in the range of  $1\text{M}\Omega$  -  $10\text{M}\Omega$  is typically used.

In humid or dirty environments it is good practice to lacquer the oscillator components and tracks after they have been cleaned to prevent leakage

#### **Application Note**

currents due to condensation or dirt accumulating on the printed circuit board (PCB). Care should be taken when laying out the components on the PCB. The components should be positioned as close as possible to the MCU and the traces should be kept as short as possible. All other traces should be kept as far away as possible to avoid coupling. It is often worthwhile surrounding the components with a shield trace connected to ground (be careful not to create any loops) or a ground plane. The IC designer should ensure that the input pin OSC1 and preferably also the output pin OSC2 are placed between 'quiet' pins carrying DC signals. If a ceramic resonator is used with capacitors  $C_1$ ,  $C_2$  integrated into a common package, the manufacturer may recommend an optimal value of  $R_0$ .

The resonator Q, and capacitors  $C_1$  and  $C_2$  form the resonant circuit.  $C_1$  and  $C_2$  represent the external capacitors and any stray capacitance in parallel. The stray capacitance should be measured or estimated and included in the values used for  $C_1$  and  $C_2$  in Equations 1 to 7.

$$- \Box = - \Box = - \Box$$

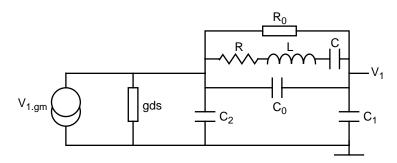

Figure 2 Crystal Equivalent Circuit

A crystal or ceramic resonator has the small signal equivalent circuit shown in Figure 2. R is called the 'series resistance', L and C are called the motional or series inductance and capacitance, respectively.  $C_0$  is the shunt capacitance, it represents the sum of the low-frequency parallel plate capacitance of the resonator and the stray capacitance of the crystal holder. In Equations 1 to 7 any additional stray capacitance between the OSC1 and OSC2 pins should be included into this value.

Values for R, L, C and  $C_0$  for a particular crystal are specified on a data sheet usually available from the crystal manufacturer. In order to measure these values, the manufacturer must apply a signal to the crystal, i.e. the values are obtained at a particular level of power dissipation in the crystal. However, at the start-up of the oscillator, the only signal across the crystal is due to thermal (Johnson) noise so the power dissipation in the crystal is extremely low. It is known that the effective value of R may increase as the power dissipated in the crystal decreases to low levels. The maximum value of R is therefore estimated by the crystal manufacturer. It is this estimated maximum value which should be used in equations 1 to 7.

# Calculating the Minimum Required Transconductance

## **Calculating the Minimum Required Transconductance**

Figure 3 Simplified Oscillator Equivalent Circuit

Figure 3 shows a simplified small signal equivalent circuit to the oscillator.

The inverter is modelled as a current source with an output current equal to  $V_1$ .gm where  $V_1$  is the input voltage and gm is the transconductance of the inverter. gds is the total output conductance i.e. the sum of the output conductances of the p-channel and the n-channel transistors in the inverter at start-up. The components of the resonant circuit have been described above.

As developed in [1] the impedance at resonance of the circuit comprising of the resonator Q and capacitors  $C_1$ ,  $C_2$  is given by:

$$R_{PQ} = \frac{1}{(\omega C_t)^2 R}$$

(Eqn 1)

where  $\omega=2\pi f$ , f being the frequency of resonance.

$C_t$  represents the total capacitance in parallel with series components R, L and C of the resonator:

$$C_t = C_0 + \frac{C_1 C_2}{C_1 + C_2}$$

(Eqn 2)

The frequency of oscillation is given to a good approximation by

$$f = \frac{1}{2\pi} \sqrt{\frac{1}{L} \left[ \frac{1}{C} + \frac{1}{C_t} \right]}$$

(Eqn 3)

For quartz resonators the term C<sub>t</sub> can be neglected.

The minimum transconductance required of the inverter to sustain oscillation in this circuit is given approximately by:

$$gm_{min} \approx \frac{(C_1 + C_2)^2}{C_1 C_2} \left[ \frac{1}{R_{PO}} + \frac{1}{R_0} + gds \left[ \frac{C_1}{C_1 + C_2} \right]^2 \right]$$

(Eqn 4)

## **Application Note**

If gm >> gds, this can be simplified to:

$$gm_{min} \approx \frac{(C_1 + C_2)^2}{C_1 C_2} \left[ \frac{1}{R_{PQ}} + \frac{1}{R_0} \right]$$

(Eqn 5)

The validity of this simplification can be checked by measuring gds, as described later in this paper.

If  $R_0 \gg R_{PO}$ , equation 5 can further be reduced to:

$$gm_{min} \approx \frac{(C_1 + C_2)^2}{C_1 C_2} \left[ \frac{1}{R_{PQ}} \right]$$

(Eqn 6)

or, if

$$C_1 = C_2$$

, to

$$gm_{min} \approx \frac{4}{R_{PQ}} = 4R\omega^2 \left[ C_0 + \frac{C_1}{2} \right]^2$$

(Eqn 7)

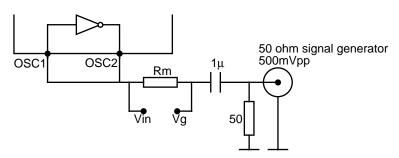

## **Measuring Amplifier Characteristics**

The recommended circuit for measuring the transconductance of the amplifier is shown in Figure 4 [2]. The circuit is simple to implement and should be powered up with the MCU reset pin held at 0V to ensure the amplifier stays active and the MCU does not execute any code. All unused inputs should be connected to 0V or V<sub>DD</sub> and not left floating. Note that the diagram correctly indicates that OSC1 and OSC2 are connected together. The transconductance does not vary significantly at frequencies below the oscillator's maximum design frequency. However, it is not recommended to measure the transconductance at the intended operating frequency, as the effects of stray capacitances will make the measurements inaccurate. A frequency in the range of 10kHz to 100kHz is recommended. A signal of around 500mVpp or less should be used with a 50 $\Omega$  terminating resistor and a 1µF coupling capacitor to ensure that the amplifier input and output remain in their linear region. It is essential that a high impedance measuring instrument, such as an oscilloscope with a low capacitance, high input resistance probe (<1pF,  $>10M\Omega$ ) is used to measure Vin and Vg with respect to ground. The value for the resistance  $R_m$  should be  $100\Omega$  to  $1k\Omega$ .

Figure 4 Measuring Amplifier Transconductance

AN1783 Rev. 1.0

Measuring Amplifier Characteristics

The transconductance of the amplifier depends on the process parameters and varies with supply voltage and temperature. Measurements should be taken on worst process parameter devices (if available) over the expected range of supply voltage and temperature. The worst case (lowest) figure can be expected at the combination of the minimum expected supply voltage and the highest expected operational temperature.

Based on the measurement results, the sum of the transconductance and of the output conductance is:

$$gm + gds = \frac{Vg - Vin}{Rm \times Vin}$$

(Eqn 8)

At this stage gds is unknown and a separate measurement must be made to determine it. If gds << gm then gds may be neglected. It may be noticed that this method of determining the available gm takes into account the reduction due to the additional n-channel transistor which exists in series with the inverter in the real NAND gate implementation.

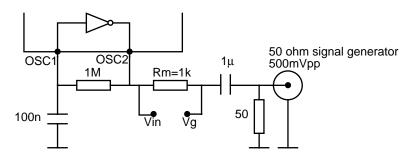

The recommended circuit for measuring the output conductance gds is shown in Figure 5. As with the measurement of transconductance, the MCU should be powered up but held in the reset state. A frequency in the range of 10kHz to 100kHz is recommended and again a high impedance measuring instrument is required.

Figure 5 Measuring Amplifier Output Conductance

To determine the available gain in the worst case the output conductance gds should be measured under the same conditions under which the minimum value of gm+gds has been determined. In the circuit of Figure 5 the AC signal at the input of the inverter is practically zero, which enables the output conductance to be measured:

$$gds = \frac{Vg - Vin}{Rm \times Vin}$$

(Eqn 9)

Now that gds is known, gm can be calculated by subtracting gds (eqn 9) from gm+gds (eqn 8). In addition, the validity of the simplification for Equation 4 can be checked.

## **Application Note**

The lowest value of gm found within the expected range of supply voltage and temperature is called the worst case value gm<sub>wcs.</sub>

The oscillation 'gain margin' can now be evaluated by calculating the ratio of worst case transconductance to the minimum required transconductance calculated from one of Equations 3 to 7.

$$gain margin = \frac{gm_{wcs}}{gm_{min}}$$

(Eqn 10)

The gain margin must be greater than unity for the oscillator to oscillate at all and as a general rule of thumb, a gain margin greater than 5 would be considered reasonable to ensure reliable start-up and operation.

If insufficient gain margin is found, the main options are:

- Reduce the size of capacitors C<sub>1</sub> and C<sub>2</sub> (shouldn't be less than 10pF),

- Use a different resonator with a lower series resistance.

In summary, four steps are required to check for reliable oscillator start-up:

- 1. Measure the worst case output conductance,

- 2. Measure the worst case transconductance,

- 3. Calculate the minimum required transconductance,

- 4. Calculate the gain margin.

## **Example**

The following measurements were made on a MCU with  $V_{DD}$  = 4.5V and T = 23°C.

Using the circuit of Figure 5, Vg = 0.496 Vpp, Vin = 0.478 Vpp From Equation 9

$$gds = \frac{0.496 - 0.478}{0.478 \times 1000} = 38 \times 10^{-6} AV^{-1}$$

Using the circuit of Figure 4, Vg = 0.488 Vpp, Vin = 0.448 Vpp From Equation 8

$$gm_{wcs} = \frac{0.488 - 0.448}{0.448 \times 100} - 38 \times 10^{-6} = 0.855 \times 10^{-3} AV^{-1}$$

The following data was obtained for a crystal:

f = 8MHz  $C_0 = 2.0pF$  C = 7.0fF  $R < 80\Omega$

2pF stray capacitance in parallel to the resonator will be assumed as well as a parallel resistance  $R_0$  of  $1M\Omega$  (on this MCU the parallel resistance is integrated on-chip).  $C_1 = C_2 = 15pF$  represent 12pF capacitors combined with 3pF stray capacitance for on-chip ESD structures, package capacitances and PCB traces. With these values the minimum transconductance calculated with Equation 4 is:

$$\begin{split} gm_{min} &= 4 \times \left\{ 80 \times \left[ 2\pi \times 8 \times 10^6 \times (4 \times 10^{-12} + 7.5 \times 10^{-12}) \right]^2 + 1 \times 10^{-6} + 38 \times 10^{-6} / 4 \right\} \\ &= 0.149 \times 10^{-3} \text{AV}^{-1} \\ \\ gain \ margin &= \frac{gm_{wcs}}{gm_{min}} = \frac{0.855 \times 10^{-3}}{0.149 \times 10^{-3}} = 5.7 \end{split}$$

This result indicates sufficient gain margin at 23°C, but it would be advisable to measure the transconductance at the highest expected operating temperature and verify the gain margin.

#### References

- A.Rusznyak: Start-Up Time of CMOS Oscillators (IEEE Trans. On Circuits and Systems, Vol 34, No 3, March 1987, pp 259...268).

- 2. P.Renard: Problem of MCU Oscillator Start-Up (Motorola Internal Report, System Eng. Group Geneva, Oct. 24, 1996).

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.